短截线是高速 PCB 设计中的一个重要主题,长期以来一直有一条指导原则,即应始终从高速数字互连的所有过孔中移除短截线。虽然短截线对高速线路不利,但并不总是需要移除。更重要的是预测损耗曲线和频率,并进行适当的布局规划,以尽量避免此类损耗。

在本文中,我将使用 Altium Designer 中附带的示例 MiniPC 项目来查看高速 PCB 上 PCIe 布线的一些模拟结果。所讨论的模拟将涉及计算来自连接器的 PCIe 通道的 S 参数。查看这些模拟结果应该可以帮助不熟悉的设计师更好地从模拟角度了解通孔和连接器转换上的短截线如何影响信号完整性,这可以帮助您做出正确的组件选择、放置和布线选择。

存根和 PCIe 路由的潜在问题

在 PCIe 布线中,通道以差分对的形式布线,并带有交流耦合电容器。通常将这些差分对通过连接器布线以到达外围设备,例如扩展卡。在通过这些扩展槽连接器布线的过程中,线路上可能会有一些剩余的短截线,这可能会限制最大带宽。这可以在模拟中进行评估,以获得非常准确的结果并精确确定 PCIe 通道的确切带宽。

任何高速传输线上的短截线都可能产生损耗或反射,因为它们的作用类似于 PCIe 通道上的高频阻抗变压器。请阅读本文了解有关短截线分析的更多信息。

尽管建议限制 PCIe 通道上的短截线,但它们可能存在于用于路由到附加卡或模块的连接器上。例如,用于垂直安装的 PCIe 附加卡的边缘连接器可能是一个通孔组件,当在与连接器相同的层上路由时,这些短截线可能会限制可用的信号带宽。在相反的层上路由可能更可取,尤其是在考虑放置电容器时。

PCIe 通道中连接器短截线丢失的示例

由于已知当信号穿过过孔短截线时会发生干扰效应,并且需要电容器来消除 PCIe 通道上的直流偏移,因此值得研究过孔短截线在通过连接器布线时对损耗的影响程度。

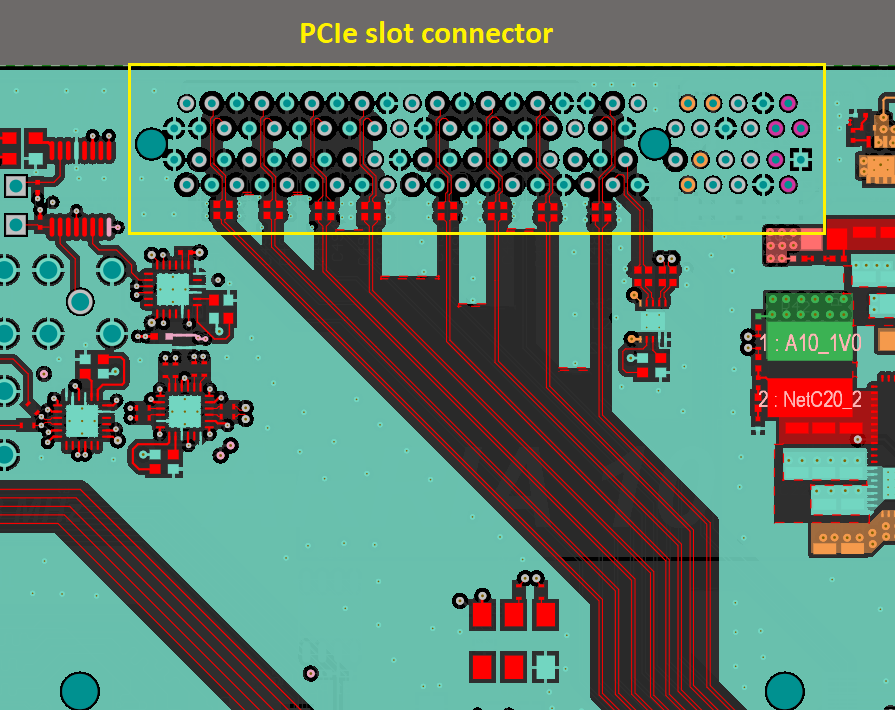

所讨论的 MiniPC 板使用带有 PCIe 接口的 Arria 10 FPGA,该接口路由至插槽连接器,如下所示。

PCIe 连接器,Tx 线上带有耦合帽,位于 98 针通孔连接器附近。

下面分析时我们需要了解的其他重要规格是板厚度和介电常数:

- 板厚 = 2.028 毫米

- 所有层的 Dk = 3.6

虽然该布局不是使用最新一代 PCIe 的 FPGA 创建的,但我们将通过与不同代 PCIe 的带宽要求进行比较来评估这些通道中的损耗。

初始模拟结果

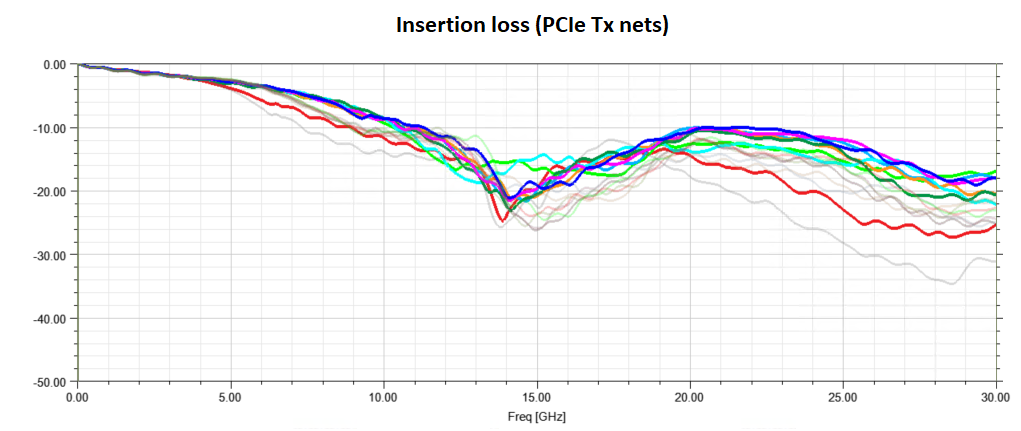

使用 Ansys SIwave 捕获了 Tx 网络的插入损耗模拟结果;这些结果如下所示。为了将电路板放入 Ansys SIwave,我们使用了 Altium Designer 中的 EDB Exporter 实用程序。在下面的结果中,我们看到 14-15 GHz 左右的下降低至 -25 dB,然后在较高频率下恢复到较低的损耗水平。

与 PCIe 插槽连接器相连的网络中的插入损耗 (S21)。

我们如何知道这种极端损失是由于存根造成的?仅仅看图表并不能证明问题是由存根引起的,但有两个很好的理由可以断定这可能是存根造成的:

- 如果您计算这些短截线中的第一个四分之一波长谐振,您会发现第一个下降预计在 13 GHz 左右。这与上面看到的 14-15 GHz 谐振非常接近。

- 14-15 GHz 左右的损耗曲线具有较窄的带宽,这正是中等 Q 值谐振器中的相消干涉所期望的结果。

- 所有曲线均有插入损耗图的典型形状,呈现出短截线行为,并且所有正在考虑的网络在 PCB 布局中都有短截线。

此图中的下降将数据传输速率限制为与约 8 GHz 的奈奎斯特频率相对应的任何值(或 2 级/NRZ 信号的 16 Gbps)。这对于 PCIe Gen4 来说没问题,但对于 Gen5 则不行。如果我们想完全消除这种损失或将此设计重新用于 Gen5 接口,则需要修改布局。

进一步调查和变更

更改布局的一些选项包括:

- 通过通孔将连接器引脚布线至后层上的电容器:尽管存在一些额外的通孔转换,但连接会脱离后层并通过通孔进入电容器,从而无需背钻即可有效地消除短线。

- 用 SMD 等效物替换连接器:这将完全消除短线,而无需通过连接器引脚和通孔进行两层转换。这也是最简单的解决方案,因为它不需要任何组件交换,尽管它确实需要重新布线。

- 对所有残线进行反钻:这需要一些额外的成本,并且会留下少量的残线(通常约 10 mil),因此最好在残线很长时使用。

如果布局已经完成,#1 和 #2 通常是最佳选择,因为它们可能需要的返工量最少,尽管 #2 将取决于较低层的内容。对于选项 #1,以下是带有 SMD 安装的示例连接器。如果您愿意在制造过程中支付控制深度钻孔的成本,则 #3 是合适的。

人们可能会认为这种行为(在特定频率附近观察到高损耗或高反射等信号完整性问题)可能来自在激励时产生强烈共振的短截线。要评估为什么这种情况可能发生在差分通道中,需要计算过孔短截线结构中的结构共振集。

1235

1235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?