如何用Tessent对网表插入scan chain?

插入Scan Chain的步骤

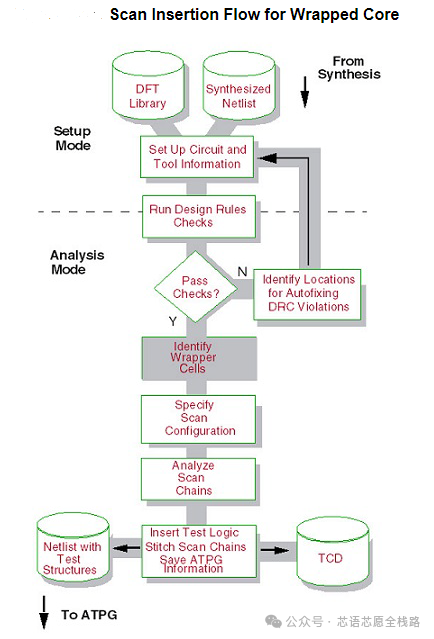

扫描链插入流程图:

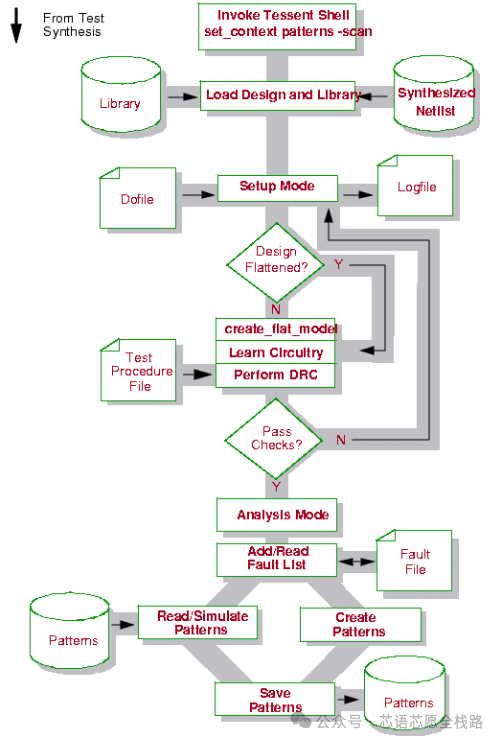

后续ATPG的流程图:

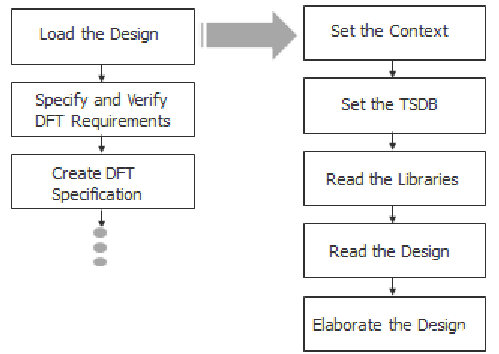

简单处理流程:

# SETUP# Set the context>set_context dft -scan# Read the verilog>read_verilog ../design/cpu.v# Read the library>read_cell_library ../library/adk.tcelllib>read_cell_library ../library/ram.lib>set_current_design cpu# Add clocks in the design>add_clock 0 clk1>add_clock 0 clk2>add_clock 0 clk3>add_clock 0 clk4>add_clock 0 ramclk//RUN DRC>set_system_mode analysis>report_drc_rules# Specify constraints to stitch up scan chains>set_scan_insertion_options -chain_count 100>analyze_scan_chains>report_scan_chains>insert_test_logic -write_in_tsdb On>report_scan_chains

再举一个完整例子说明

假设我们有一个门级网表文件cpu_top_synthesized.vg,并且我们想要为这个设计设置DFT上下文以进行扫描链插入。以下是具体的命令示例:

# 设置DFT上下文为扫描测试,并指定设计ID为gate3set_context dft -scan -design_id gate3# 读取单元库read_cell_library ../library/tessent/adk.tcelllib# 设置DFT上下文为扫描测试,并指定设计ID(这里假设为gate,但根据您的脚本可能是gateread_cell_library的一个误写)set_context dft -scan -design_id gate# 读取综合后的门级网表文件read_verilog ../Synthesis/cpu_top_synthesized.vg# 设置测试数据库输出目录set_tsdb_output_directory ../tsdb_gate# 设置当前设计(这里假设cpu_top是门级网表的名称)set_current_design cpu_top# 检查设计规则(这一步可能根据具体需求有所不同)check_design_rules# 找到EDT实例(这里假设已经有一个EDT实例存在)# 注意:这里的命令链可能需要根据实际设计进行调整set edt_instance [get_name_list [get_instance -of_module [get_name [get_icl_module -filter {tessent_instrument_type==mentor::edt}]]]]# 添加扫描模式(这里假设使用EDT作为扫描模式)add_scan_mode edt_mode -edt_instance $edt_instance# 分析扫描链analyze_scan_chains# 报告扫描链report_scan_chains# 插入测试逻辑insert_test_logic

1.前期准备

1)综合(Synthesis):在插入扫描链之前,需要先对设计进行综合,确保逻辑正确并实现优化。

2)明确DFT需求:确定每个模块(Core)的扫描链数量、Wrapper Cells(共享或专用包装单元)数量。

3)设置DFT上下文:使用如set_context dft -scan -design_id gate等命令,为扫描链插入设置正确的DFT(可测性设计)上下文。

设置DFT(可测性设计)上下文是扫描链插入等DFT操作的重要前提,如何设置DFT上下文呢?

首先,需要启动Tessent™ Shell工具,这是进行DFT相关操作的基础环境。

使用set_context命令:

在Tessent™ Shell中,使用set_context命令来设置DFT上下文。该命令指定了当前DFT操作的上下文环境,如扫描测试、边界扫描等。

指定设计ID:

在set_context命令中,需要指定一个唯一的设计ID(design ID)来标识当前的设计。对于门级网表,通常推荐使用gate或gate3作为设计ID(根据上下文描述,gate3可能更适用于门级网表,而gate可能用于更扁平的设计)。

# 设置DFT上下文为扫描测试,并指定设计ID为gate3set_context dft -scan -design_id gate3

在执行上述命令后,Tessent™ Shell将把当前上下文设置为扫描测试,并且所有后续的DFT操作都将针对设计ID为gate3的设计进行。

注意事项:

-

确保在设计流程的早期阶段就正确设置了DFT上下文,因为这将影响后续的所有DFT操作。

-

如果设计ID不是唯一的,可能会导致工具报错或覆盖之前的设计数据。

-

在设置DFT上下文之前,确保已经加载了正确的网表文件和其他必要的设计数据。

2.扫描配置

1)确定扫描链的数量。

根据测试时间、功耗和布线资源限制,确定设计所需的扫描链数量。

set_scan_insertion_options -chain_count 100add_scan_mode single_mode -chain_count 4

2)指定扫描单元的类型。

扫描单元是集成在扫描链中的特殊触发器,用于在测试模式下捕获和移出数据。不同类型的扫描单元可能具有不同的功能和性能特点。

3)排除不需要进行扫描替换的存储元件。

在某些情况下,某些存储元件(如特定的寄存器或存储器)可能不需要被替换为扫描单元。这可能是因为它们用于特定的功能(如复位逻辑或状态机),或者因为它们已经包含了内置的测试功能。

4)规划扫描单元在扫描链内的布置方式。

扫描单元在扫描链内的布置方式对于测试质量和测试时间都有重要影响。通常,我们希望将相关的扫描单元放置在同一个扫描链中,以减少测试数据的移动和存储开销。

扫描链配置:

-

set_scan_mode

-

create_scan_chain_family

> analyze_wrapper_cells> create_scan_chain_family ext_chains \-si_port_format { ext_si[%d]} \-so_port_format { ext_so[%d]} \-include_elements [get_scan_elements -class wrapper]

-

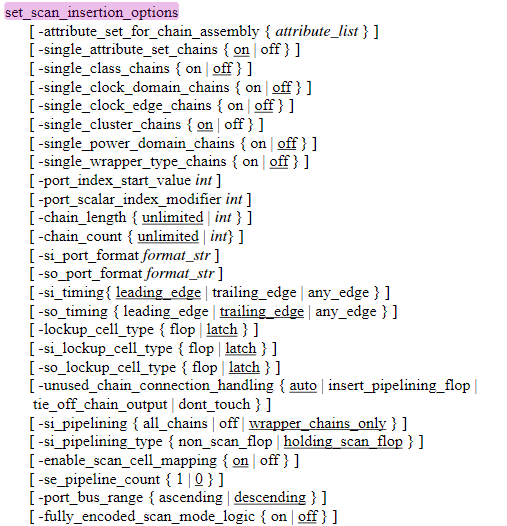

set_scan_insertion_options,三个命令都可以进行配置,具体配置options如下图所示

single_clock_edge_chains on/off 是否允许相同时钟沿触发器串在一条链上

single_clock_domain_chains on/off 是否允许相同时钟串在一条扫描链上

chain_length 链长

chain_count 链数

-

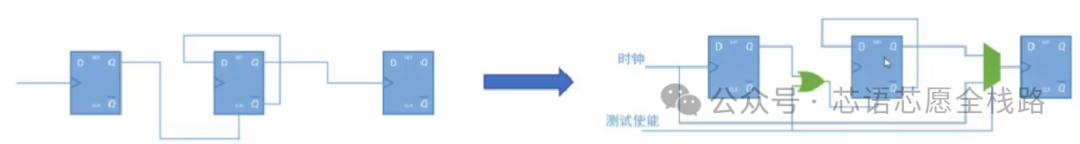

insert_test_logic:插入指定数量、长度的扫描链,插入测试逻辑(受set_test_logic选项控制)。如下如所示,左图在第一个寄存器移位操作时,中间寄存器复位状态不定不可控,第三个寄存器时钟端又受到第二个寄存器影响分频电路,第二个寄存器在移位时第三个时钟不可控,通过insert和set这两个命令工具会自动修正上述问题。或门可以在测试使能时会屏蔽来自Q端的信号,第三个寄存器在测试时使用原本的时钟而不是来自Q端的数据。

3.扫描替换

将原始存储单元(如普通寄存器)替换为扫描单元(如扫描触发器scan flip-flop)。这些扫描单元具有额外的测试引脚,如scan_in(扫描输入)、scan_enable(扫描使能)和scan_out(扫描输出)。

没有直接展示扫描替换的命令,但Tessent工具在后续步骤中会根据这些输入信息自动进行扫描替换,并生成扫描链。在这个过程中,Tessent工具会识别出设计中的哪些单元需要被替换为扫描单元,并自动完成替换工作。同时,它还会根据设计需求和扫描测试策略,将替换后的单元连接成合适的扫描链。

# Scan insertion stepanalyze_wrapper_cellsadd_scan_mode int_edt_mode -edt_instances c1_rtl3_tessent_edt_c1_int_instadd_scan_mode ext_edt_mode -edt_instances c1_rtl3_tessent_edt_c1_ext_instanalyze_scan_chainsinsert_test_logic# Scan mode verification and scan graybox generation stepset_context patterns -scan

4.扫描连接

将所有扫描单元按照一定顺序连接起来,形成扫描链。这通常涉及将每个扫描单元的scan_out连接到下一个扫描单元的scan_in,以及将扫描链的起始scan_in和结束scan_out连接到适当的测试端口。

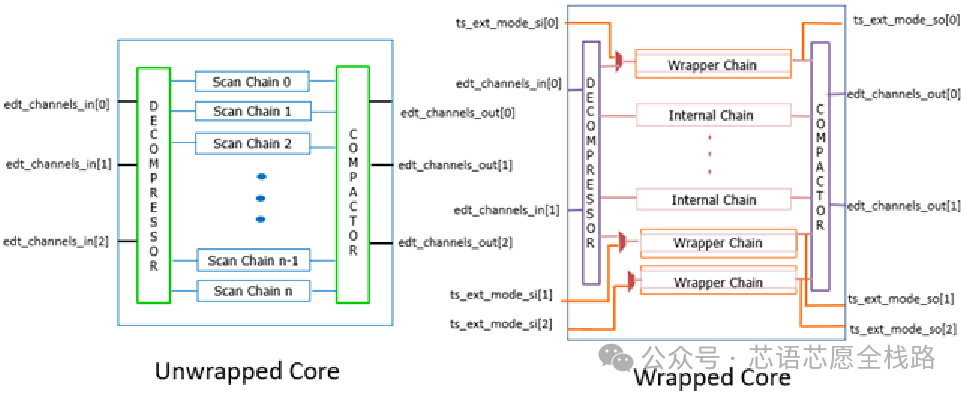

1)自动处理混合链:Tessent会自动将扫描链(Scan Chains)和包装链(Wrapper Chains)拼接成混合链,以减少扫描通道(Scan Channels)数量。

2)信号控制:使用以下信号控制扫描单元:

int_ltest_en(内部测试使能)

ext_ltest_en(外部测试使能)

scan_enable(扫描模式切换)

add_dft_signals int_ltest_en ext_ltest_en int_mode ext_mode5.生成测试硬件与模式

根据扫描链的配置,生成用于测试的硬件结构(如EDT、Hybrid TK/LBIST等)。

提取ICL(仪器连接语言)模块描述,用于描述测试仪器与待测设备之间的连接。

生成ICL测试模式并运行仿真,以验证扫描链的正确性和测试覆盖率。

extract_icl -write_in_tsdb on

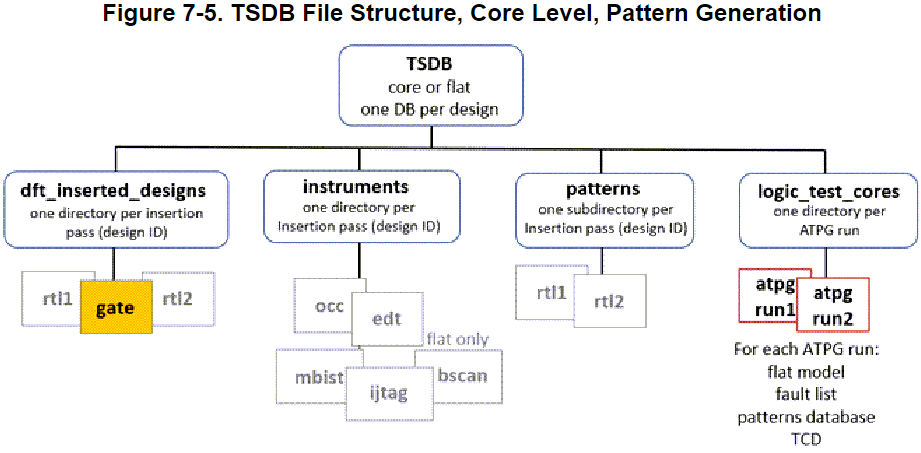

6.后续处理

在完成扫描链插入后,可能还需要进行扫描链重组(Scan Reorder)等后续处理,以优化扫描链的布局布线并减少走线长度。

生成相关的测试报告和.def文件,供后端工程师进行进一步的处理和分析。

-

insert_test_logic -write_in_tsdb on(默认将网表信息和配置信息保存到tsdb文件中,也可使用下面两个命令)

-

write_design -output_file abc_scan.v(保存带扫描链信息的网表)

-

write_atpg_setup abc(保存.defile&.testproc file,作为后续ATPG工作的输入)

注意事项

1)在插入扫描链时,需要充分考虑DFT团队提供的约束条件,如哪些寄存器不能做成SCAN FF、哪些Net要设成don’t_touch等。

2)扫描链的插入过程可能涉及复杂的脚本编写和命令执行顺序,因此要求工程师具备扎实的DFT知识和工具使用经验。

3)在完成扫描链插入后,需要进行充分的验证和测试,以确保扫描链的正确性和测试覆盖率满足设计要求。

对网表插入scan chain是一个复杂而精细的过程,需要工程师具备丰富的经验和专业知识。

503

503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?