本文介绍了综合属性MAX_FANOUT对Schematic的影响,通过本文可以理解通过寄存器复制的方式可以降低扇出。

高扇出信号可能会因为布线拥塞而出现时序问题。常用的规避方法是通过寄存器复制的方式降低扇出,可通过MAX_FANOUT实现寄存器复制。

MAX_FANOUT既可用于RTL代码中,也可以用于XDC中。

比如:

RTL代码:(*MAX_FANOUT = 50 *) reg rx_ce;

XDC: set_property MAX_FANOUT 50 [get_cells rx_ce_reg]或

set_property MAX_FANOUT 50 [get_nets {rx_ce}]

其中,rx_ce_reg表示要降低扇出的寄存器。

通常,寄存器复制后的寄存器名字最后都带有字符串rep,这一特性可帮助查找已复制的寄存器。

MAX_FANOUT起作用的条件

- 打算降低扇出的网络必须是reg寄存器驱动的。因为降低扇出的原理就是当reg驱动超过N时,就复制一个同样的reg驱动其他网络。

- -flatten_hierarchy不能设置为none。

- 如果需要优化的信号在IP核内部,那么在布局完成后使用命令:phys_opt_design -force_replication_on_nets [get_nets net_name]来保证IP核取消对内部网络的保护。

测试代码(RTL形式)

module top (

input clk_in,

input rst_n,

output reg [2:0] max_value

);

always@(posedge clk_in or negedge rst_n)

begin

if(!rst_n)

max_value <= 0;

else

max_value <= max_value + 1;

end

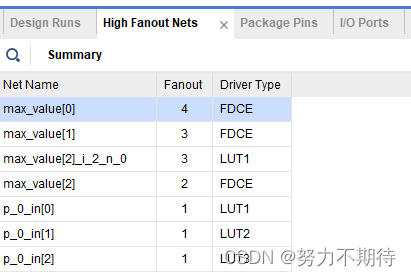

endmodule综合后的Schematic如下图,蓝色高亮表示max_value[0],扇出数是4:

扇出数如下图所示:

修改测试代码如下,设定了MAX_FANOUT=3:

module top (

input clk_in,

input rst_n,

(*MAX_FANOUT = 3 *) output reg [2:0] max_value

);

always@(posedge clk_in or negedge rst_n)

begin

if(!rst_n)

max_value <= 0;

else

max_value <= max_value + 1;

end

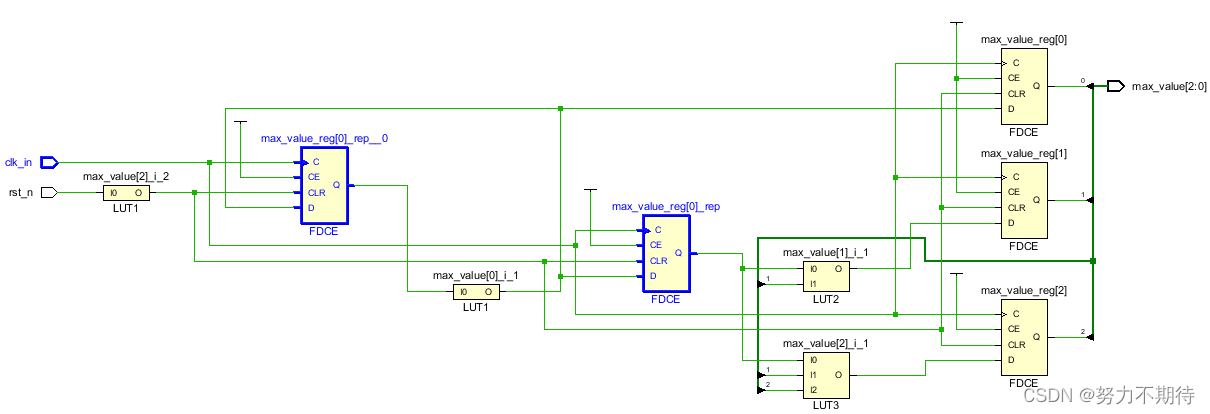

endmodule上面的代码限定了max_value的最大扇出数为3,综合后的原理图如下:

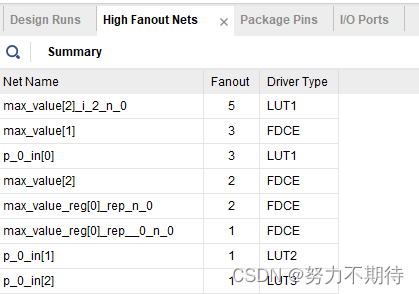

上图中蓝色高亮的部分就是通过寄存器max_value_reg[0]复制后得到的。通过执行Reports -> High Fanout Nets得到扇出数如下:

当在top.xdc中设置约束如下:

set_property MAX_FANOUT 3 [get_nets {max_value[0]}]

得到的原理图与上上图相同,如下。

当在top.xdc中设置约束如下:

set_property MAX_FANOUT 3 [get_cells max_value_reg[0]]

得到的原理图与上图相同,不再给图。

8877

8877

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?