💡 Note:

本文是根据AXI协议IHI0022F_b_amba_axi_protocol_spec.pdf(issue F)整理的。

主要是分享AXI3.0和4.0部分。

如果内容有问题请大家在评论区中指出,有补充或者疑问也可以发在评论区,互相学习🙌

Burst 传输

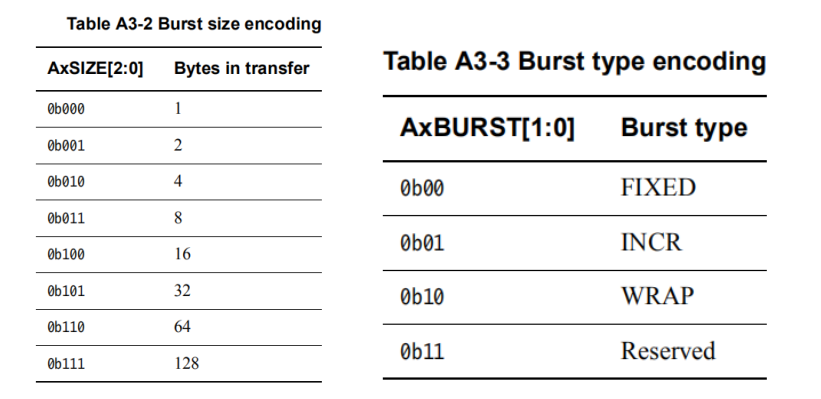

跟burst相关的信号有AxSIZE, AxLEN, AxBURST,编码如下:

AXI对burst传输方式的要求:

-

AXI3.0中incr burst的burst length最大为16,AxLEN为4bit信号;在AXI4.0中,incr burst的burst length为256,AxLEN为8bit信号。

-

对于其他类型的burst传输(fixed,wrap),burst length最大16.

-

AXI4.0(H suite)中说,对于非INCR burst,支持1-16 burst length,但后面又说wrap传输只支持2、4、8、16 burst length。

-

Burst length不能超过4KB边界。

-

Burst 传输不能被提前终止,即使发生了传输错误。在写中,发生错误,也还要将写传输周期完成,master可以将wtrb拉低。在读的时候,传输周期也要完成,但是master可以discard data。

对于device设备,读操作发生错误,会怎么样呢?Device memory一般是read-sensitive的,读了之后,device中的设备就被移除了,如果我们把数据discard,这些数据就丢失了。所以spec中建议:a Manager must use a burst length that exactly matches the size of the required data transfer.

-

在AXI4.0中,对于一个non-modifible的INCR burst,并且她的长度大于16,也可以把它转换成多个小的burst。虽然是non-modifiable,也可以改变,但只能改变Axlen和响应的地址,其他的控制信号不能改变。

-

要注意,AxBURST, AxLEN, AxSIZE这些信号,在Axvalid, Axready同时为高的那一个周期内被采样一次,而不是每次transfer都采样。RDATA/RRESP是每个transfer都会返回,而BRESP是一个burst只返回一次。

-

对于exclusive access ,还有一些特殊的要求,见exclusive 部分。

Wrap 操作

-

wrap的burst length为2、4、8、16,没有1.(如果是1的话,那么就是fixed address了)

-

Wrap的地址要跟transfer size对齐,比如地址位宽是64bit,transfer size是32bit,那么地址要跟0x4对齐,不能是0x1,0x2,0x3这种。

-

要知道Wrap boundary address是什么?Wrap boundary是小于等于传输的起始地址,它跟burst的byte size(burst length*transfer size)对齐。比如AxSIZE为2,也就是4个byte的transfer size,burst length为4,所以这个burst的transfer size 为0x10,如果传输是从0x14开始的,那么每次transfer的起始地址是0x14->0x18->0x1c->0x10,会返回到0x10,这个0x10就是wrap boundary address。(始终要记住,地址是跟transfer size对齐,也就是跟0x4对齐)

-

Wrap传输一般用在cache access中。

-

AxBURST[1:0]==0b10表示wrap传输

-

在非对齐写访问中,比如transfer szie是4byte,数据位宽是8byte,那么地址也要跟transfer size对齐。

INCR读写example

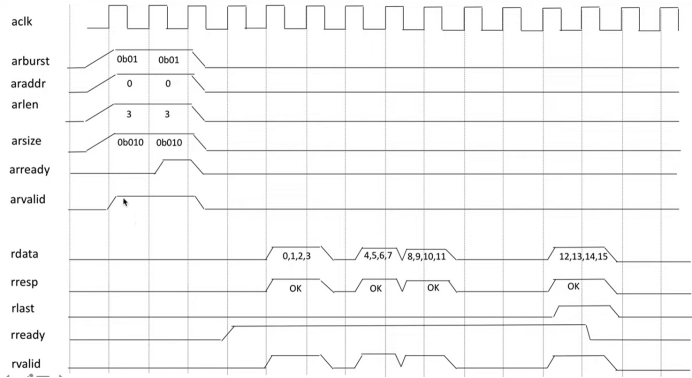

上图是读操作,ARVALID和ARREADY同时有效的时候,采样相关的控制信号,下一个周期ARVALID和ARREAD拉低,在一次burst传输中,控制信号只采样一次。

上图读操作的burst length是4,4次transfer,从图中可以看出,每次transfer 都要回一个rresp,这跟写不同,写只回一次bresp;最后一次transfer的时候,RLAST拉高一个cycle。

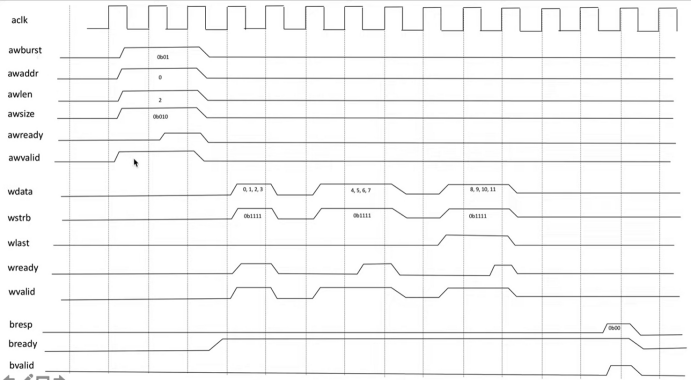

写跟读的不同是写的bresp只回一次。在所有数据都传输结束之后会resp。

问题:如果slave那边在burst传输过程中,buffer满了,发生slave error,slave会提前发送resp告诉master吗?

猜测:应该不会,因为即使发生错误,也要把burst传输完成。但也有可能会提前返回resp,这样可以告诉master,后面的数据可以只发0就行了,把wstrb都拉低。

本文详细介绍了AXI协议(基于IHI0022F_b_amba_axi_protocol_spec.pdfissueF)中的Burst传输特性,包括AXI3.0和4.0的区别。重点讨论了Burst传输的相关信号AxSIZE、AxLEN和AxBURST,以及Burst传输的限制,如最大长度、错误处理和非INCRburst的特定要求。此外,还提到了Wrap操作的规则和Exclusive访问的特殊需求。

本文详细介绍了AXI协议(基于IHI0022F_b_amba_axi_protocol_spec.pdfissueF)中的Burst传输特性,包括AXI3.0和4.0的区别。重点讨论了Burst传输的相关信号AxSIZE、AxLEN和AxBURST,以及Burst传输的限制,如最大长度、错误处理和非INCRburst的特定要求。此外,还提到了Wrap操作的规则和Exclusive访问的特殊需求。

2407

2407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?