简单易懂的AXI_Lite 总线详解

1、前言

AXI_LITE协议主要应用于Xilinx的ZYNQ芯片构架下的ARM和FPGA之间的数据读写,更偏向于单个寄存器的读写。

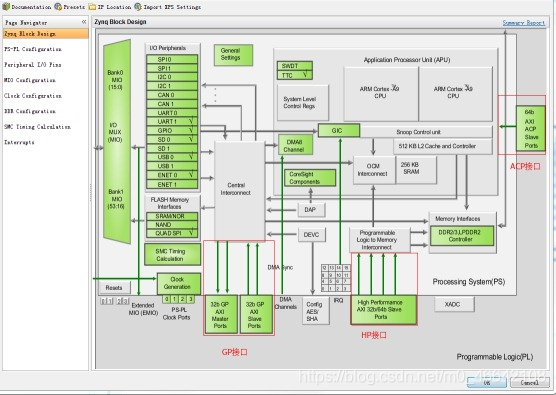

2、AXI总线与ZYNQ的关系

AXI(Advanced eXtensible Interface)本是由ARM公司提出的一种总线协议,Xilinx从6系列的FPGA开始对AXI总线提供支持,此时AXI已经发展到了AXI4这个版本,所以当你用到Xilinx的软件的时候看到的都是“AIX4”的IP,如Vivado打包一个AXI IP的时候,看到的都是Create a new AXI4 peripheral。

3、AXI总线和AXI接口以及AXI协议

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。 协议就是传输数据的规则。

3.1、AXI总线概述

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

首先说AXI4总线和AXI4-Lite总线具有相同的组成部分:

(1)读地址通道,包含ARVALID, ARADDR, ARREADY信号;

(2)读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

(3)写地址通道,包含AWVALID,AWADDR, AWREADY信号;

(4)写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

(5)写应答通道,包含BVALID, BRESP, BREADY信号;

(6)系统通道,包含:ACLK,ARESETN信号。

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:

读地址信号都是以AR开头(A:address;R:read)

写地址信号都是以AW开头(A:address;W:write)

读数据信号都是以R开头(R:read) 写数据信号都是以W开头(W:write)

应答型号都是以B开头(B:back(answer back))

了解到总线的组成部分以及命名特点,那么在后续的实验中您将逐渐看到他们的身影。每个信号的作用暂停不表,放在后面一一介绍。

而AXI4-Stream总线的组成有:

(1)ACLK信号:总线时钟,上升沿有效;

(2)ARESETN信号:总线复位,低电平有效

(3)TREADY信号:从机告诉主机做好传输准备;

(4)TDATA信号:数据,可选宽度32,64,128,256bit

(5)TSTRB信号:每一bit对应TDATA的一个有效字节,宽度为TDATA/8 (6)TLAST信号:主机告诉从机该次传输为突发传输的结尾;

(7)TVALID信号:主机告诉从机数据本次传输有效;

(8)TUSER信号 :用户定义信号,宽度为128bit。

对于AXI4-Stream总线命名而言,除了总线时钟和总线复位,其他的信号线都是以T字母开头,后面跟上一个有意义的单词,看清这一点后,能帮助读者记忆每个信号线的意义。如TVALID = T+单词Valid(有效),那么读者就应该立刻反应该信号的作用。每个信号的具体作用,在后面分析源码时再做分析

3.2、 AXI接口介绍

三种AXI接口分别是:

AXI-GP接口(4个):是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS中的片内外设。

AXI-HP接口(4个):是高性能/带宽的标准的接口,PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

AXI-ACP接口(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。 我们可以双击查看ZYNQ的IP核的内部配置,就能发现上述的三种接口,图中已用红色方框标记出来,我们可以清楚的看出接口连接与总线的走向:

3.3、 AXI协议概述

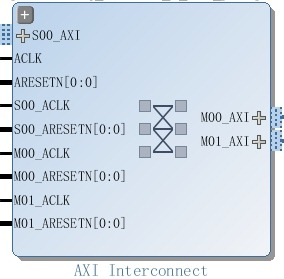

讲到协议不可能说是撇开总线单讲协议,因为协议的制定也是要建立在总线构成之上的。虽然说AXI4,AXI4-Lite,AXI4-Stream都是AXI4协议,但是各自细节上还是不同的。 总的来说,AXI总线协议的两端可以分为分为主(master)、从(slave)两端,他们之间一般需要通过一个AXI Interconnect相连接,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。当我们添加了zynq以及带AXI的IP后再进行自动连线时vivado会自动帮我们添加上这个IP,大家应该是不陌生了。 AXI Interconnect的主要作用是,当存在多个主机以及从机器时,AXI Interconnect负责将它们联系并管理起来。由于AXI支持乱序发送,乱序发送需要主机的ID信号支撑,而不同的主机发送的ID可能相同,而AXI Interconnect解决了这一问题,他会对不同主机的ID信号进行处理让ID变得唯一。

AXI协议将读地址通道,读数据通道,写地址通道,写数据通道,写响应通道分开,各自通道都有自己的握手协议。每个通道互不干扰却又彼此依赖。这也是AXI高效的原因之一。

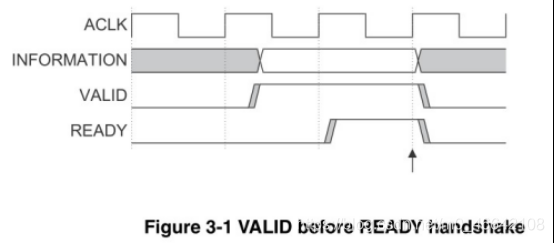

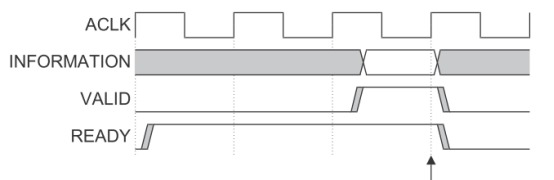

3.4 AXI协议之握手协议

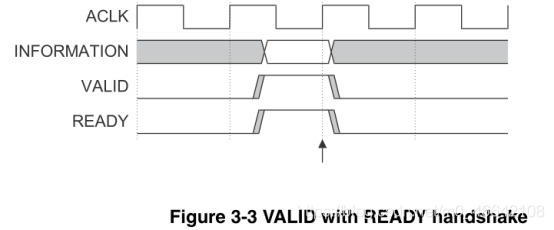

AXI4所采用的是一种READY,VALID握手通信机制,简单来说主从双方进行数据通信前,有一个握手的过程。传输源产生VLAID信号来指明何时数据或控制信息有效。而目地源产生READY信号来指明已经准备好接受数据或控制信息。传输发生在VALID和READY信号同时为高的时候。VALID和READY信号的出现有三种关系。

(1) VALID先变高READY后变高。时序图如下: 在箭头处信息传输发生。

(2) READY先变高VALID后变高。时序图如下:同样在箭头处信息传输发生

(3) VALID和READY信号同时变高。时序图如下:

在这种情况下,信息传输立马发生,如图箭头处指明信息传输发生。 需要强调的是,AXI的五个通道,每个通道都有握手机制,接下来我们就来分析一下AXI-Lite的源码来更深入的了解AXI机制。

3.5、 突发式读写

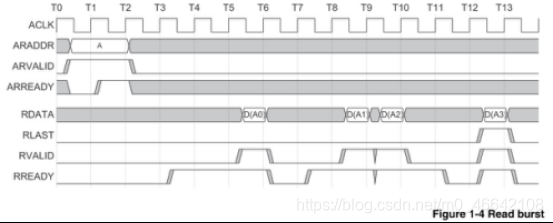

1、突发式读的时序图如下:

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持VALID为低直到读数据有效。为了表明一次突发式读写的完成,设备用RLAST信号来表示最后一个被传输的数据。

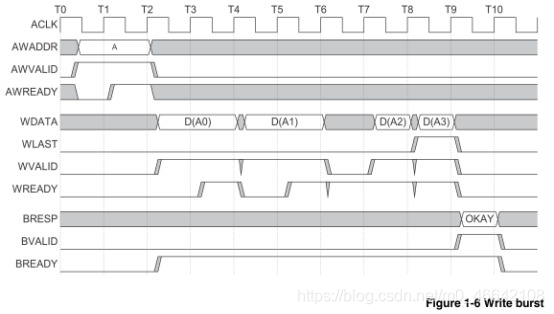

2、 突发式写时序图如下:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

4 AXI4-Lite详解

4.1 AXI4-Lite源码查看

Step1:要看到AXI-Lite的源码,我们先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Pa

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5634

5634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?