微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

工程源码获取地址:

https://download.csdn.net/download/m0_50111463/88526903?spm=1001.2014.3001.5501

四、开源的AXILite的使用及仿真

本章内容介绍工程中使用的开源AXI4Lite源码,推荐优势在于移植方面,可用于不同的FPGA开发平台,比如国产芯片EDA等。

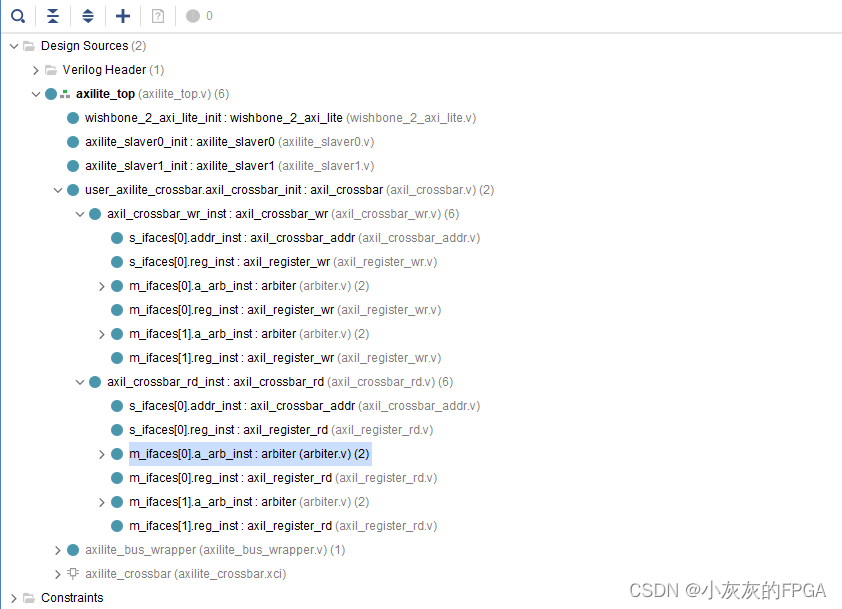

开源代码框架如下:

具体代码就不详细讲解,此框架适合移植代码使用

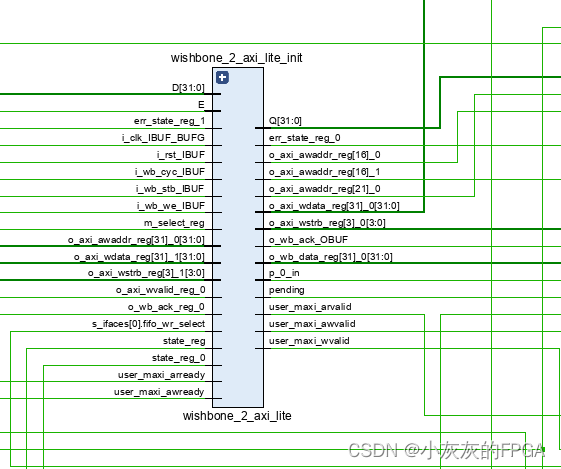

1、通过wb转换axilite接口,便于操作使用,不同控制axilite的各个通道;此处地址直接透传,并不符合wb总线的要求,未作偏移,如果有需要的自行修改

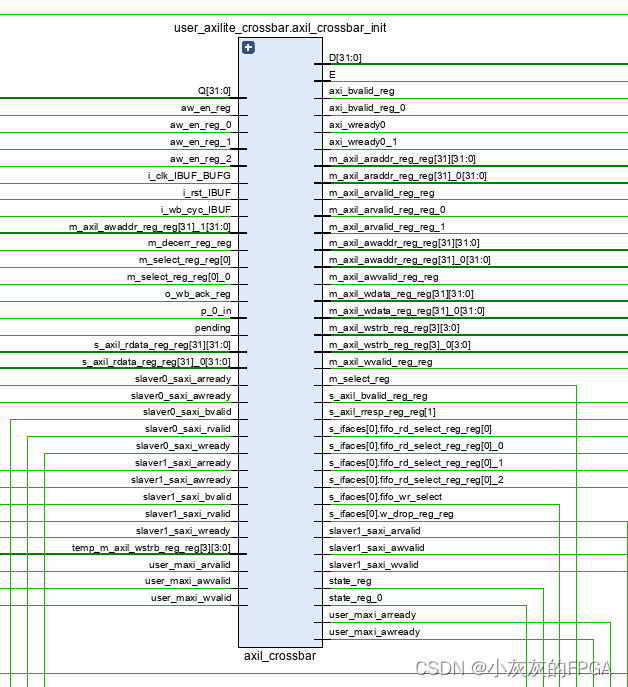

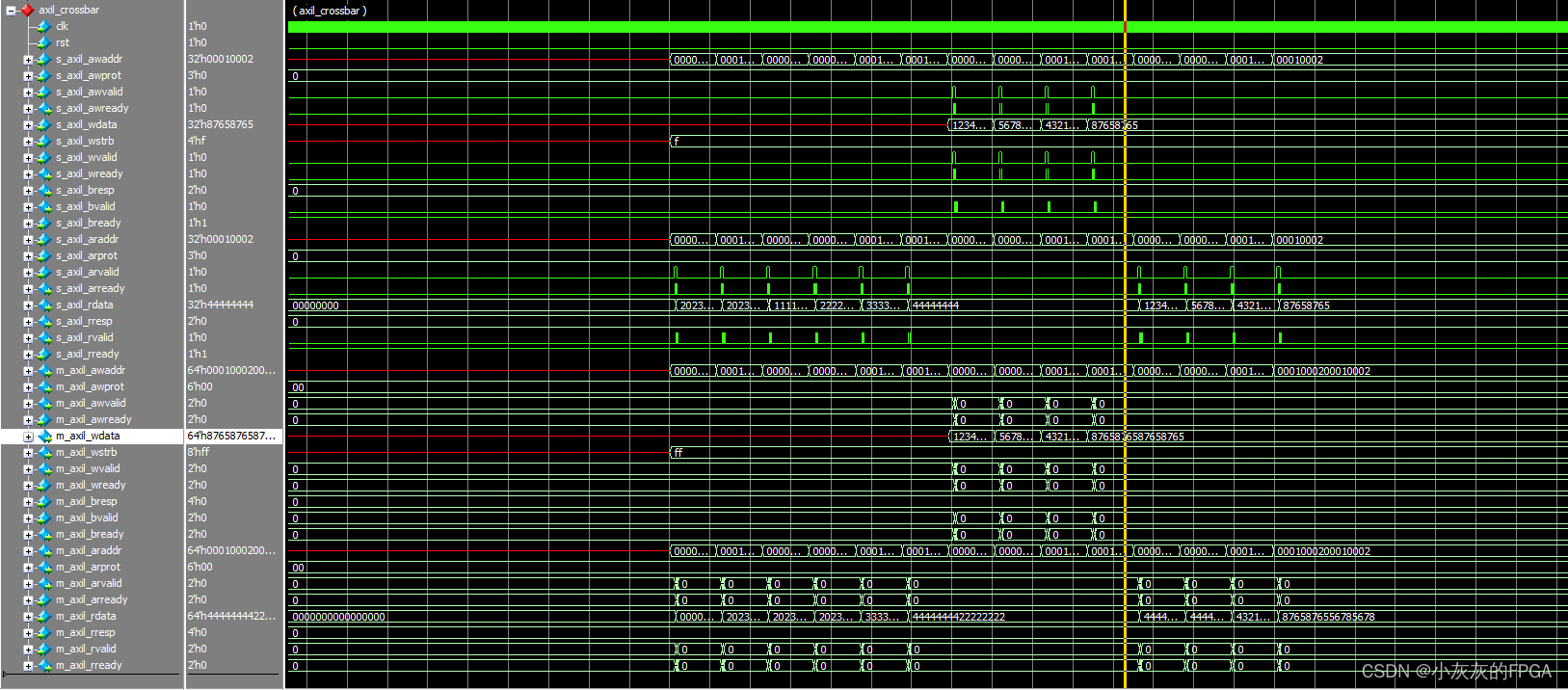

2、通过axil_crossbar实现一主两从的互联,包括仲裁以及寄存器读写控制

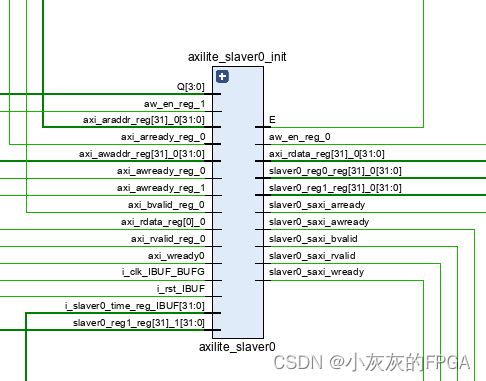

3、通过自定义模块slaver0/slaver1完成内部寄存器与外设控制、状态信息的映射

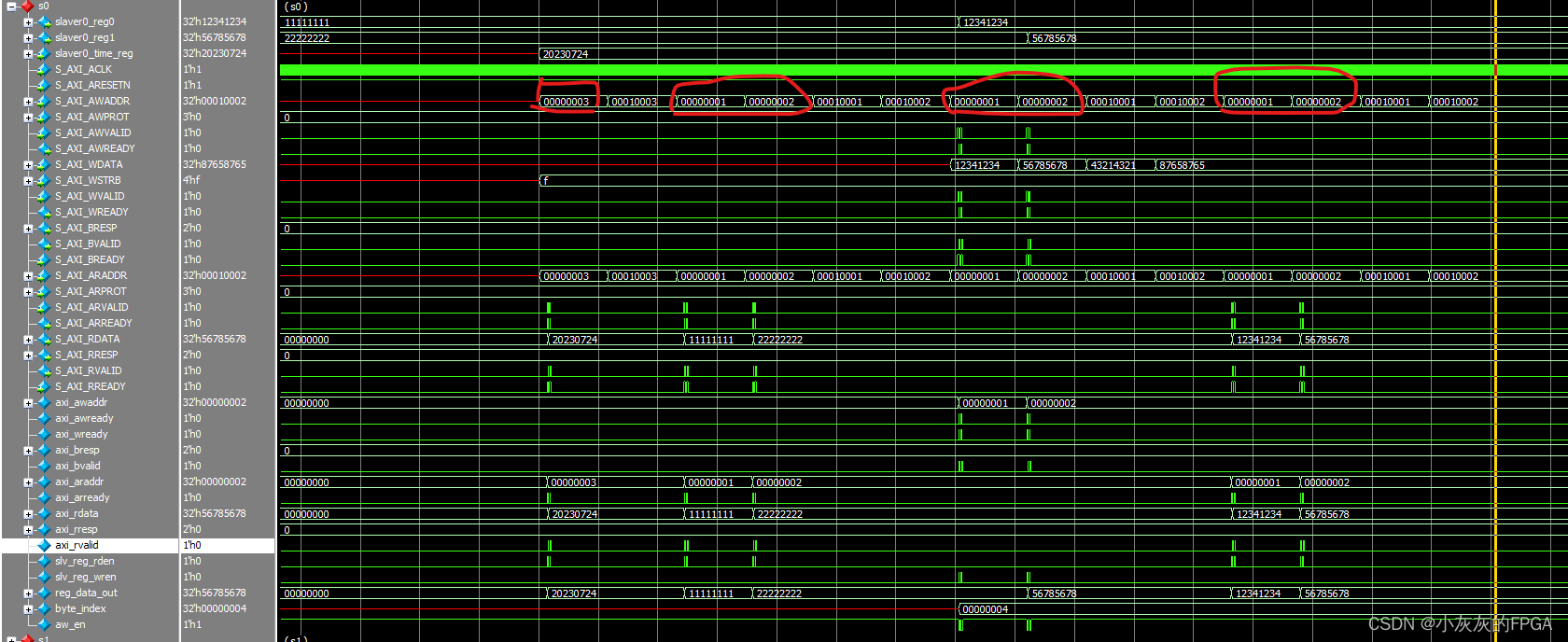

4、slaver0的AXIlite的仿真

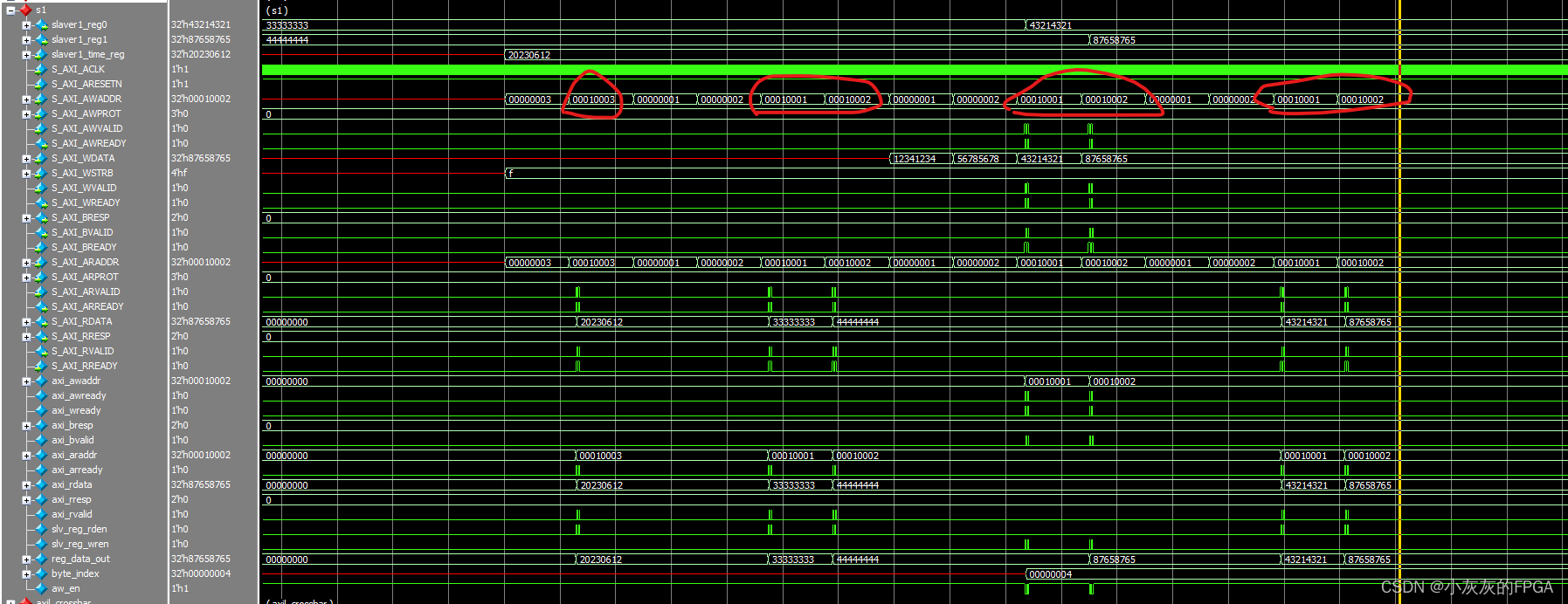

5、slaver1的AXIlite的仿真

6、axil_crossbar的互联仿真

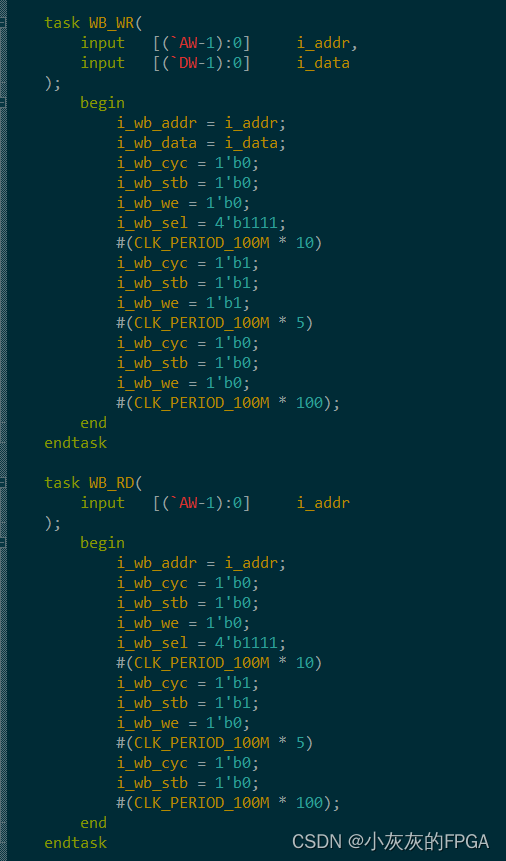

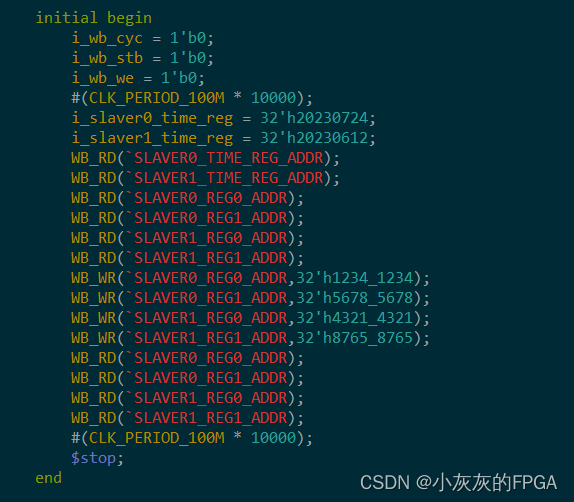

五、仿真文档TB简单说明

1、通过task封装WB的读写操作用于仿真使用

2、对宏定义的Slaver0/Slaver1的自定义寄存器进行操作,从而实现寄存器的读写控制

至此AXI4Lite系列完结,本工程只是简单的使用AXI4lite,但已经具备工程应用思想,完全可以移植至项目中,只需要对wb的主机控制和自定义从机的寄存器内容即可。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?