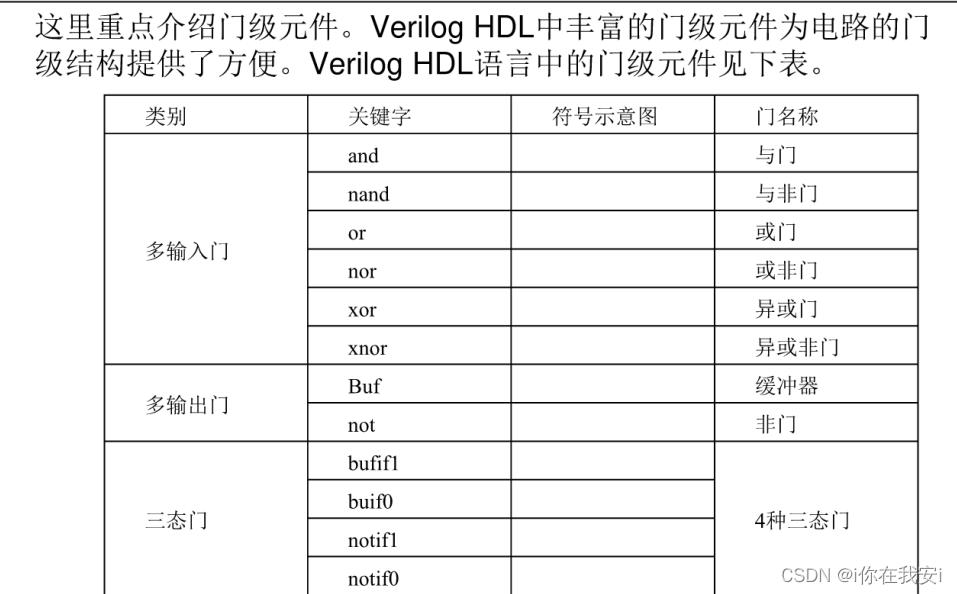

门级建模:12个基本门级元件包括:与,或,非,与非,或非,异或,异或非,缓冲器,以及高电平使能三态缓冲器,低电平使能三态缓冲器,高电平使能三态非门,低电平使能三态非门 构成

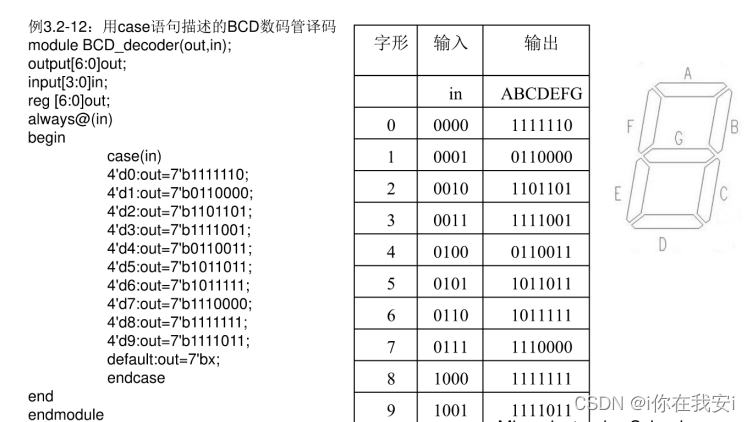

数据流建模:采用运算操作符完成 +-*/%...

行为级建模:在描述电路的行为,亦或者可以说是在描述电路的输入与输出的关系(always@())

优点:不用去过多的关注底层电路的实现形式,更多的是关注电路的行为

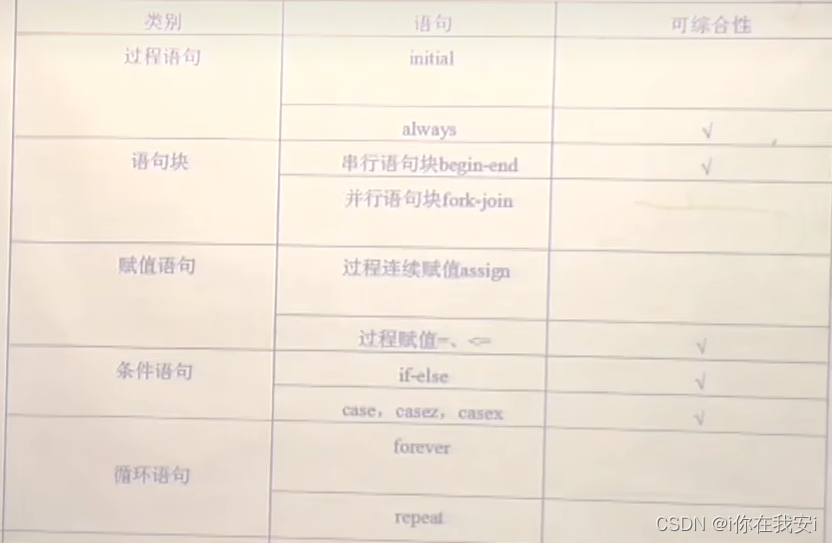

只有在行为级中间(always@())的串行语句块(begin end)中间使用阻塞型赋值语句(=)的时候才是串行的结构

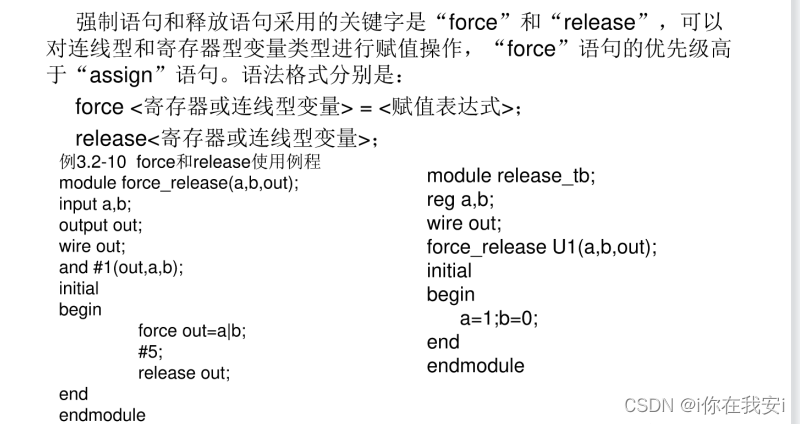

force - release 一般用于调试,当代码比较多时,有错误,通过force强制拉到正确电平 再延迟释放 看看在这段延迟时间内,后续信号对不对,二分法

verilog中可综合语句:input,output,parameter,reg,wire,always,assign, begin...end,case,for,posedge,negedge,or,and,default,if,function,generate,integer,while,repeat(while、repeat循环可综合时,要具有明确的循环表达式和循环条件,for可综合时也要有具体的循环范围),`define

不可综合语句:initial,fork...join,wait,time,display,forever。

保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:

(1)不能使用initial,initial一般使用在测试程序,做初始化。

(2)不建议使用延时,#1,这种只是模拟数字电路中因为布线产生的信号延时,不可综合,但也不会报错。

(3)不能使用循环次数不确定的函数,但forever在综合设计中禁止使用,只能使用在仿真测试程序中。

(4)尽量使用同步电路设计方式。<=

(5)除非关键电路设计,一般不建议调用门级元件进行设计,一般使用行为级进行设计。

(6)当使用always进行组合逻辑设计时,敏感列表里面的要列出所有输入信号。(*)

(7)在进行时序电路进行编写时,采样非阻塞赋值。组合逻辑设计时,采样阻塞赋值,但是不能在同一个always语句里两种混合使用。

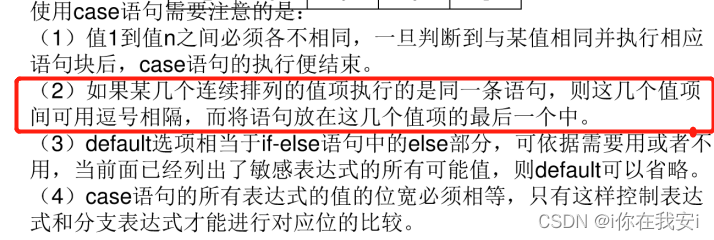

(8)为避免产生锁存器,if,case要进行完整的语句赋值,且case语句中避免使用X值,Z值。

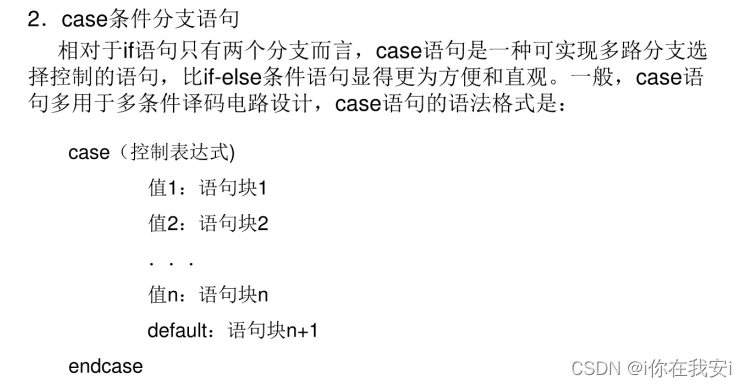

1、任何电路都有真值表,可与case语句联用

assign 可以描述所有的组合逻辑电路

串行语句中:阻塞性赋值语句按顺序执行;非阻塞性语句并列执行

并行语句中二者皆为并列执行 不可综合

在敏感事件列表里没有与(&&)只有或(|| or)的概念

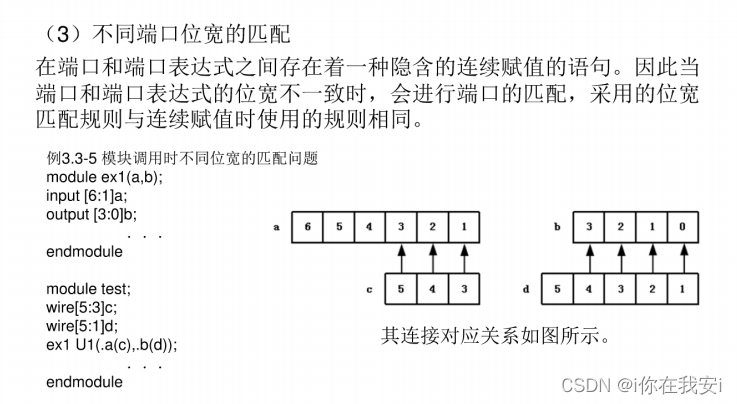

位宽不匹配 可以仿真(对应相应位置,多余位置不匹配) 但在电路中是错的 没有意义

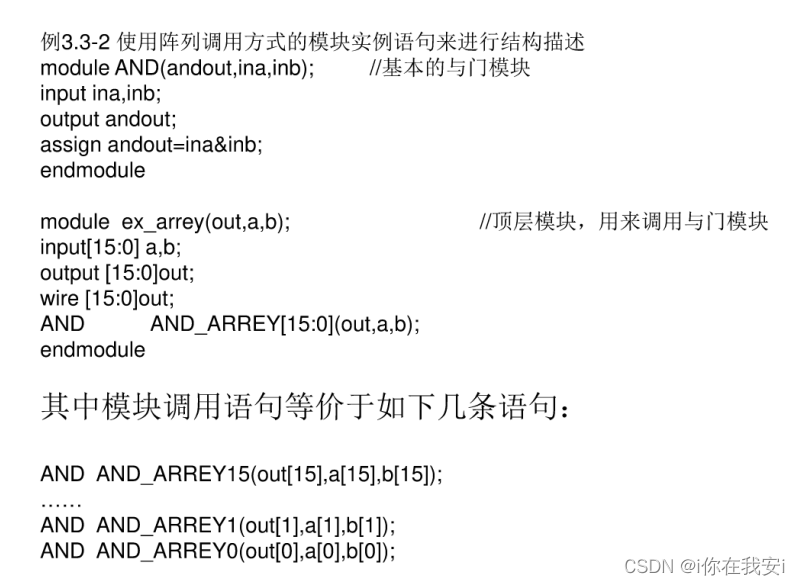

定义参数语句修改参数值

格式:defparam 实例名.参数名n=参数值n;

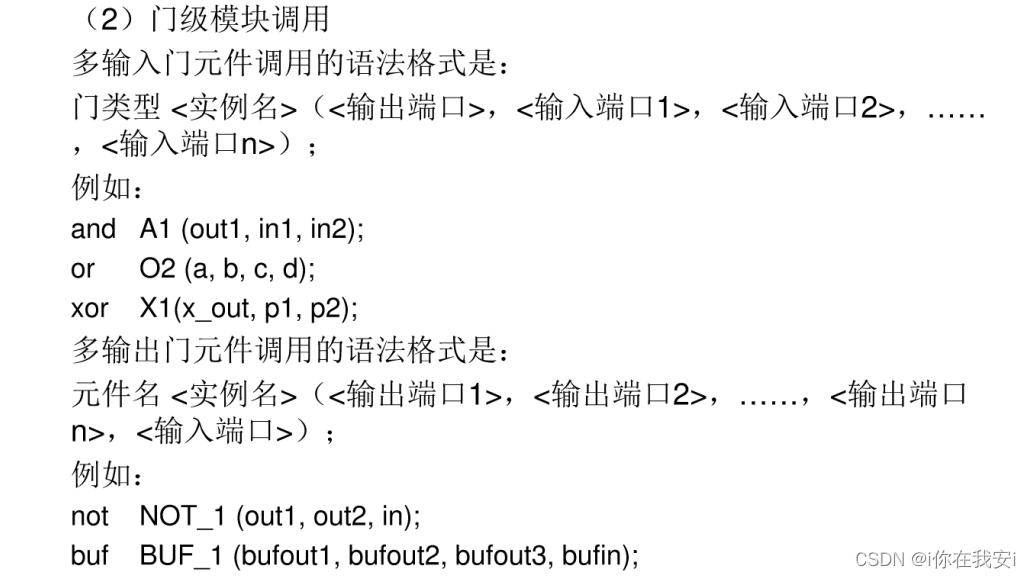

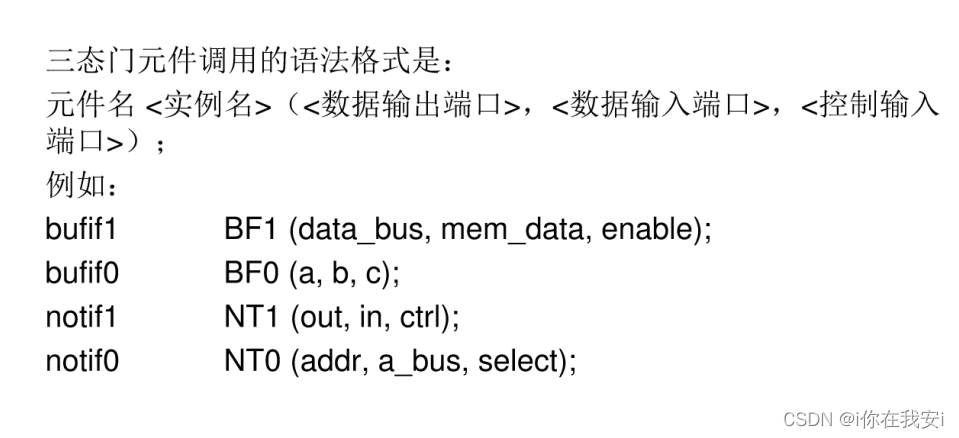

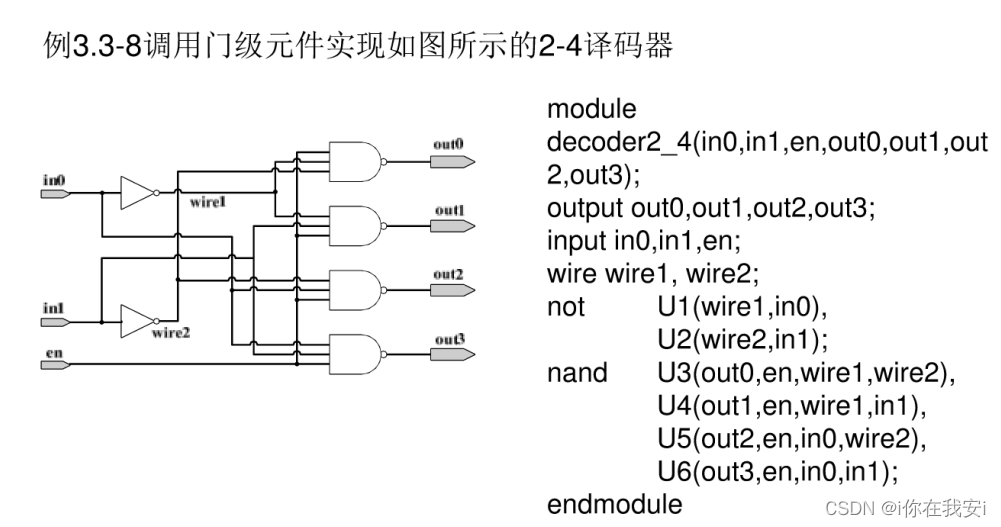

门级建模

关键字都是小写;

单入多出 单出多入的门;输出在前 输入在后 模块名 实例名(out,in);

396

396

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?