2 DDR5 SDRAM封装,引脚描述和寻址-3

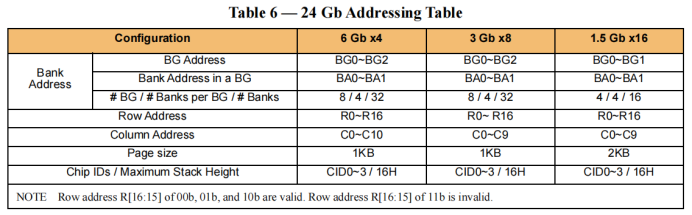

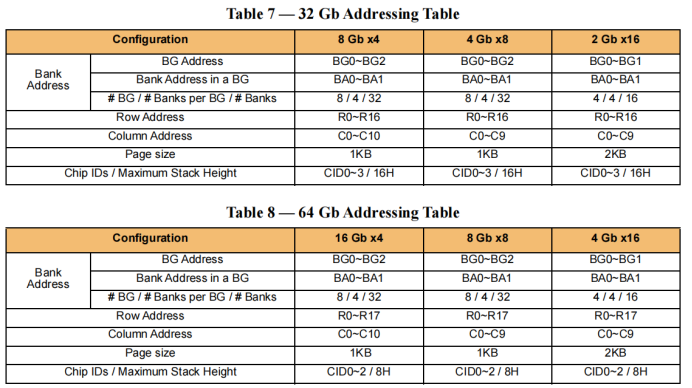

2.7 DDR5 SDRAM寻址

cell概念:每一行中的每一列为1个内部存储单元(cell);

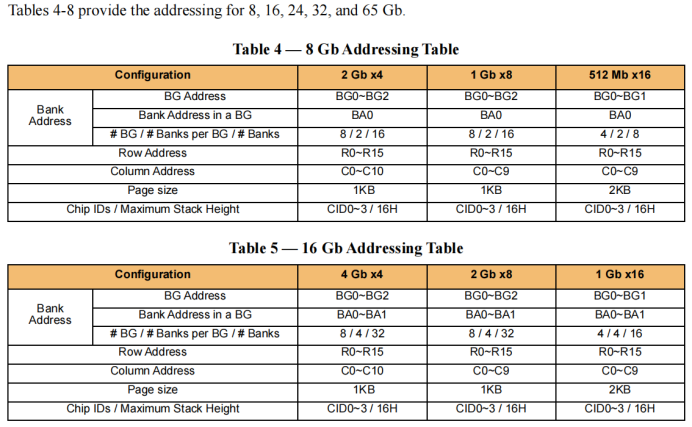

如8Gb的512Mbx16配置:

x16:芯片位宽(即I/O宽为16bit,也就是说,按道理每一行中每一列这样一个交叉点,存储容量为16bit),

但是DDR5 DRAM内部存储单元(cell)容量是芯片位宽的16倍,

所以,每个基本存储单元cell容量 为16*16bit=32B,即选定一行后,指定列,每个这样的基本存储单

元,写命令时,向其中写入32B, 读命令时,向外读出32B;

page size:每一行的容量(package的每一行)

DDR5中每一行有4位列用来表示burst order,所以共有具有存储容量能力的列数:2^(10-4)=2^6列

page size = 具有存储容量能力的列数*单个cell容量 = 2^6*32B = 2^11B = 2KB

每个bank容量 = row*page size

每个bank容量 = 2^16 * 2KB = 128MB

每个chip共计8个bank

每个chip容量 = 8 * 128MB = 1GB = 8Gb

讲到这里顺便讲一下prefetch 与 BL 和 DDR5每次操作将交付字节数:

DDR5提供2个独立的32bit数据通道,prefetch为16,默认BL为16(这些为协议定义的内容);

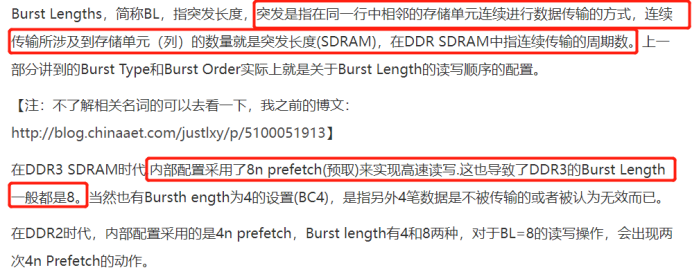

首先澄清一下BL的概念:Burst Lengths,突发长度,突发是指在同一行中相邻的存储单元连续进行数据传输

的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期

数。

对于DDR5,BL=16,通道通路32bit,则每次操作,产生的数据量为16*32bit=64B,即意味着每次操作,

DDR5的单个channel一次交付64B数据,一个DDR5双channel一次就交付2个64B数据。

为什么要这样设计?

cacheline概念:当从内存中取单元到cache中时,会一次取一个cacheline大小的内存区域到cache中,

然后存进相应的cacheline中。

x86环境下一个CacheLine是64字节,所以猜想,DDR5每次交付数据量与cacheline大小有一定关系。

至于,进行一次操作时,通道通路的每个BL的32bit数据是怎么从芯片内部拿?需要进一步考证。

以下可以作为线索

page size ?

page size is the number of bytes of data delivered from the array to the internal sense

amplifiers when an ACTIVE command is registered.

page size is per bank.

1064

1064

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?