11 验证——编写test bench、波形产生、从文本文件中读取向量、向文本文件中写入向量

本章介绍了如何编写测试验证程序 (test bench)。测试验证程序用于测试和验证设计的正

确性。Verilog HDL提供强有力的结构来说明测试验证程序。

11.1 编写测试验证程序

测试验证程序有三个主要目的:

1) 产生模拟激励(波形)。

2) 将输入激励加入到测试模块并收集其输出响应;

3) 将响应输出与期望值进行比较。

Verilog HDL提供了大量的方法以编写测试验证程序。在本章中,我们将对其中的某些方

法进行探讨。典型的测试验证程序形式如下:

11.2 波形产生

有两种产生激励值的主要方法:

1) 产生波形,并在确定的离散时间间隔加载激励。

2) 根据模块状态产生激励,即根据模块的输出响应产生激励。

通常需要两类波形。一类是具有重复模式的波形,例如时钟波形,另一类是一组指定的

值确定的波形。

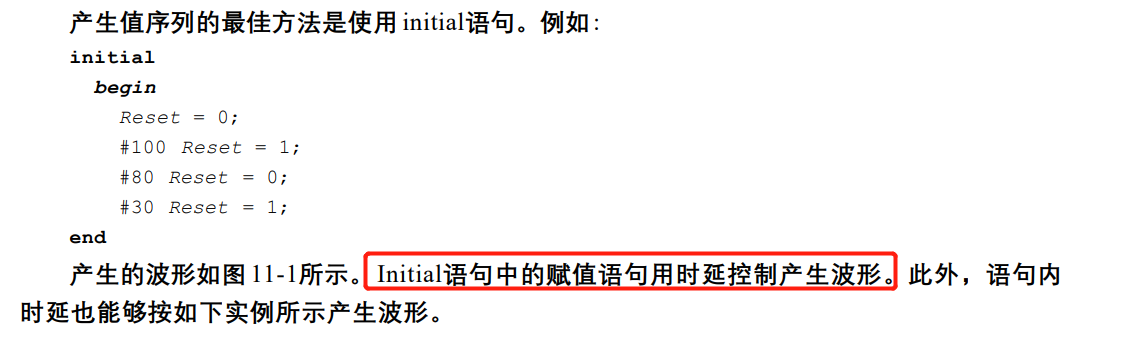

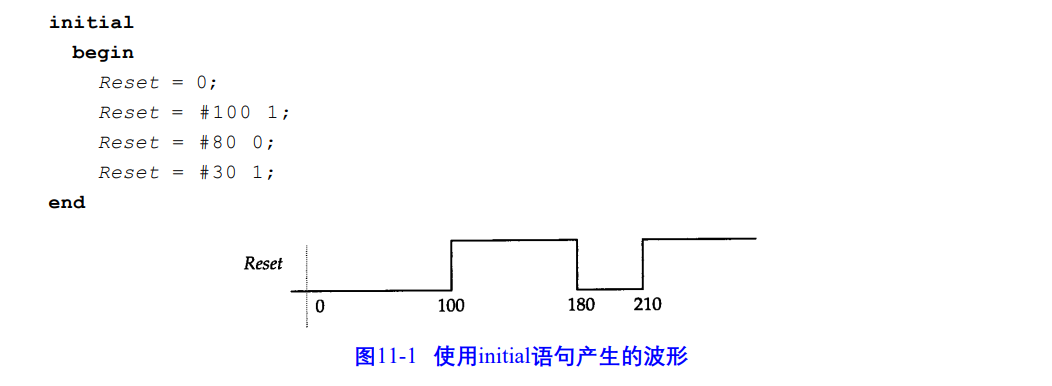

11.2.1 值序列

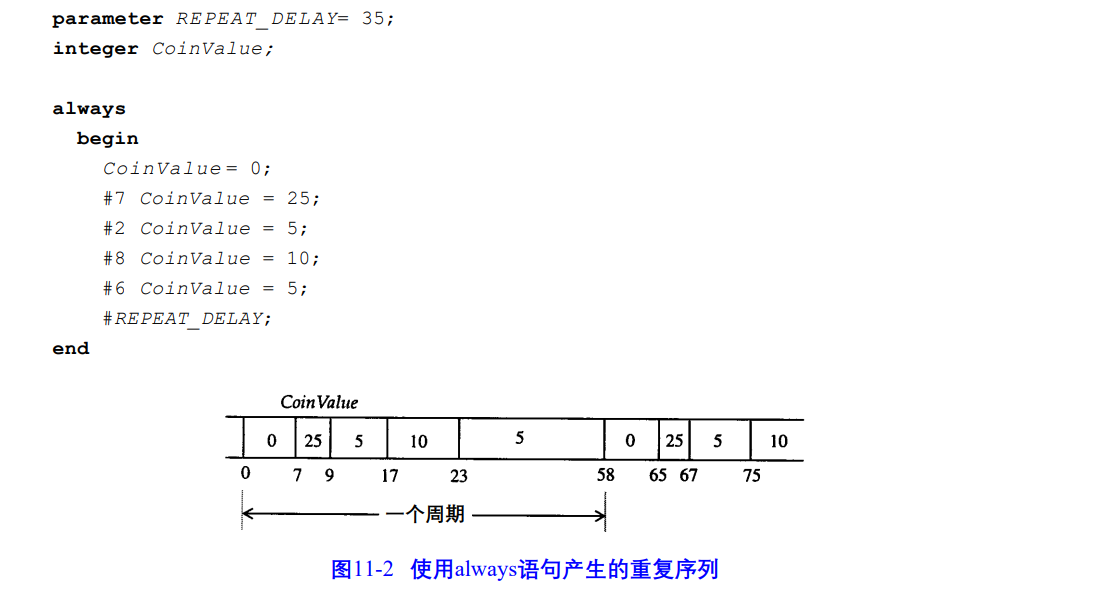

为重复产生一个值序列,可以使用 a l w a y s语句替代i n i t i a l语句,这是因为i n i t i a l语句只执行

一次而a l w a y s语句会重复执行。下例的a l w a y s语句所产生的波形如图11 - 2所示。

11.2.2 重复模式

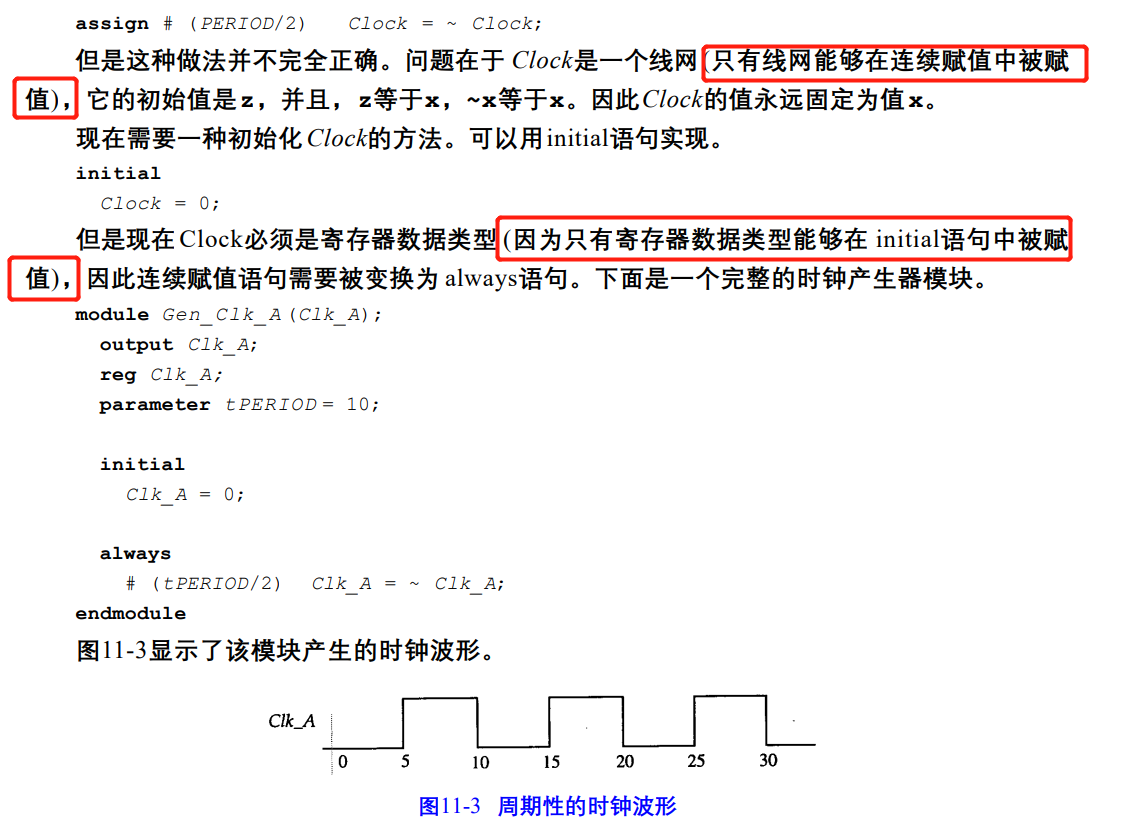

重复模式的生成通过使用如下形式的连续赋值形式加以简化:

生成标准时钟波形

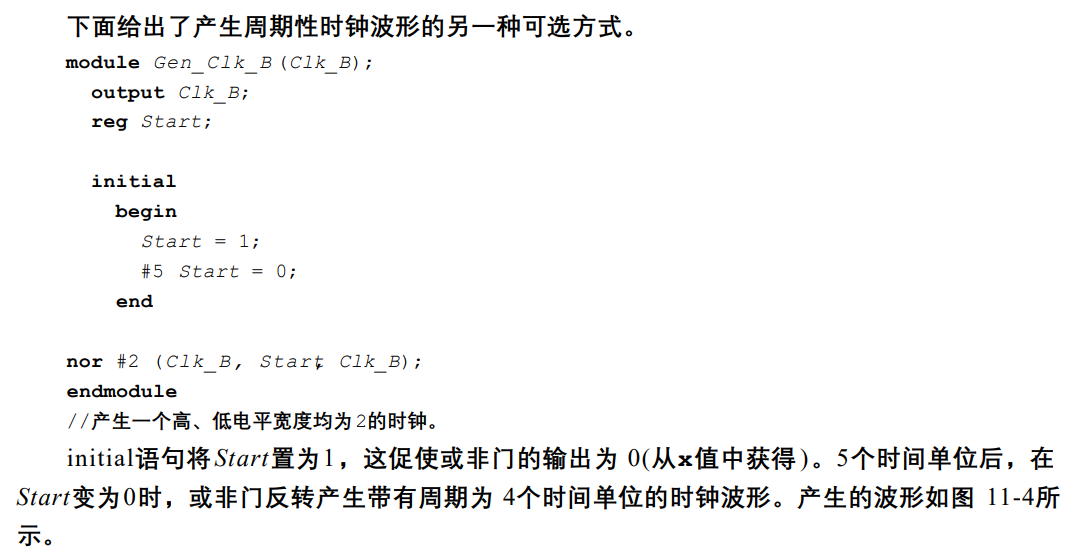

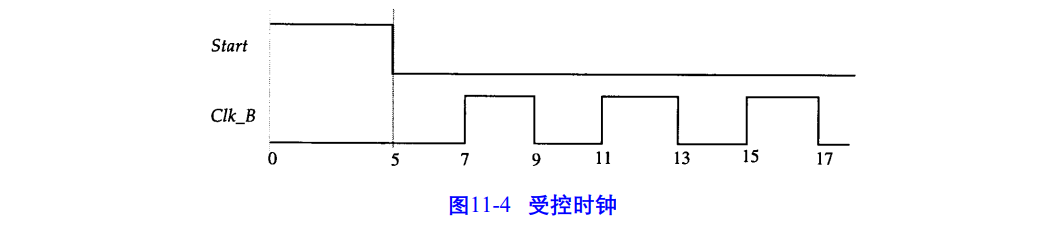

或非门生成时钟波形

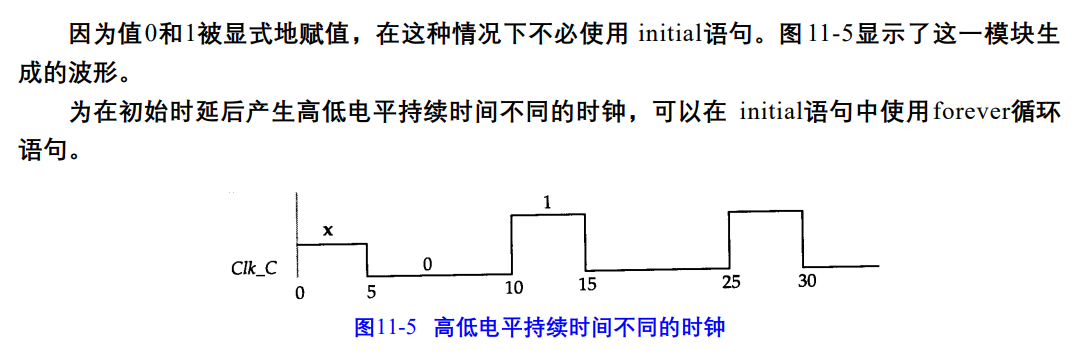

产生高低电平持续时间不同的时钟波形

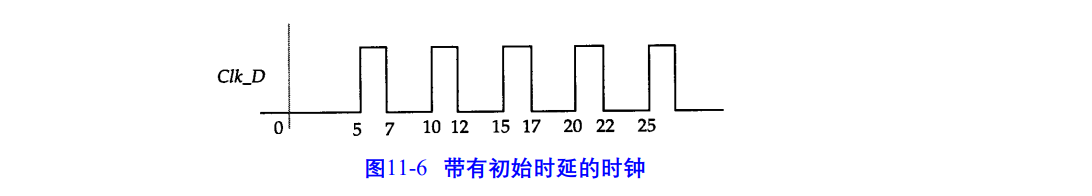

forever产生高低电平持续时间不同的时钟波形

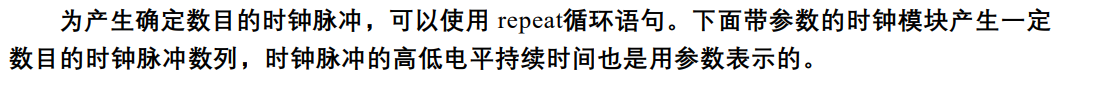

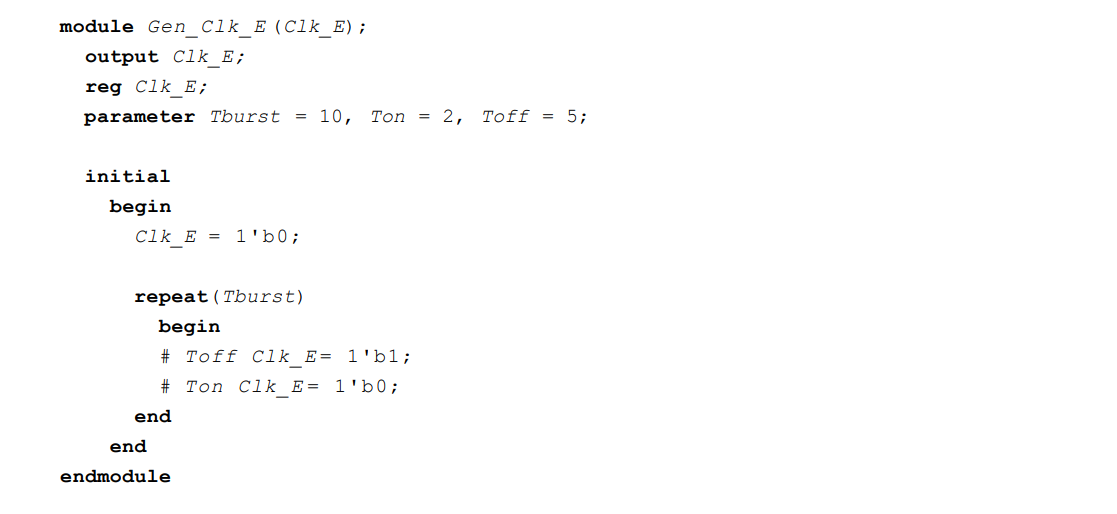

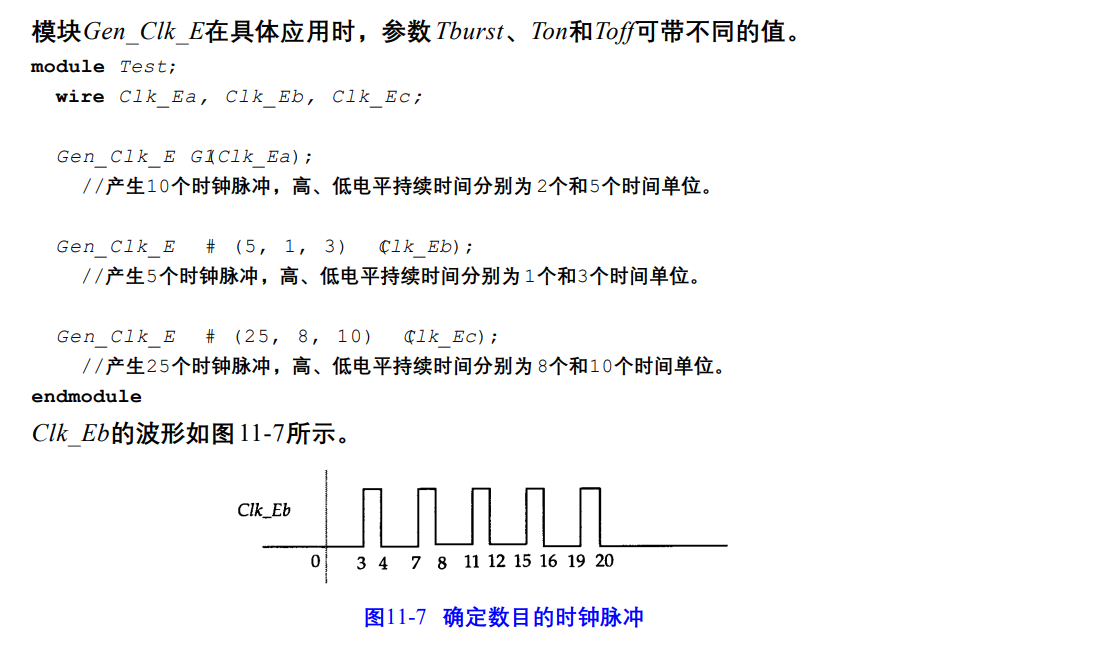

repeat产生确定数目时钟脉冲

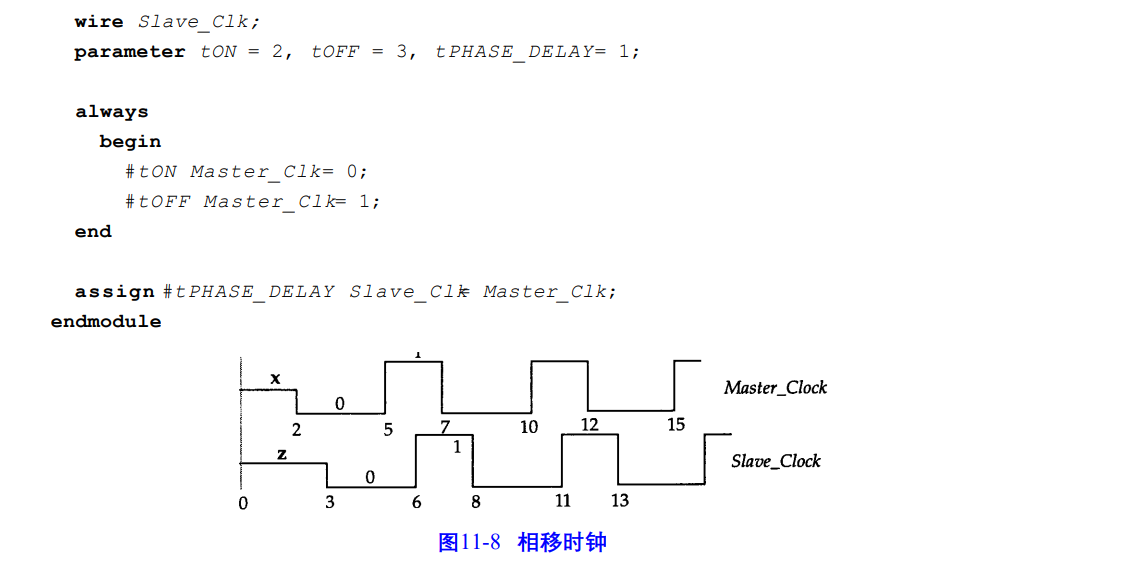

连续赋值产生一个时钟的相移时钟

11.3 测试验证程序实例

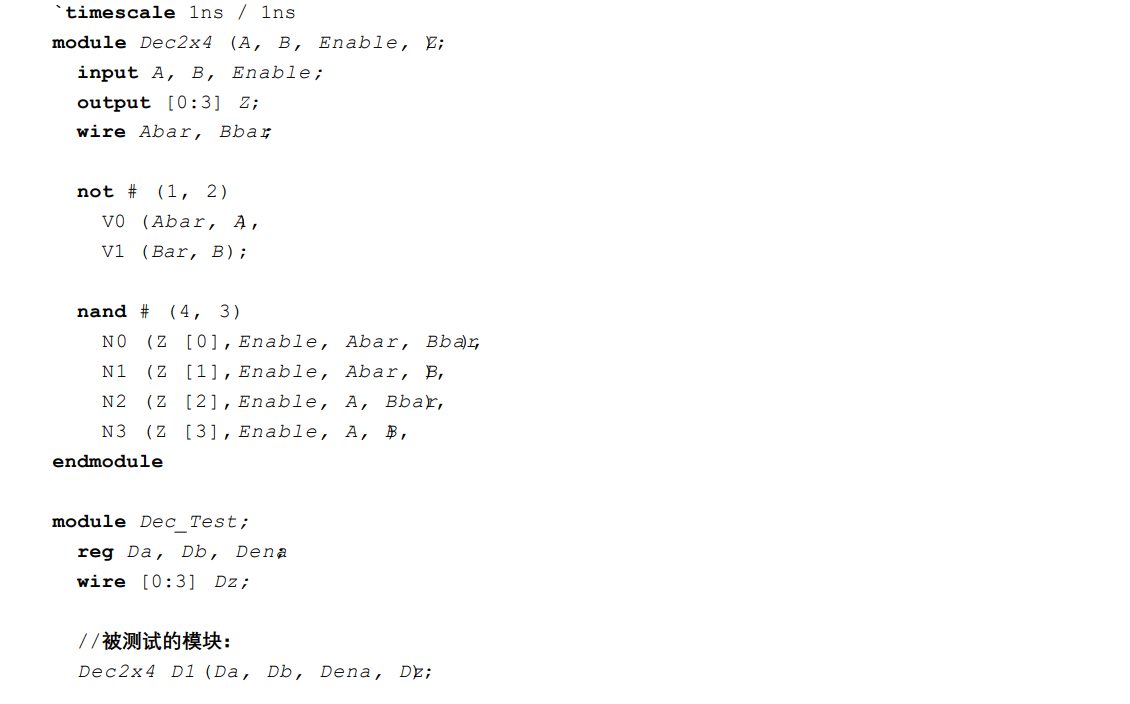

11.3.1 解码器

2 - 4解码器和它的测试验证程序

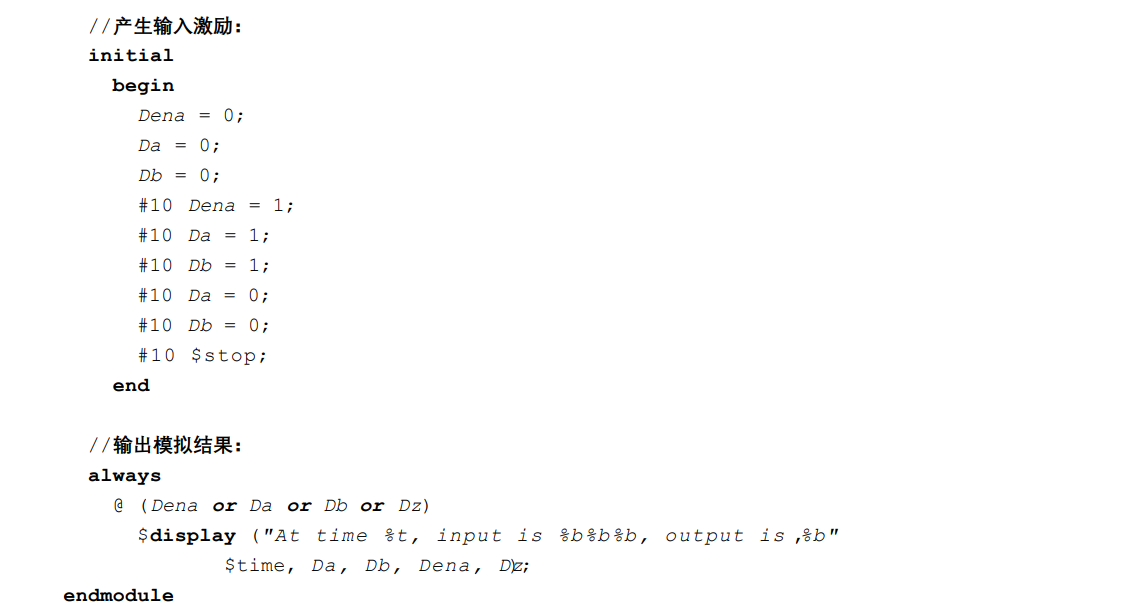

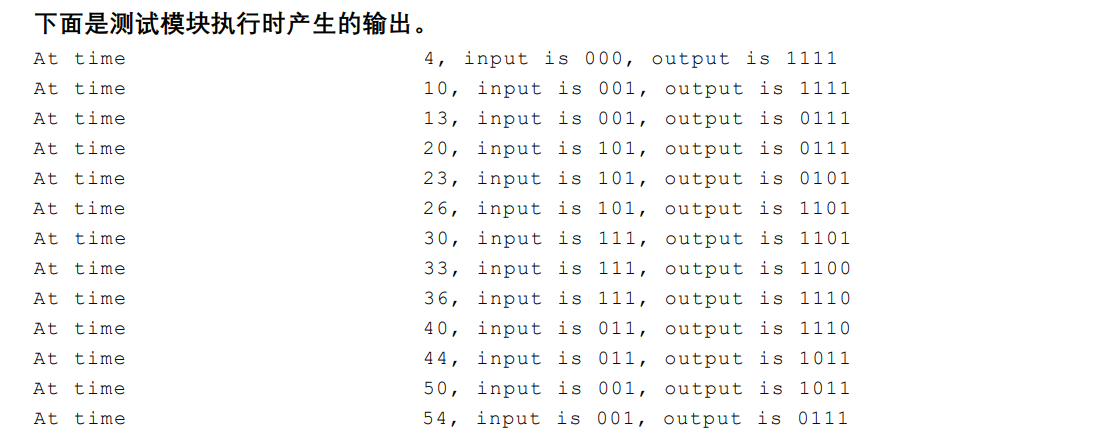

下面是2 - 4解码器和它的测试验证程序。任何时候只要输入或输出信号的值发生变化,输

出信号的值都会被显示输出。

11.3.2 触发器

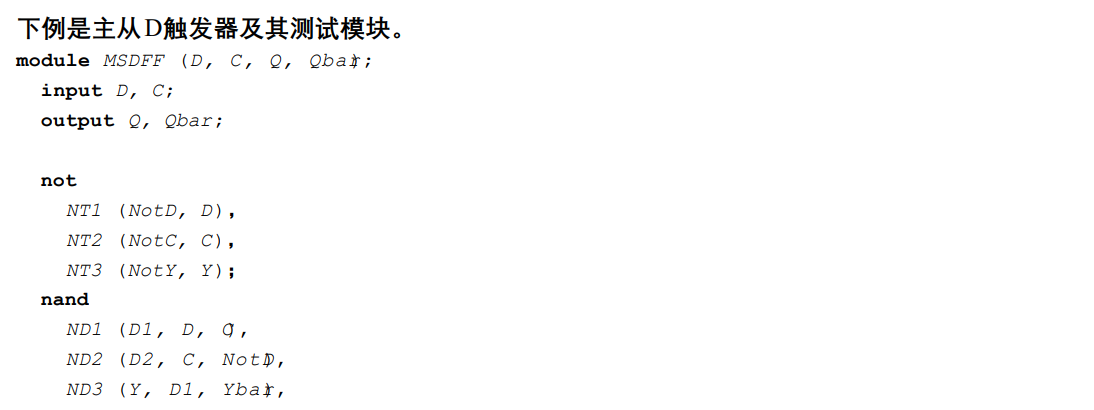

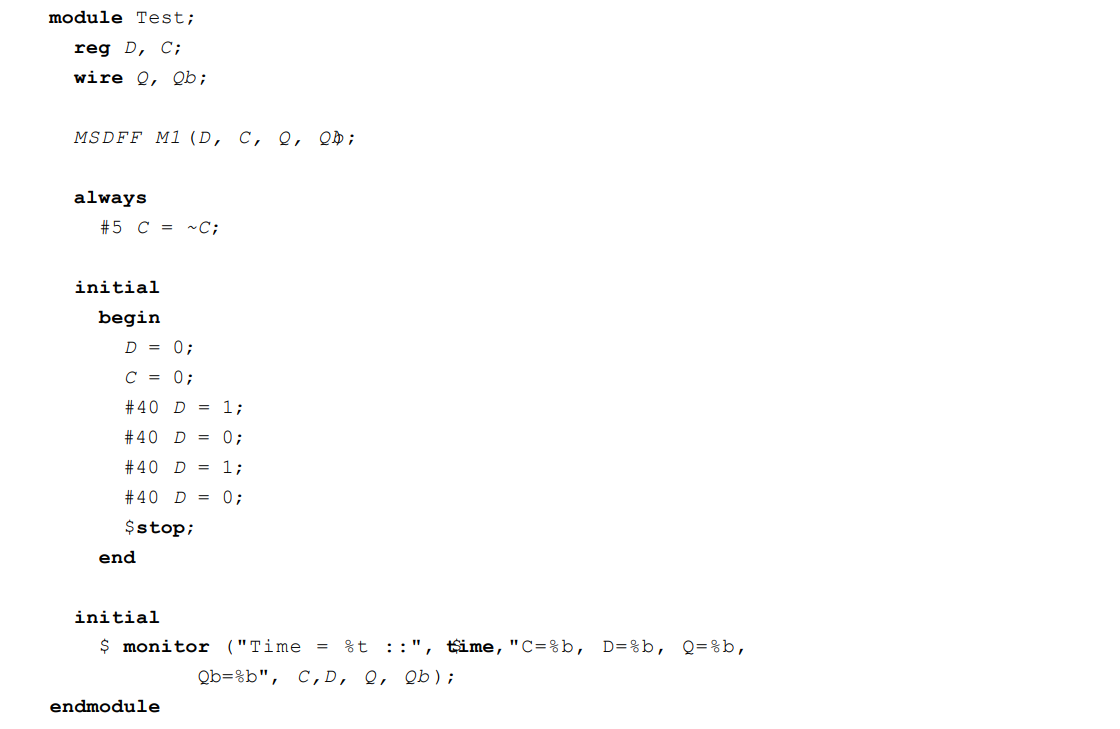

主从D触发器及其测试模块

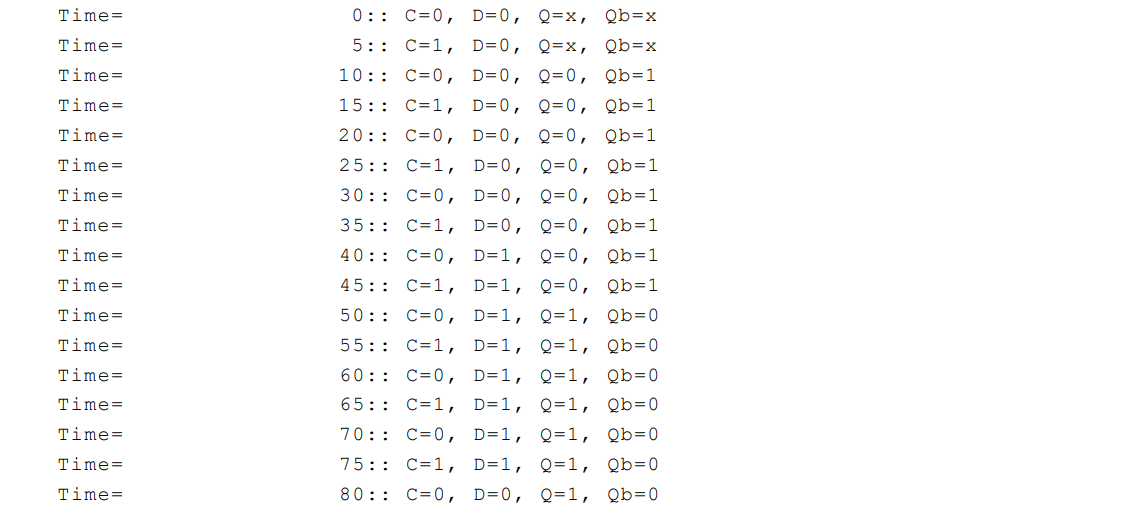

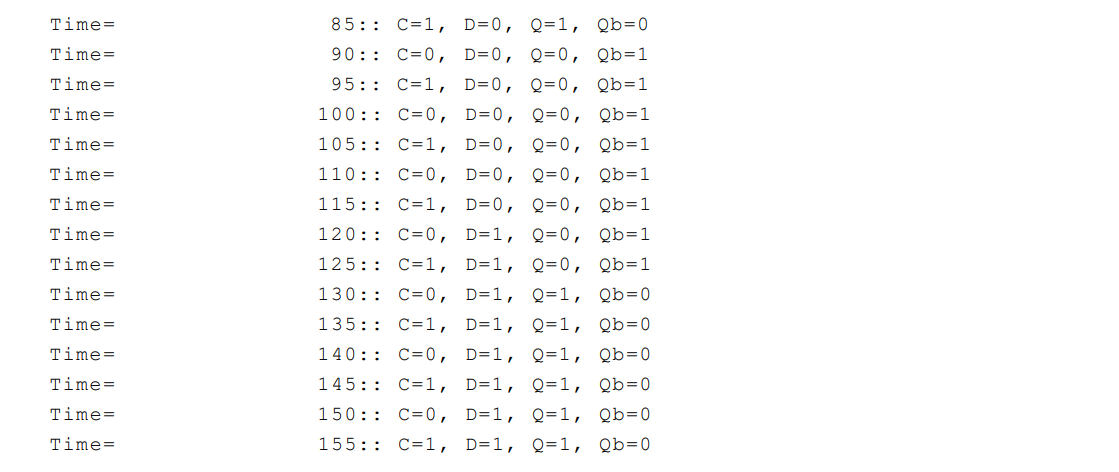

在此测试验证模块中,触发器的两个输入和两个输出结果均设置了监控,故只要其中任

何值发生变化就输出指定变量的值。下面是执行产生的输出结果。

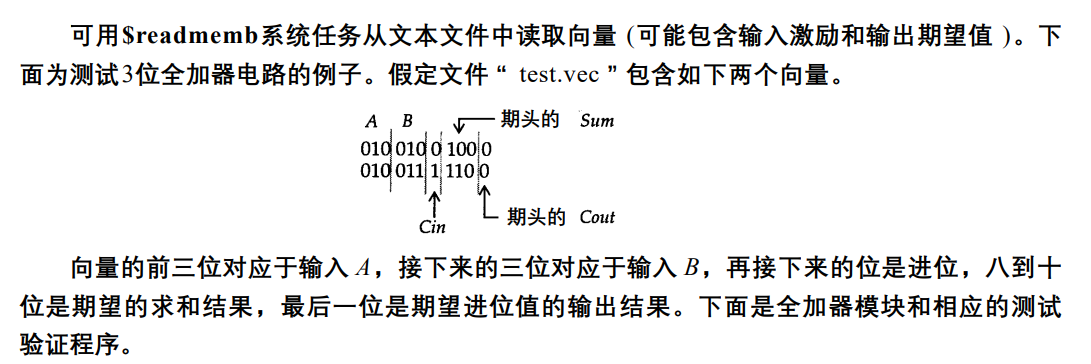

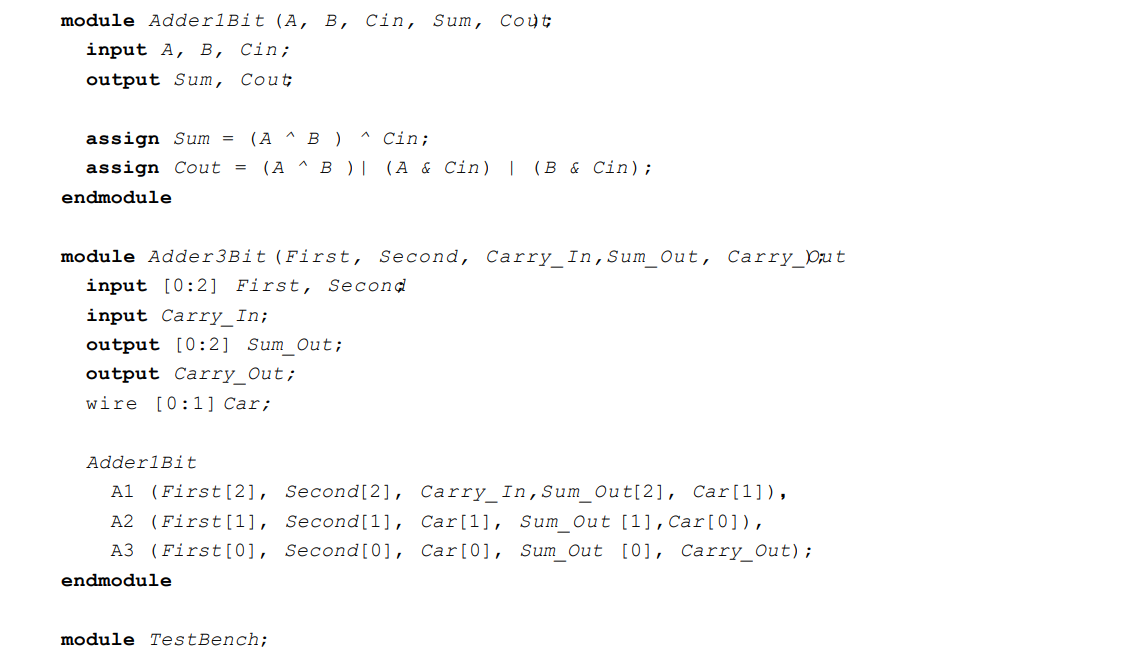

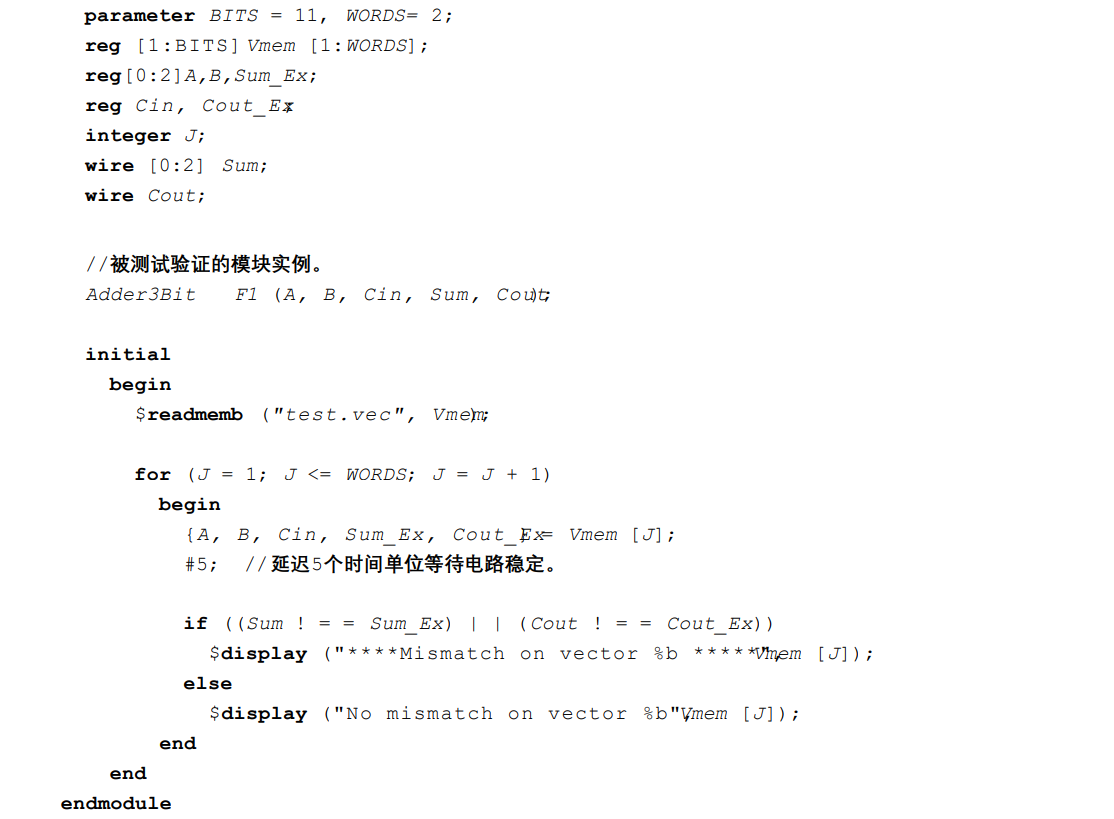

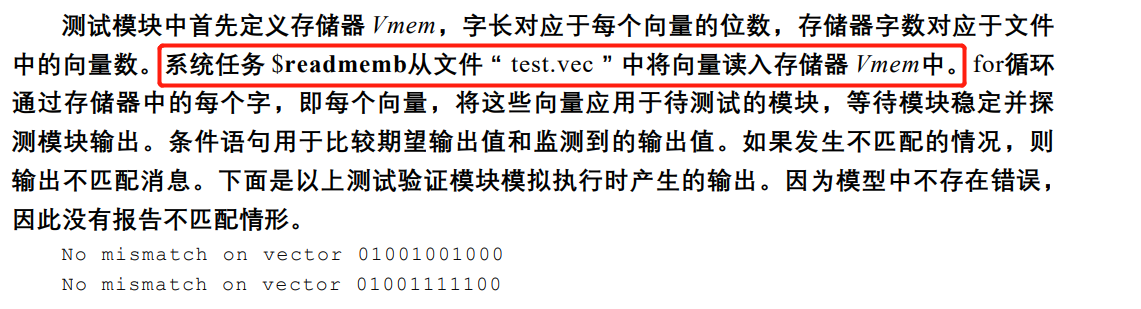

11.4 从文本文件中读取向量

$ readmemb系统任务

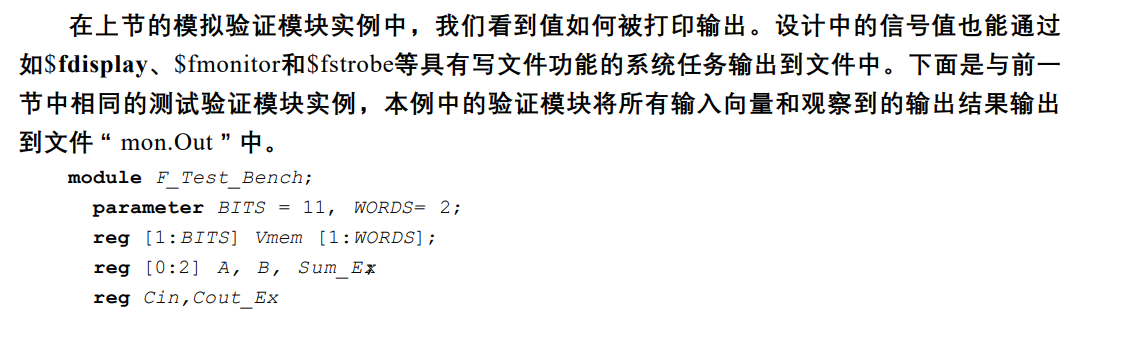

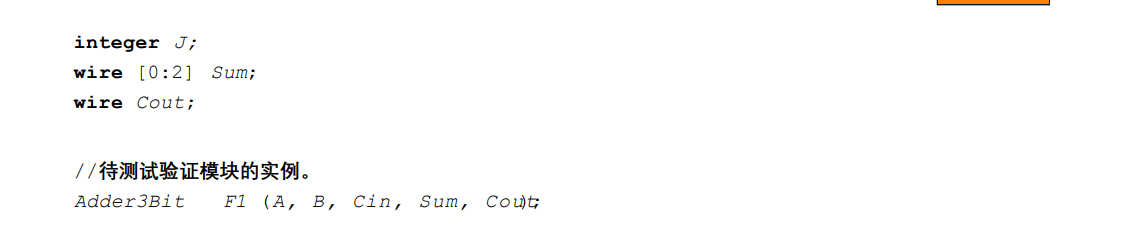

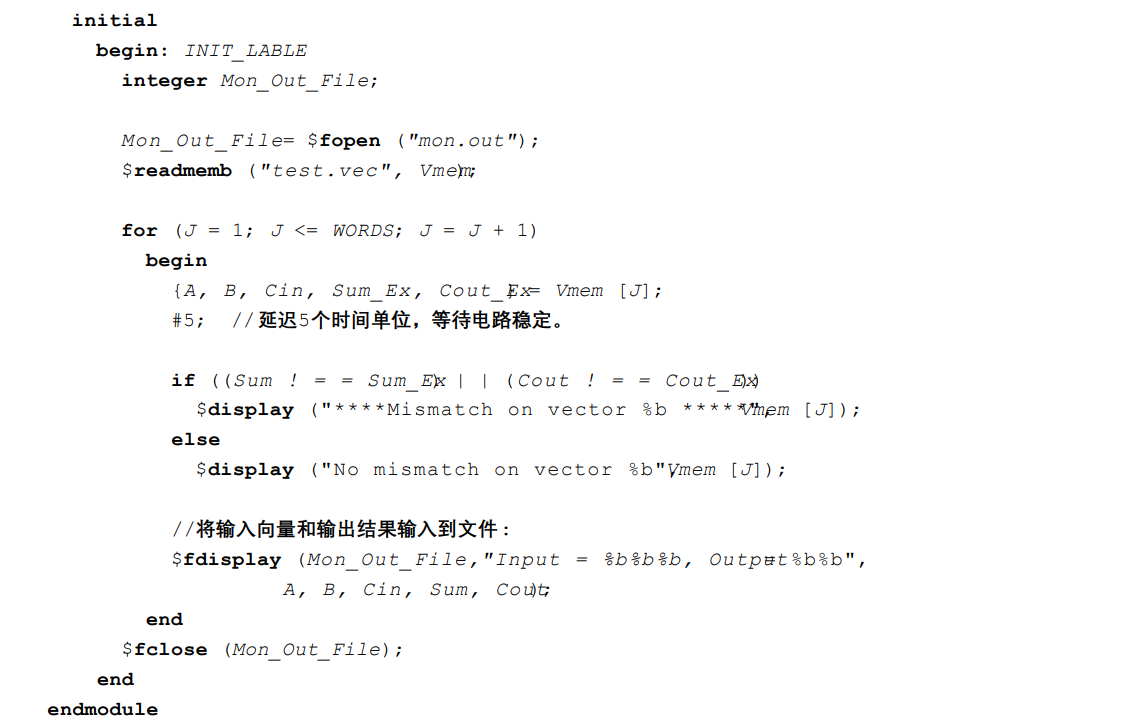

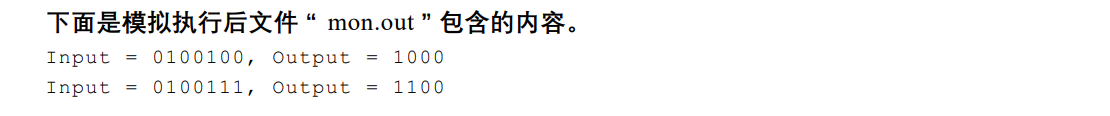

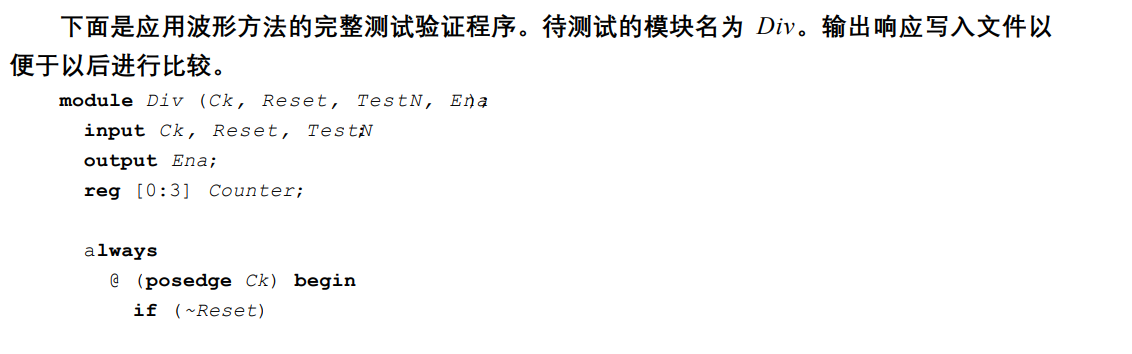

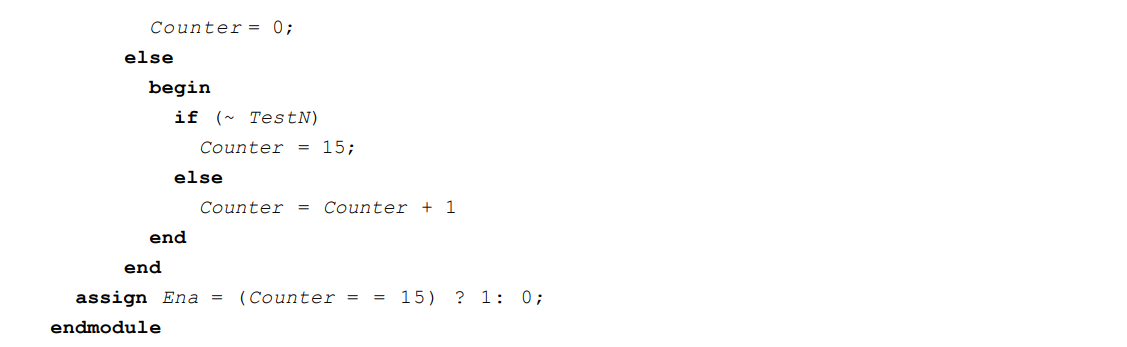

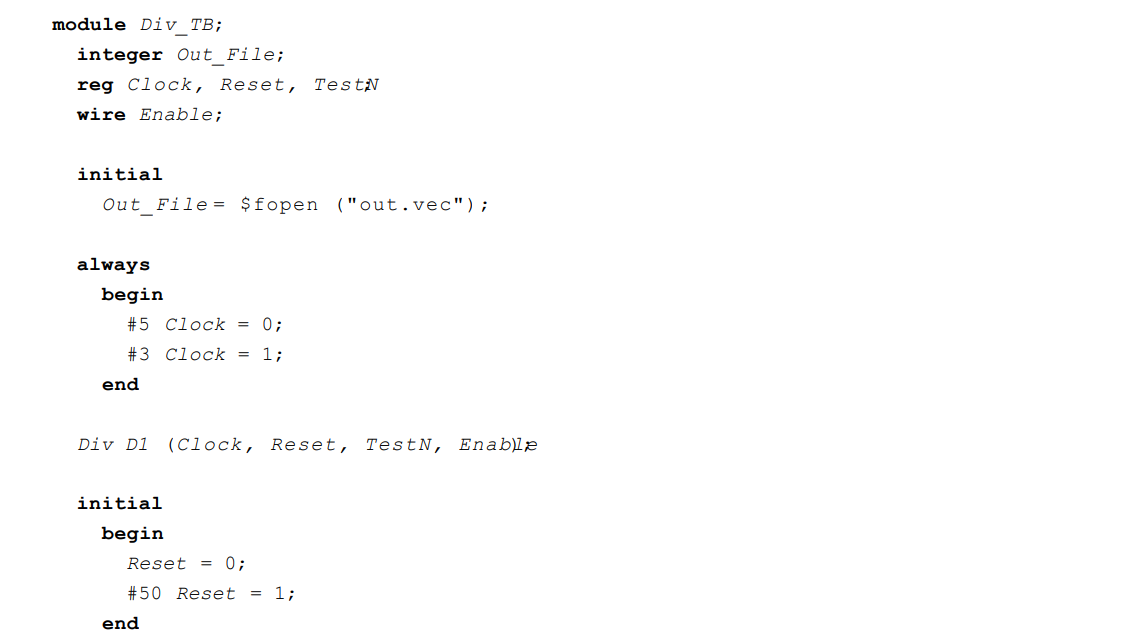

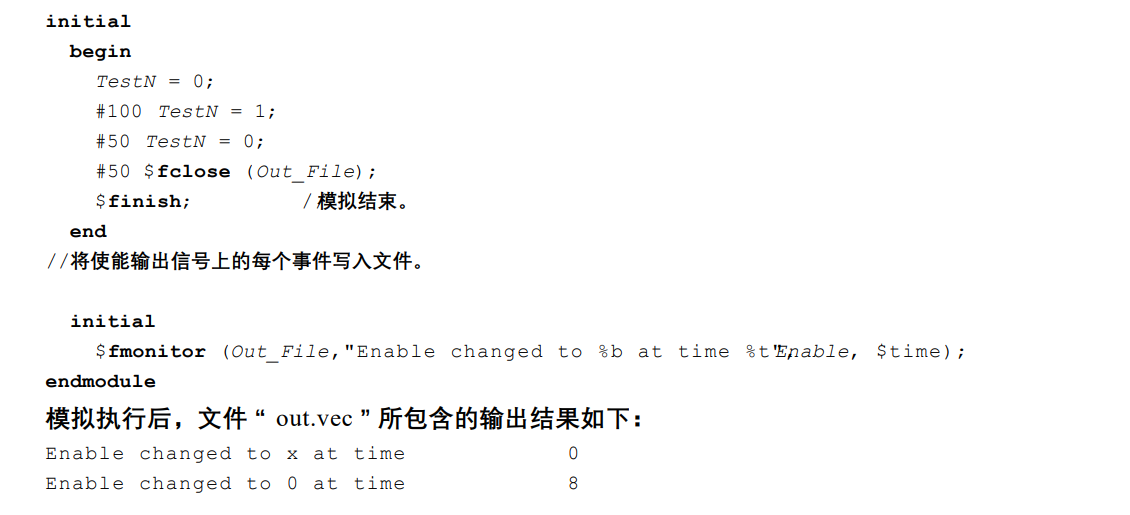

11.5 向文本文件中写入向量

$fdisplay $fmonitor $fstrobe

11.6 其他实例

11.6.1 时钟分频器

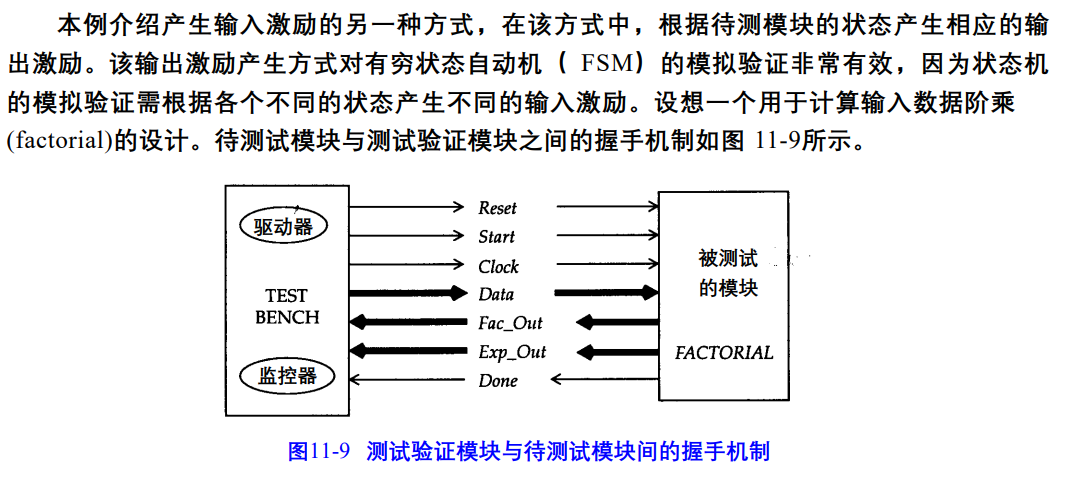

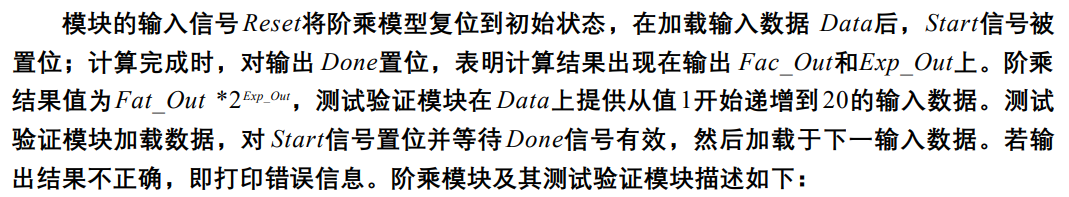

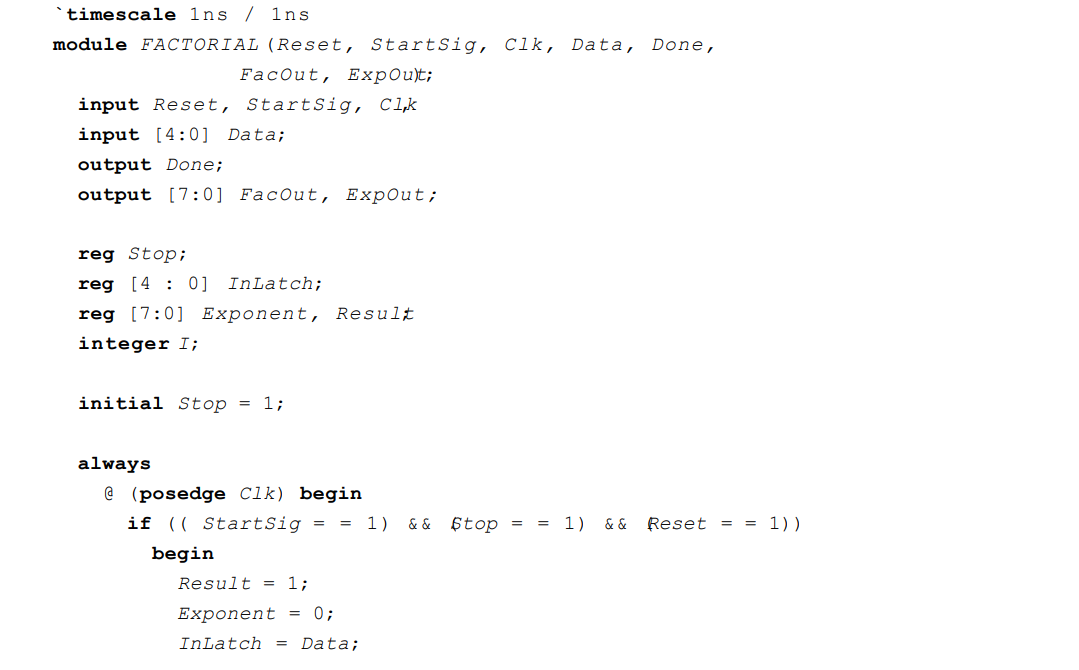

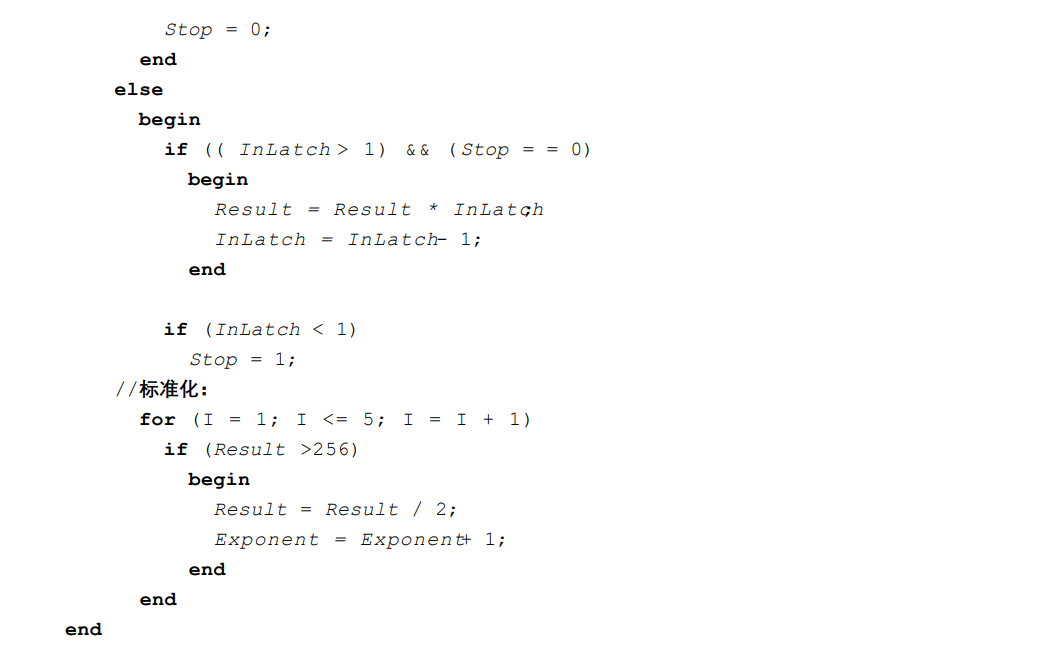

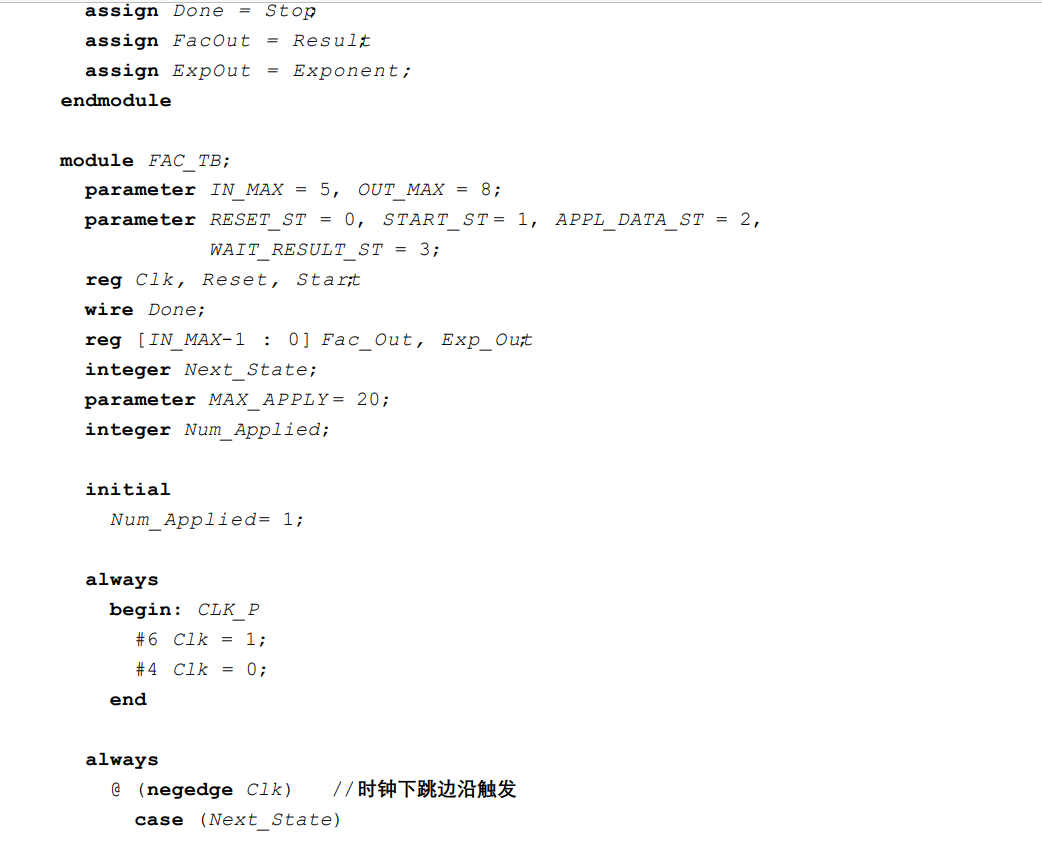

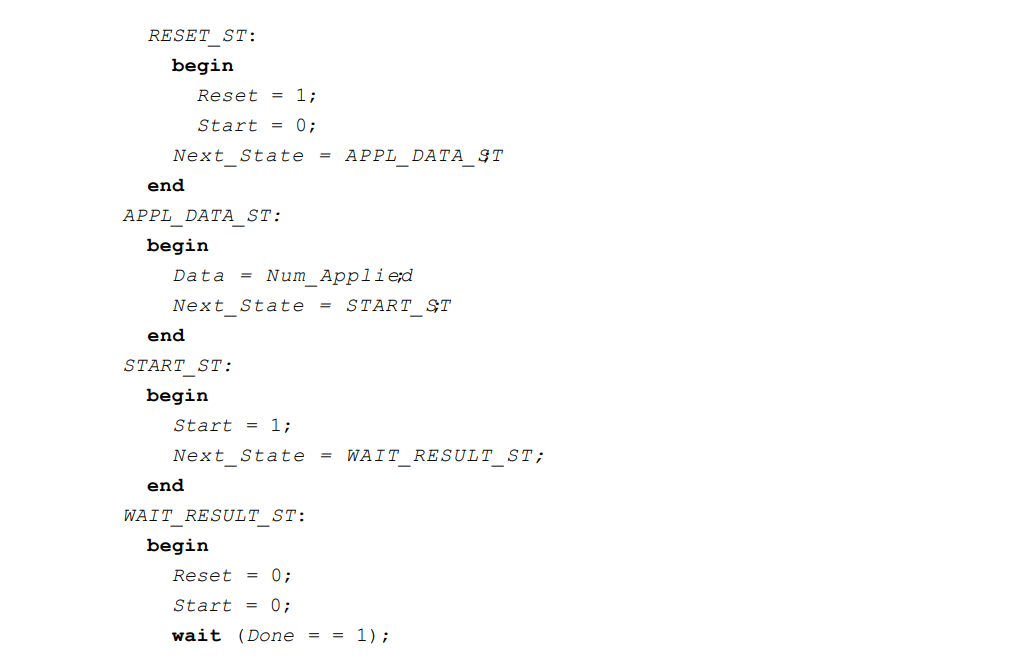

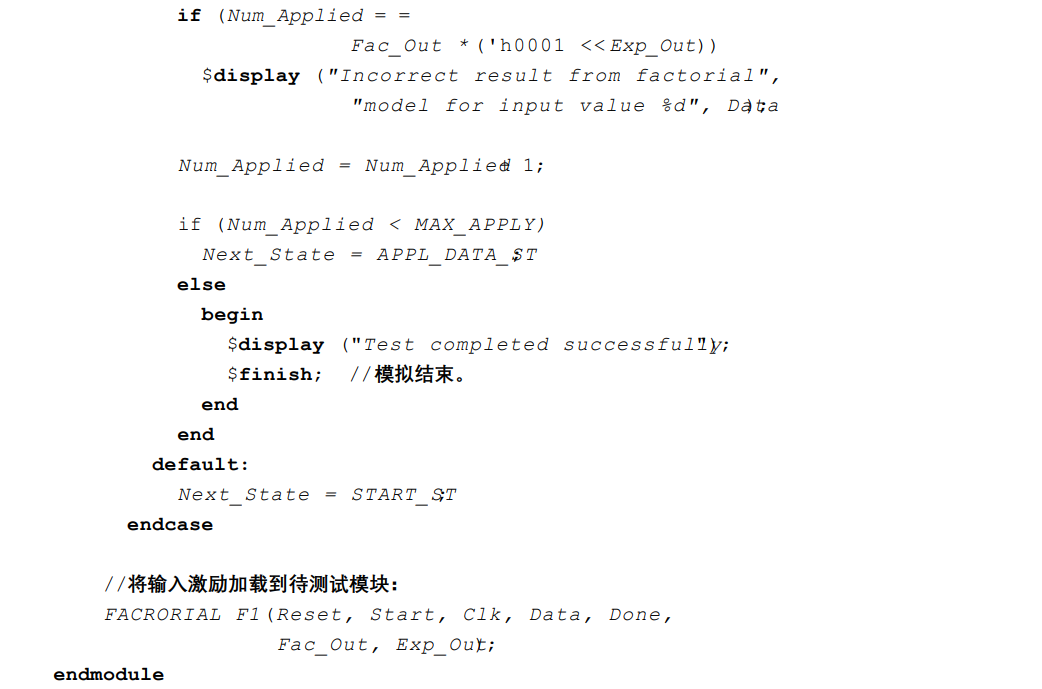

11.6.2 阶乘设计

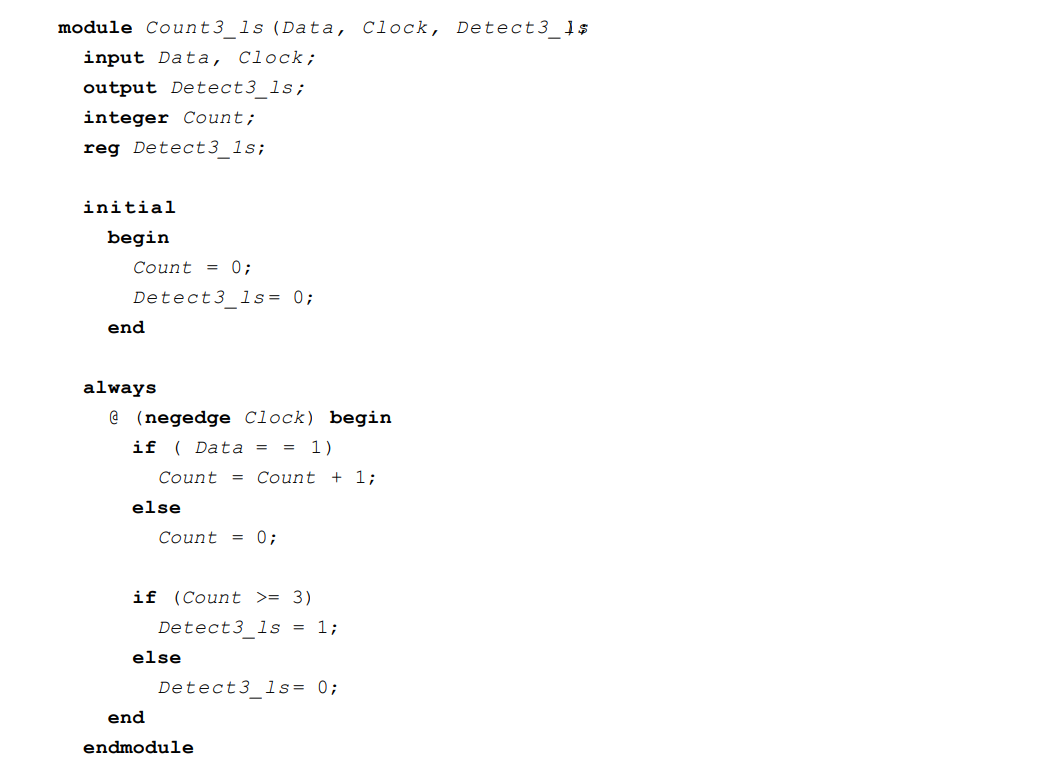

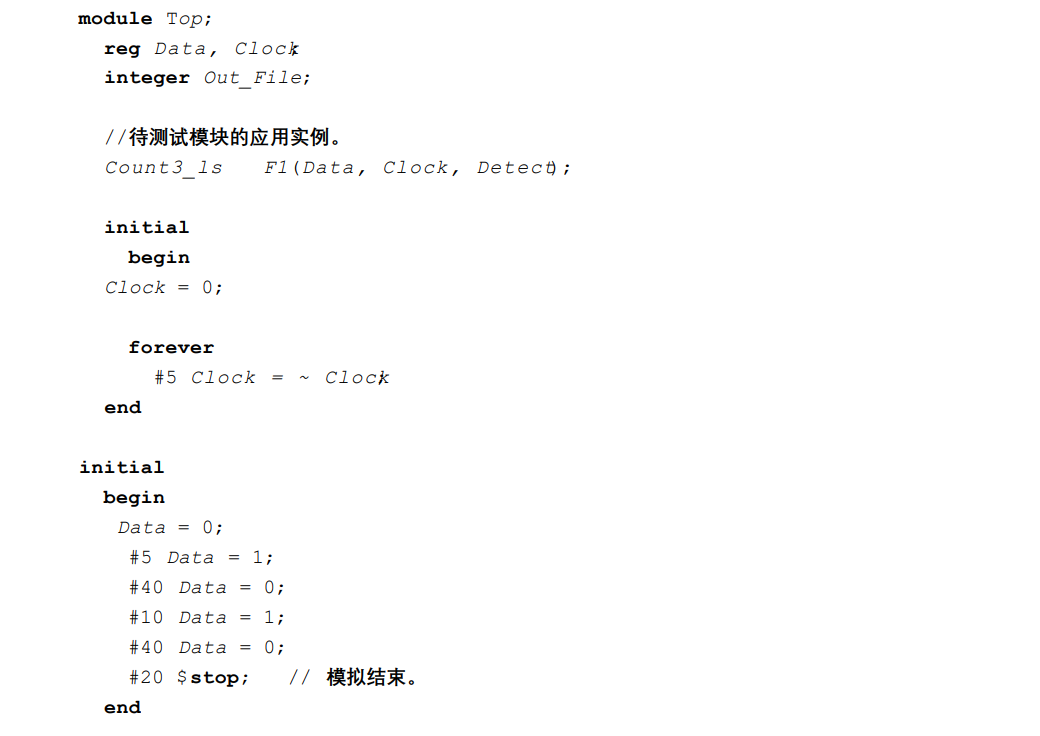

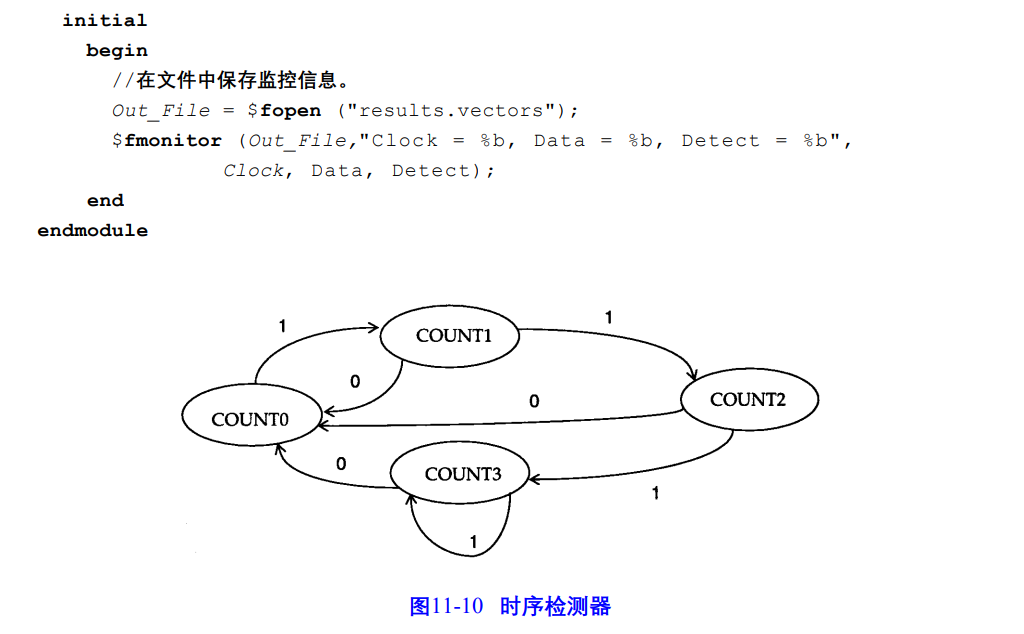

11.6.3 时序检测器

下面是时序检测器的模型。模型用于检测数据线上连续三个 1的序列。在时钟的每个下沿

检查数据。图11 - 1 0列出了相应的状态图。带有测试验证模块的模型描述如下:

645

645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?