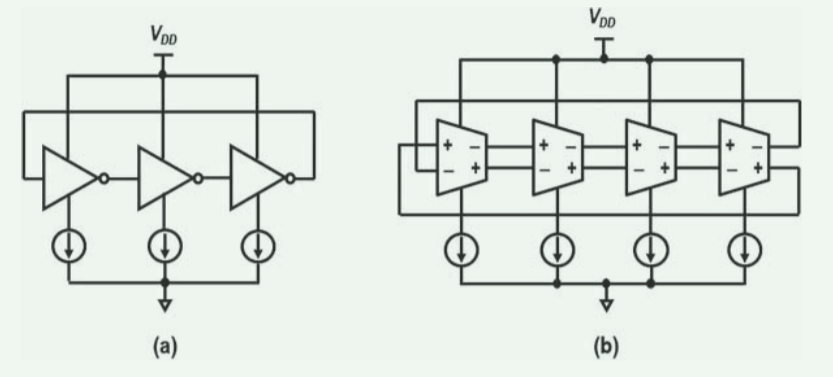

如果三个反相器串联,最后一个反相器的输出反馈到第一个反相器的输入,由于亚稳定性,每个反相器的输出在逻辑1和逻辑0之间切换。

环形振荡器可以被理解为产生切换输出的参数稳定反馈,但通过考虑反相器的小信号增益以及每一级的相位延迟量,奈奎斯特准则或巴克豪森准则仍然可以应用于环形振荡器。

.通常,如果反相器的数量是奇数并且不小于3,则振荡频率fosc:

:反相器的数量

:反相器延迟时间

反省其延迟时间可以通过测量基于反相器的振荡器(即环形振荡器)的振荡频率来简单地估计。

环形振荡器一直是一种流行的测试工具,用于测量反相器或其他数字门的门延迟时间。

随着差分环压控振荡器(VCO)的发展,PLL的电源抑制性能得到了显著的改善,PLL的应用范围也扩展到了时钟产生和时钟恢复系统中。

当设计差分延迟单元时,通过交换末级和第一级反相器之间连接的极性,环形振荡器可以与偶数个差分反相器一起工作,如图(b)所示。

如果级数是4的倍数,差分环VCO可以产生0 kHz和90 kHz的正交相位,这对于时钟和时钟数据恢复(CDR)应用非常有用。

1. 设计方面

采用了LC谐振电路,所以在相同的功率下,LC压控振荡器的相位噪声比环形压控振荡器低,而频率却高得多。

具有片上电感的LC VCO占据大面积并且遭受窄调谐范围。

大多数有线系统不是采用混合模式或RF CMOS技术实现的,而是采用标准数字CMOS技术实现的,其中没有厚金属选项。此外,标准CMOS技术不能为片上电感器或变容二极管提供良好的模型与硬件相关性。

无电感环形VCO的选择也可能来自成本和设计灵活性,这有时比噪声性能更重要。

由于频率是基于门延迟时间,所以环形VCO显示出宽的调谐范围,不需要精确控制自激频率。

环形压控振荡器的相位噪声很差,可以通过宽带锁相环的开环增益来抑制,宽带锁相环对压控振荡器噪声具有高通滤波特性。

环形VCO的另一个强大功能是多相产生。

利用多相特性的一个流行应用是CDR系统中的数据采样,以放松PLL的速度要求。

例如,如果CDR-PLL设计为4级差分环形VCO,则可以使用环形VCO的四个相位,使用1 GHz四相位时钟对4 Gb/s NRZ数据进行采样。

请注意,使用频率较低的多相位时钟不会放松目标数据速率下的随机抖动要求,相位失配会导致另一个确定性抖动源。

然而,由于振荡频率与每个反相器的延迟时间直接相关,因此环形VCO对PVT变化高度敏感.

宽带锁相环的使用可以改善相位噪声,但其积分相位误差仍远高于LC VCO。这是因为在设计宽带PLL时,噪声带宽也增加了。

随着数据速率超过5 Gb/s,串行I/O链路中的抖动要求变得更加严格,LC VCO成为高频时钟生成系统的自然选择。

在无线系统中,带内相位噪声和带外相位噪声对于满足频谱屏蔽很重要。

因此,环形VCO的使用在无线系统中受到限制。

2. 相位噪声

2.1 单端

环形VCO采用强限压模式工作,单端电路采用轨到轨摆幅,差分电路采用硬限幅摆幅。

- 由于摆幅是由有源电路而不是无源谐振器的品质因数设置的,

- 相位噪声性能主要由直流电源决定,

- 直流电源决定了过零点处上升沿和下降沿的斜率

- 相位噪声的大小并不取决于级数。

- 对于给定的功率,大量的反相器提高了开环增益,也增加了有源晶体管的噪声贡献。

- 增加平均电源电流或电源电压是降低相位噪声的有效途径.

- 反相器的延迟时间决定了振荡频率

- 环形振荡器的相位噪声会受到电源或衬底噪声耦合的严重影响。

- 还有来自控制电压的噪声贡献。

为了推导环形振荡器中反相器的定时不确定性,在反相器的输入端施加一个阶跃输入电压,并在输出端测量一个电压斜坡。

定义传输延迟为输出电流通过VDD/2的时间。

假设电流噪声in的平均值为零,则仅使用NMOS晶体管的平均传播延迟:

C是反相器输出端的负载电容

是NMOS在饱和区的漏极电流

NMOS进入线性区,电流也不会剧烈变化。

方差:

:NMOS的体效应系数

:NMOS的阈值电压

包含PMOS,则周期抖动的方差:

N:反相器的级数

为了简单计算,,

,

,则

N级环形振荡器的输出频率f0:

则:

对于给定的周期抖动方差,单边带相位噪声L(f)表示为

相位噪声可以得到:

,基于简单模型,反相器的数量不会影响相位噪声,并且增加电源或电源电压是设计人员降低相位噪声的唯一选择。

当添加闪烁噪声时,相位噪声方程变为

:是栅氧电容

:NMOS(PMOS)电子迁移率

:NMOS(PMOS)晶体管参数

:NMOS(PMOS)的栅长度

与其他电路一样,使用较长的栅极长度有利于降低闪烁噪声,

但会因负载电容增加而降低上升沿和下降沿的斜率。

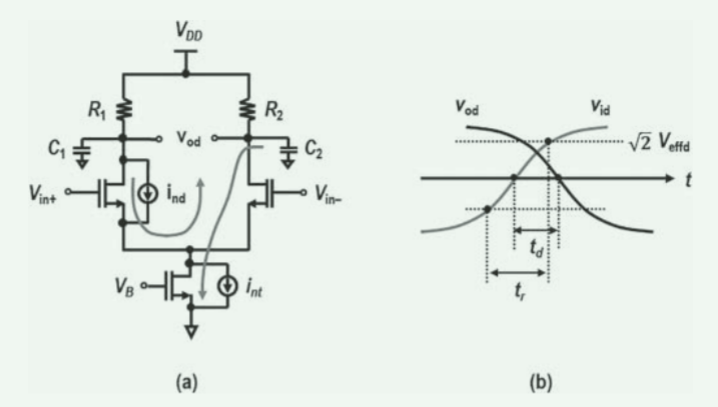

2.2 差分

- 单端环形VCO对电源噪声太敏感

- 差分环形VCO主要用于集成PLL电路的设计

需要额外的电路来在不同的偏置电流下保持恒定的输出幅度。

否则,差分环形振荡器的输出频率遭受非常窄的调谐范围,

随着偏置电流增加而增加的输出摆幅会降低振荡频率。

单端Ring VCO比具有辅助环路差分Ring VCO噪声性能差。

假设差分幅度恒定(,偏置电流、负载电阻)。在RC负载,衰减指数

:

抖动方差:

:差分对的有效栅极电压

:尾晶体管的有效栅极电压

为了在下一级中完全引导差分输入对的电流,Vop需要满足

周期抖动方差的单边带相位噪声:

闪烁噪声对相位噪声的影响:

来自差分对的白色噪声 + 来自尾部晶体管的闪烁噪声 = 总相位噪声。

闪烁噪声比白色噪声更占主导地位。

对于单端和差分环压控振荡器,提高平均功率是降低相位噪声的最有效方法

3. 电路实现

环形压控振荡器的性能受电路拓扑结构的影响很大,因此可以根据不同的设计要求来考虑各种结构。

- 相位噪声

- 短时抖动

- 功耗

- 工作电压

- 电源抑制

- 多相产生

- 工作速度

压控延迟线(VCDL)是环形压控振荡器设计的关键组成部分

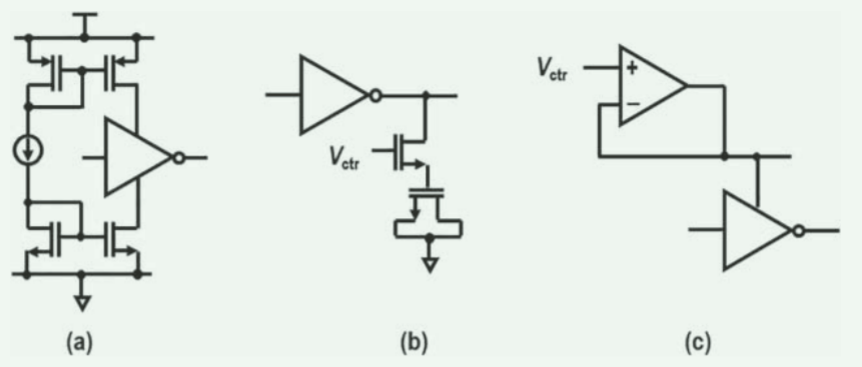

3.1 单端VCDL

| (a) | (b) | (c) | |

| 延迟时间控制方式 | 电流控制 电流饥饿型VCD | 电容控制 | 电压控制 |

| 控制方式 | 频率随着电流的减小 从最大频率开始降低 | 每一级的延迟时间随控制电压的增加而增加 | 直接改变反相器的电源电压 |

| 尾电流是通过电流镜而不是栅极电压来控制的 并且需要电压-电流转换器 | 单端压控振荡器由于对电源电压变化的高度敏感性,很少用于超大规模集成电路系统中 |

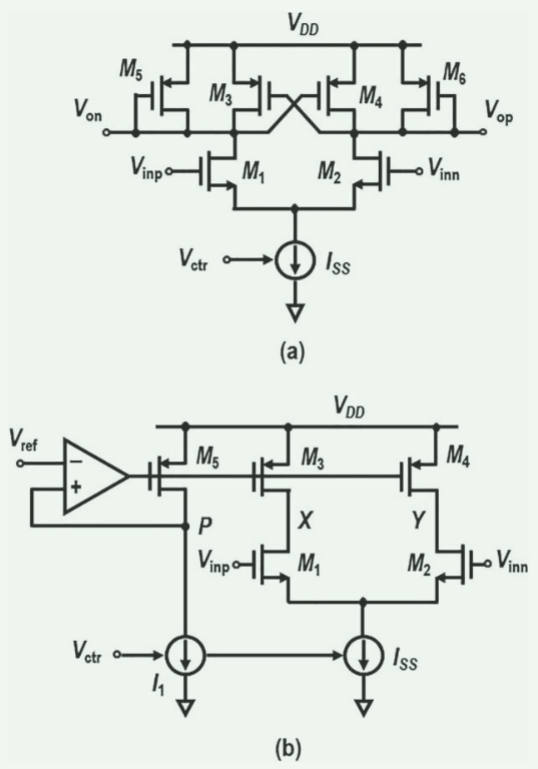

3.2 全差分VCDL

具有电阻负载的差分环形VCO的调谐范围非常窄,

因为输出摆幅的幅度几乎与偏置电流的值成比例。

为了限制电压摆动,使用有源负载。

| (a) | (b) | |

| 使用PMOS二极管作为负载来限制电压摆幅 | 用线性区PMOS和复制偏置控制提供线性电压频率控制 | |

| 问题 | 栅极-源极电压严重依赖于工艺和温度变化 由于MOSFET固有的平方律特性,难以进行线性电压频率控制 |

(b)用线性区PMOS和复制偏置控制提供线性电压频率控制

线性区域PMOS表现为压控电阻器,电阻可以通过栅极电压改变。

假设环形振荡器具有硬极限摆幅。当M1导通而M2截止时,节点X和Y处的输出电压VX和VY:

线性模式M3的有效负载电阻RL3:

- 即M1完全导通,并将VP设置为由反馈电路提供的参考电压。

- 如果Itail增大,则M1的电阻通过反馈而减小,以使VP不变。

- 在复制电路中,当M1完全导通时,VX与VP相同。

- 环形振荡器的输出摆幅为:(VDD − Vref)至VDD。

振荡频率为:

α:考虑电路延迟的影响的缩放参数

输出频率由尾电流线性控制。

为了改善电源抑制,可以设计一个带NMOS负载的PMOS输入对,而不是NMOS输入对,使环形VCO的输出摆幅以地为基准。

- 具有有源负载的差分VCDL难以实现快速,因为有源负载增加了大量的寄生电容。

- 此外,当VCO以非常高的频率工作时,输出摆幅的上升和下降时间会发生摆动。

- 因此,通过改变有源负载的电阻来控制输出频率是困难的。

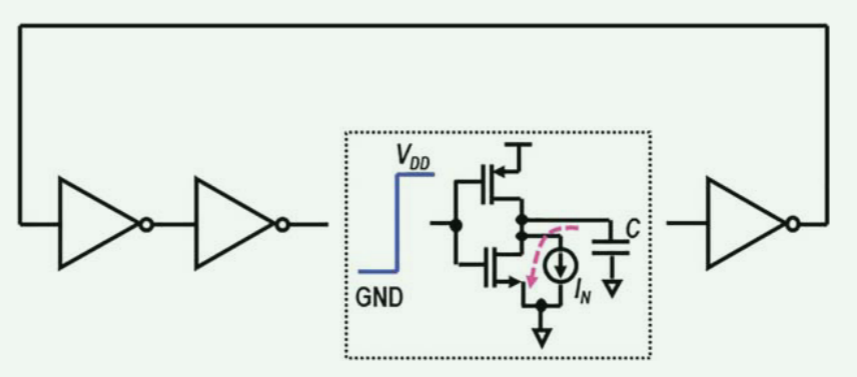

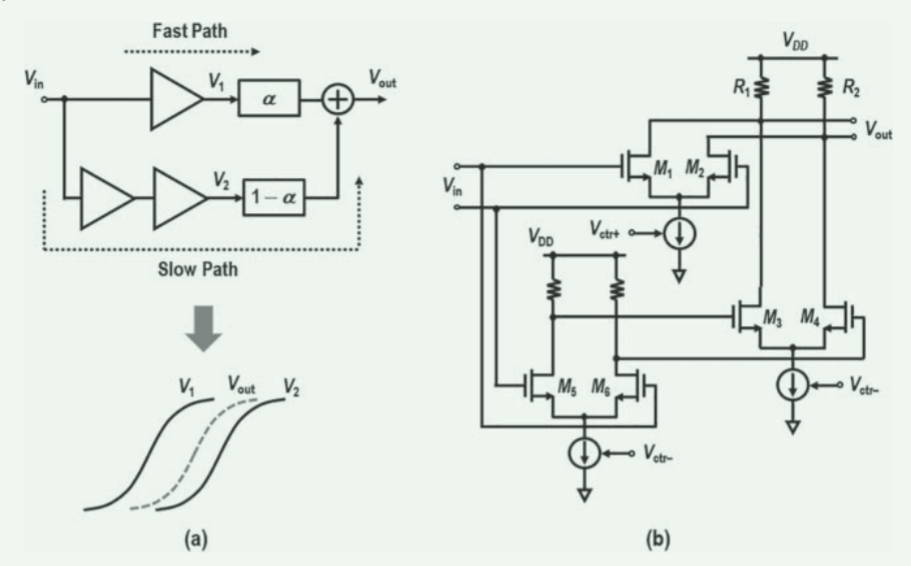

上图显示了另一种用于高频工作的差分VCDL。

- 对原始正弦信号和延迟正弦信号进行平均求和时,生成内插相位。

- 如果总电流不变,则求和信号的幅度保持不变。

- 通过改变两个信号路径,即快速路径和慢速路径的加权比,实现了基于相位插值的相位控制,如图(a)所示。

- 对于平滑相位插值,慢路径中的相位延迟量不应超过快路径信号的90 °。

- 由于可变延迟是在电压域中通过使用带电阻负载的电流导引放大器来实现的,如图(b)所示,所以在高频时可以实现线性频率控制。

- 相位内插VCDL遭受窄调谐范围,除非多相输入才可用。

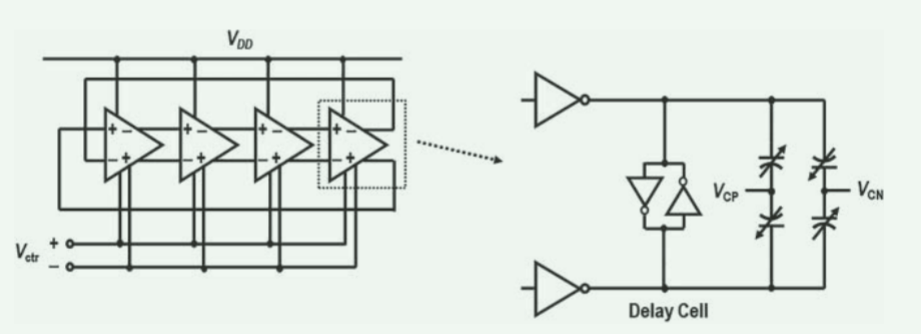

3.3 伪差分VCDL

偏置电流的使用使得差分环形VCO难以实现紧凑、低功率或低电压设计。

- 如图所示的伪差分VCDL,紧凑的面积和低功耗,适合中速工作。

- 利用轨到轨摆幅和正反馈锁存器,可获得快速上升和下降时间,从而实现低噪声性能。

- 伪差分拓扑结构使偶数延迟单元成为可能。

- 通过具有可变电容性负载来实现可变延迟。

- 类似于LC VCO设计中的电容器阵列,每个延迟单元的输出节点处的开关电容器阵列也可以用于提供粗调谐,而细调谐由通过变容二极管的控制电压完成。

- 控制延迟时间的另一种方式是在反相器的电源节点处具有数控电阻阵列

- 即使对于伪差分反相器,栅极延迟时间也高度依赖于电源电压

4168

4168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?