一.WPE效应分析

1.什么是WPE效应

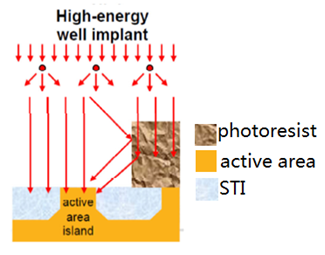

WPE=Well Proximity Effect,阱临近效应。在先进 COMS 工艺中,阱是通过高能将离子注入硅晶圆上,由光阻材料控制形成的硅晶圆上的注入区域形成的。在高能离子注入生成阱区域时,部分注入离子会从光阻材料的侧面散射到阱区域,使得阱边缘的离子浓度发生变化,见下图。

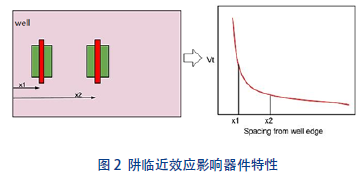

在 N 型阱和 P 型阱边缘,阱离子注入掺杂(施主或者受主)MOSFET 沟道的掺杂是同一类型,额外的散射离子会增加沟道浓度,从而使得 N-MOSFET和 P-MOSFET 的阈值电压变高。一般来说相同尺寸的MOSFET 距离阱边缘的距离越近,其阈值电压变化越明显。[2]

离子的散射量和阱边缘的距离相关,一般来讲有效区域为 2 μm 甚至更大的区域。

2.实验验证

2.1实验验证

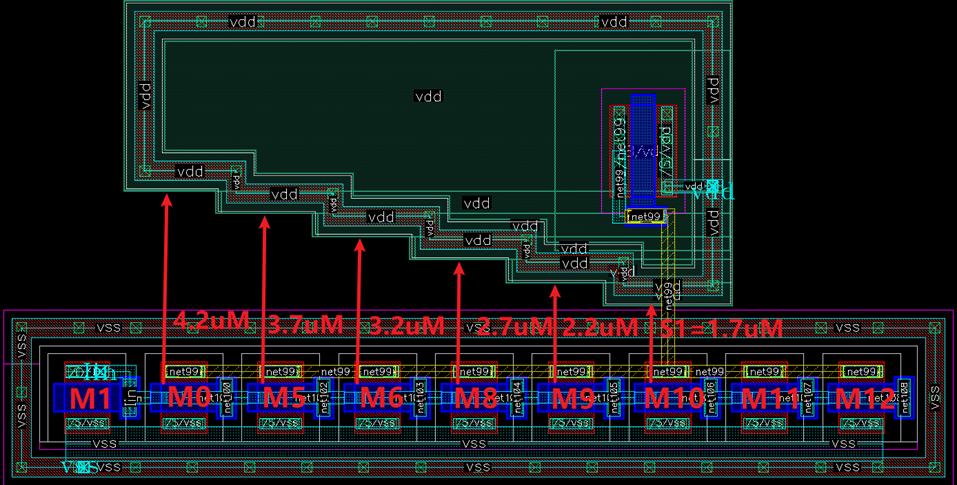

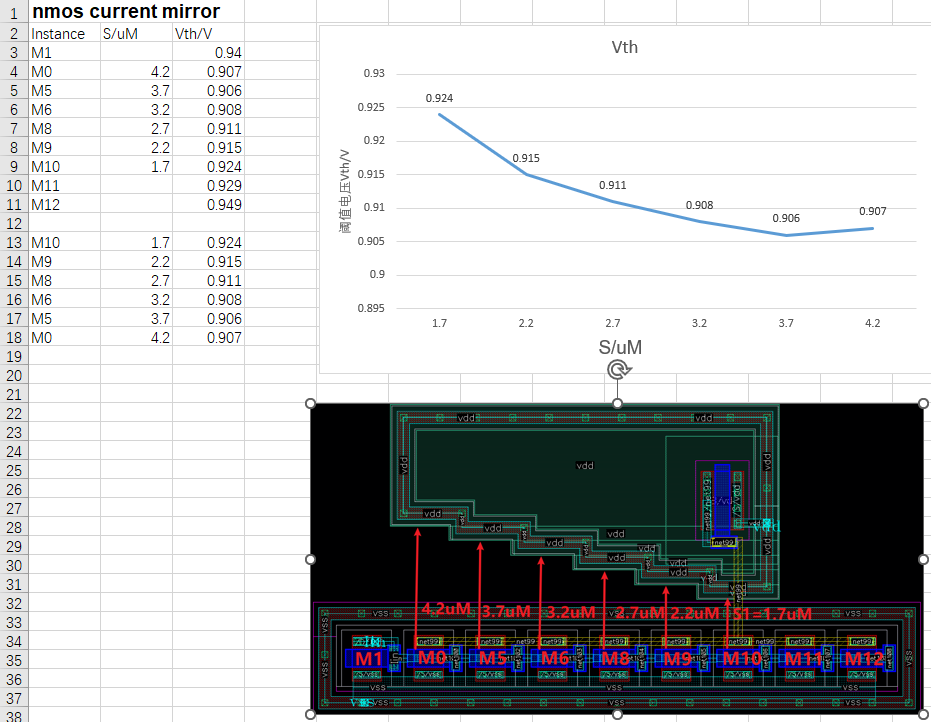

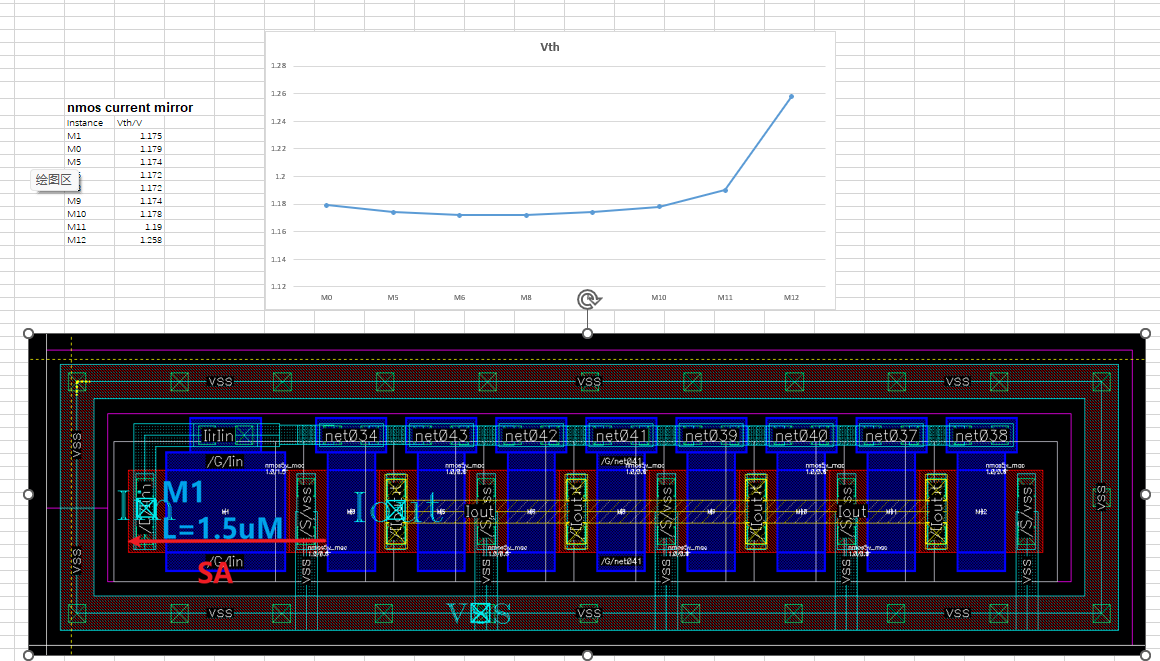

首先设计实验验证WPE效应的时候,应该要考虑到STI效应。这里将nmos管并排放置,对于上图中的M0-M10而言,可认为它们所受STI的影响一致。

然后设置nmos管到NWELL的间距,这里以0.5uM为间隔,设置了从1.7uM—4.2uM。

2.2DC仿真

从实验数据可以看出,距离最近的管子的阈值电压和距离最远的管子阈值电压相差了17mV。

在3.2uM以内的nmos管阈值电压受影响比较大,而当距离超过了3.2uM后,基本可以认为阈值电压变化基本不受影响。

3.结论

为减少WPE效应影响,可以通过添加dummy的方式使得nmos管到阱边缘距离至少大于3.2uM。

二.LOD效应分析

1.什么是LOD效应

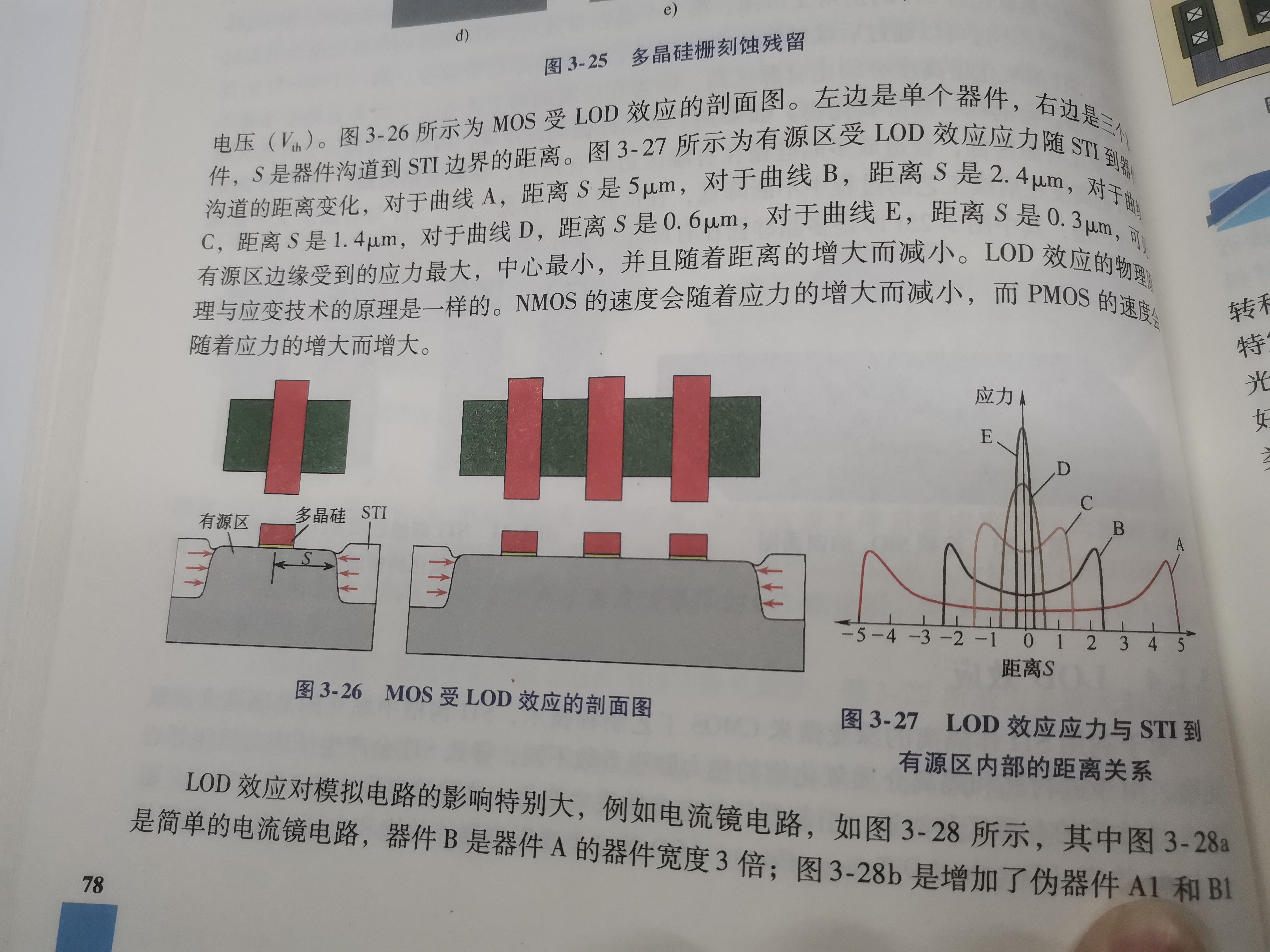

STI是Shallow Trench Isolation的缩写,STI压力效应就是LOD效应。

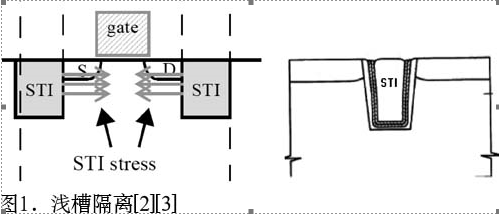

为了完成有源器件的隔离,在它周围必须形成绝缘侧壁,在较为先进的CMOS工艺制成中,通常用STI的方法来做隔离。浅槽隔离利用高度各向异性反应离子刻蚀在表面切出了一个几乎垂直的凹槽。该凹槽的侧壁被氧化,然后淀积多晶硅填满凹槽的剩余部分。

在substrate挖出浅槽时会产生压力的问题。由于扩散区到MOS管的距离不同,压力对MOS管的影响也不同。所以对于相同长宽两个MOS管,由于对应的扩散区长度的不同而造成器件性能的不同。[1]

2.如何减轻LOD效应

增加有效器件栅极到STI的距离。

3.实验验证

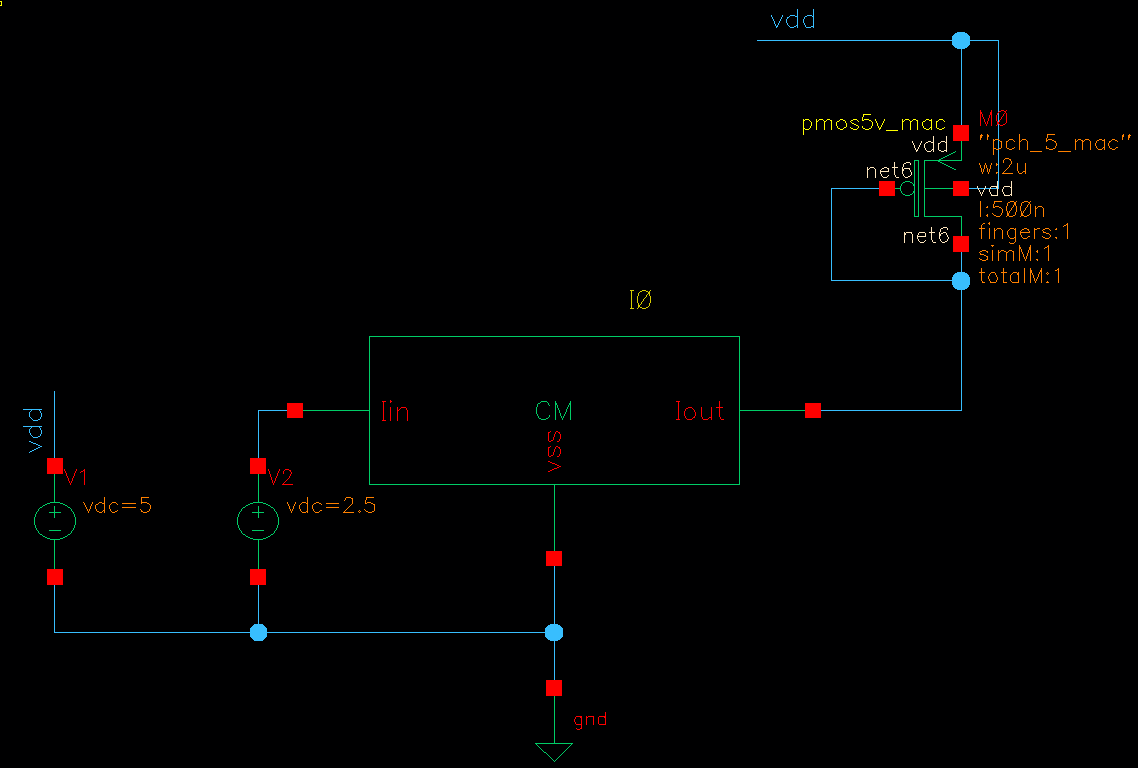

下面用简单的电流镜电路,来研究LOD效应对管子产生的影响。

3.1实验一

其中所有nmos管的尺寸都采用最小比例2u/0.6u。

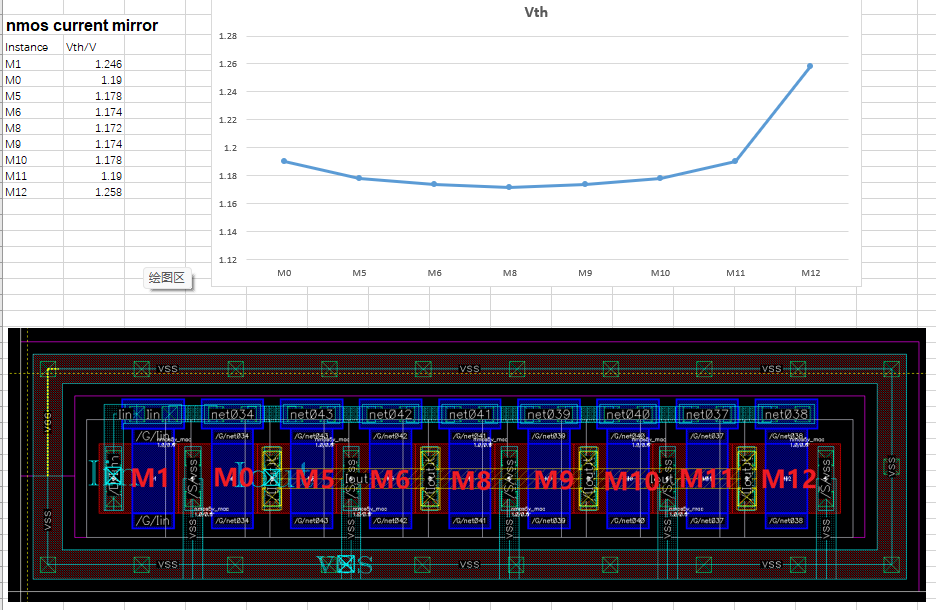

根据仿真结果,nmos管的Vth分布呈现两头高中间低的特点。

这也符合对对LOD效应的预期,即越靠近STI,则有源区长度受影响越明显,反之则是离得越远所受影响越小。

那么为了削弱LOD效应带来的影响以及增加电路匹配度,应该加上多长的dummy呢?

3.2实验二

以位于中心的M8为基准,M0和M5的Vth分别相差1.5%和0.5%。当中M0栅到STI的距离约为1.5u,M5栅到STI的距离约为2.5u。

这里选择改变M1的length至1.5u,相当于增大M0到sti的距离SA,其他条件不变。

从仿真结果可以看出,当SA增大为1.5u,M0的阈值Vth相较于M8/M9管的Vth差别变为0.26%。

4.结论

在对电路匹配要求比较高的地方,为了减轻LOD效应的影响,可以在电路两边增加dummy(最小Length应该为1.5uM)从而达到增加匹配性的目的。

参考资料

1.《深亚微米IP模块设计中必须考虑的制造工艺的影响》 马莹,李章全

2.《一种提高 WPE 在仿真中准确性的方法》 杜浪,黄其煜

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?