Chisel入门——在windows系统下部署Chisel环境并点亮FPGA小灯等实验

一、chisel简介

传统数字芯片的RTL设计采用Verilog语言为主,Chisel语言的全称是Constructing Harward in Scala Embeded Language,即在Scala语言中导入Chisel3库,即可使用Chisel语言。其特点是面向对象编程,可以方便地参数化定制硬件电路,加快设计流程。目前在RISC-V生态中应用较多,中科院计算所主持的培育下一代处理器设计人才的“一生一芯”项目也在极力推进该语言。

Chisel是一个Scala库,用于构建高级别的、可综合的、模块化的硬件设计。它允许设计师在高层次上定义硬件的行为,然后通过一系列的转换步骤将其转换为低层次的Verilog或VHDL代码。这使得设计师可以专注于实现硬件的功能,而不需要关心底层的细节。

Chisel的主要特点包括:

高级抽象:使用Scala的高级别抽象来描述硬件行为。

可综合:生成的Verilog或VHDL代码可以直接用于ASIC或FPGA的设计。

模块化:可以将设计分解为多个独立的模块,每个模块都可以独立地进行测试和验证。

交互式开发:可以在Scala REPL中直接运行Chisel代码,以便于调试和验证。

为什么要提出Chisel?

Chisel的设计者们是这么说的(以下翻译自官网Motivation – “Why Chisel?”):

在我们的科研项目和硬件设计课程中,与现有硬件描述语言进行了多年的斗争,这促使我们开发一种新的硬件语言。Verilog和VHDL是作为硬件仿真语言开发的,直到后来它们才成为硬件综合的基础。这些语言的大部分语义不适用于硬件综合,事实上,许多结构都无法综合。其他结构在他们如何映射到硬件实现是很不直观的,或者说他们的使用可能会意外地导致非常低效的硬件结构。虽然可以使用这些语言的子集并且还能得到可以接受的效果,但它们仍然呈现出混乱和令人困惑的规范模型,特别是在教学环境中。

然而,我们开发新硬件语言的最强烈动机是我们希望改变电子系统设计的方式。我们认为,重要的是不仅要教学生如何设计电路,还要教他们如何设计电路生成器——从高级设计参数和约束自动生成设计的程序。通过电路生成器,我们希望利用设计专家的辛勤工作,为大家提高设计抽象水平。为了表达灵活和可拓展的电路结构,电路生成器必须采用复杂的编程技术来确定如何根据高级参数值和约束更好地定制其输出电路。虽然Verilog和VHDL包含一些用于编程电路生成的原始结构,但它们缺乏现代编程语言中的强大功能,例如面向对象编程、类型推断、对函数式编程的支持以及反射等。

我们没有从头开始构建新的硬件设计语言,而是选择在现有语言中嵌入硬件构造原语,我们选择Scala不仅是因为它包含我们认为对于构建电路生成器很重要的编程特性,还因为它是专门作为特定领域语言(DSL)的基础而开发的。

这里只做简单的介绍:更多资料可以查看以下链接

链接: link

二、vscode搭建scala开发环境

2.1 安装Scala官方插件

在VS Code中安装插件,先安装 Scala Syntax (official),再安装 Scala (Metals):

第一个和第二个都需要安装

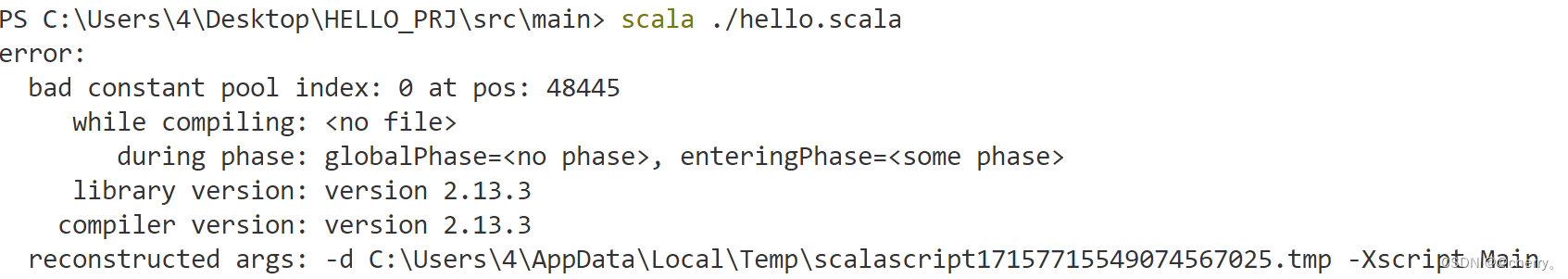

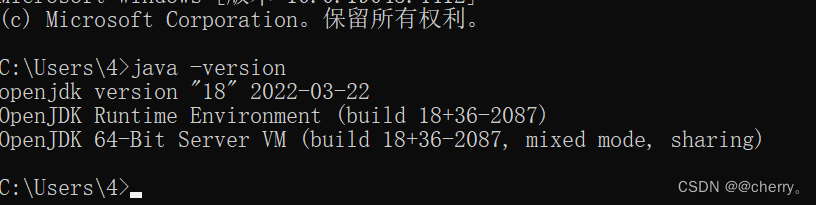

2.2 java版本(本人用的是jdk18)

注意可能部分jdk不适配

直接打开终端,输入

java -version

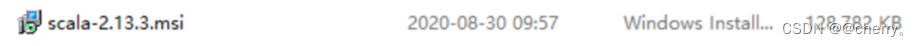

2.3 下载Scala Windows版本的二进制文件

下载链接:link

然后一直点击next即可

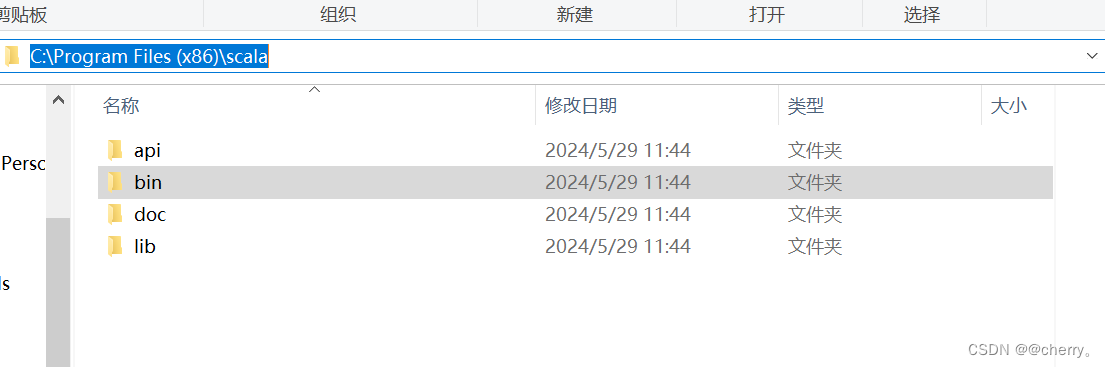

注意需要记得安装的路径

2.4 配置环境变量

1、变量值即为安装的路径

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3323

3323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?