一、在Logisim上采用74LS00芯片设计RS触发器

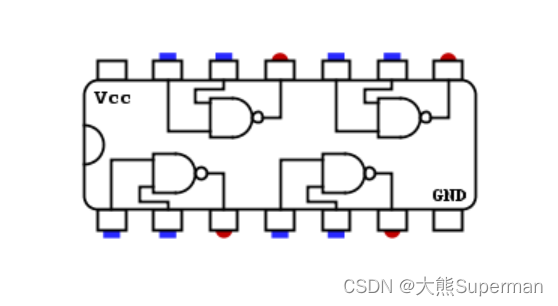

74LS00芯片是由四个二端输入与非门组合形成的元器件,其电路如图:

RS触发器也叫RS锁存器,有些地方也把它叫做SR触发器或者SR锁存器,它是时序电路中最基础的存在。我们可以简单地将它理解为一个存储单元,可以用来储存一位数据及0或者1。RS触发器可以用两个与非门或者或非门实现。

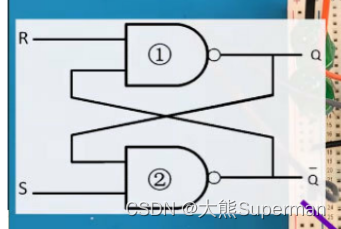

两个与非门实现RS触发器电路如图:

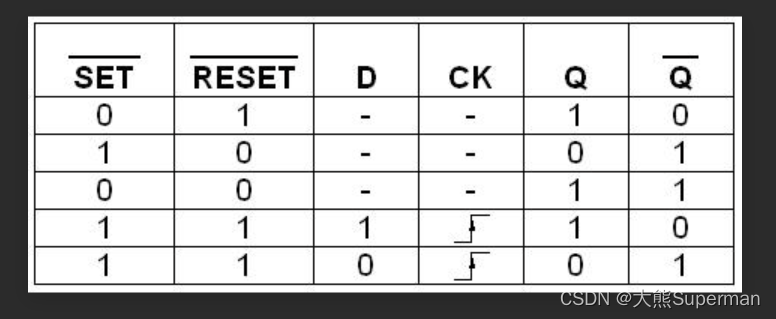

对于与非门实现的RS触发器,其特征变如图:

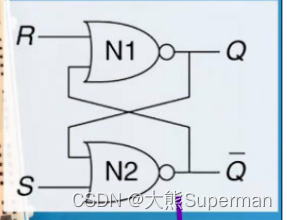

两个或非门实现RS触发器电路如图:

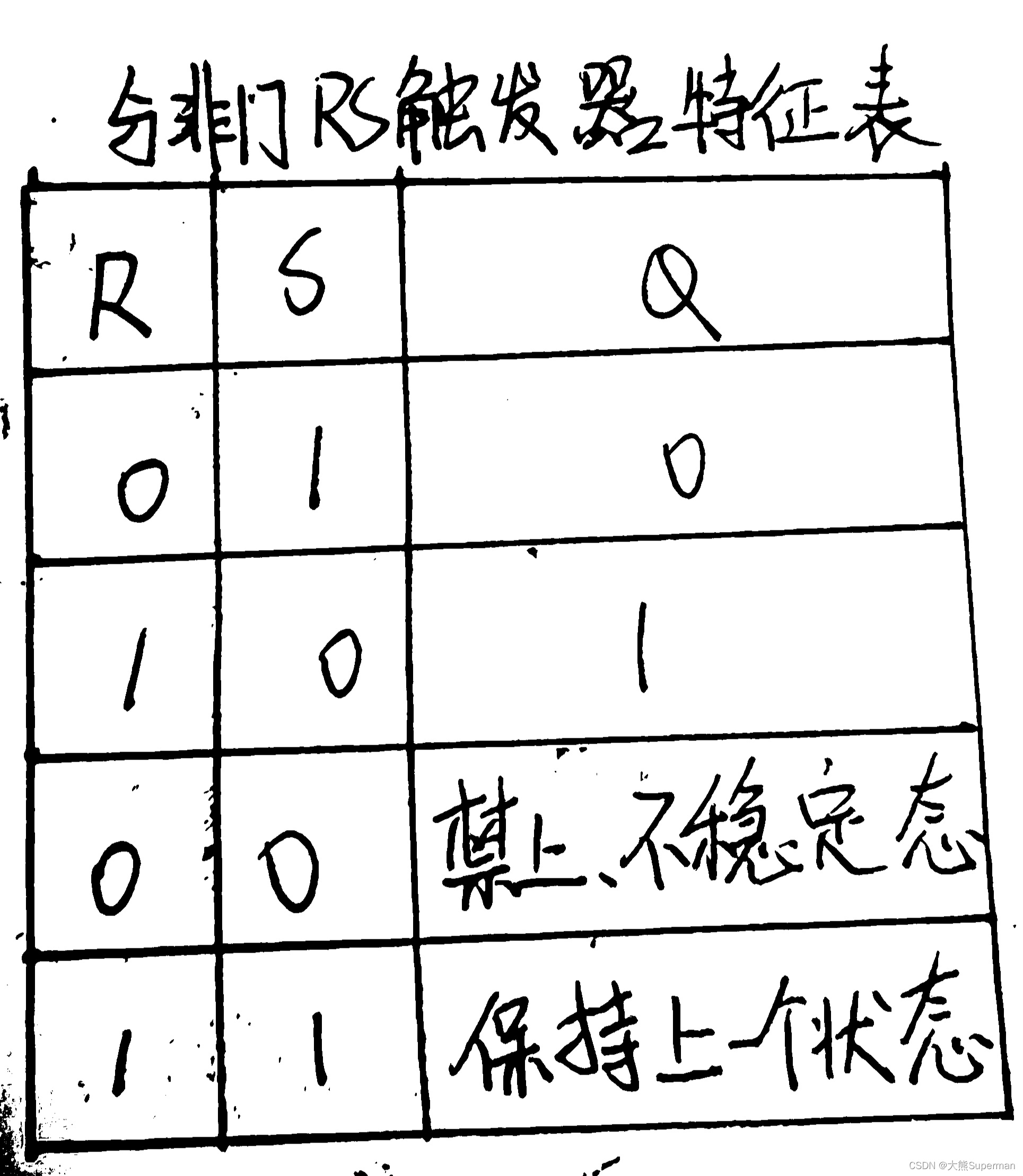

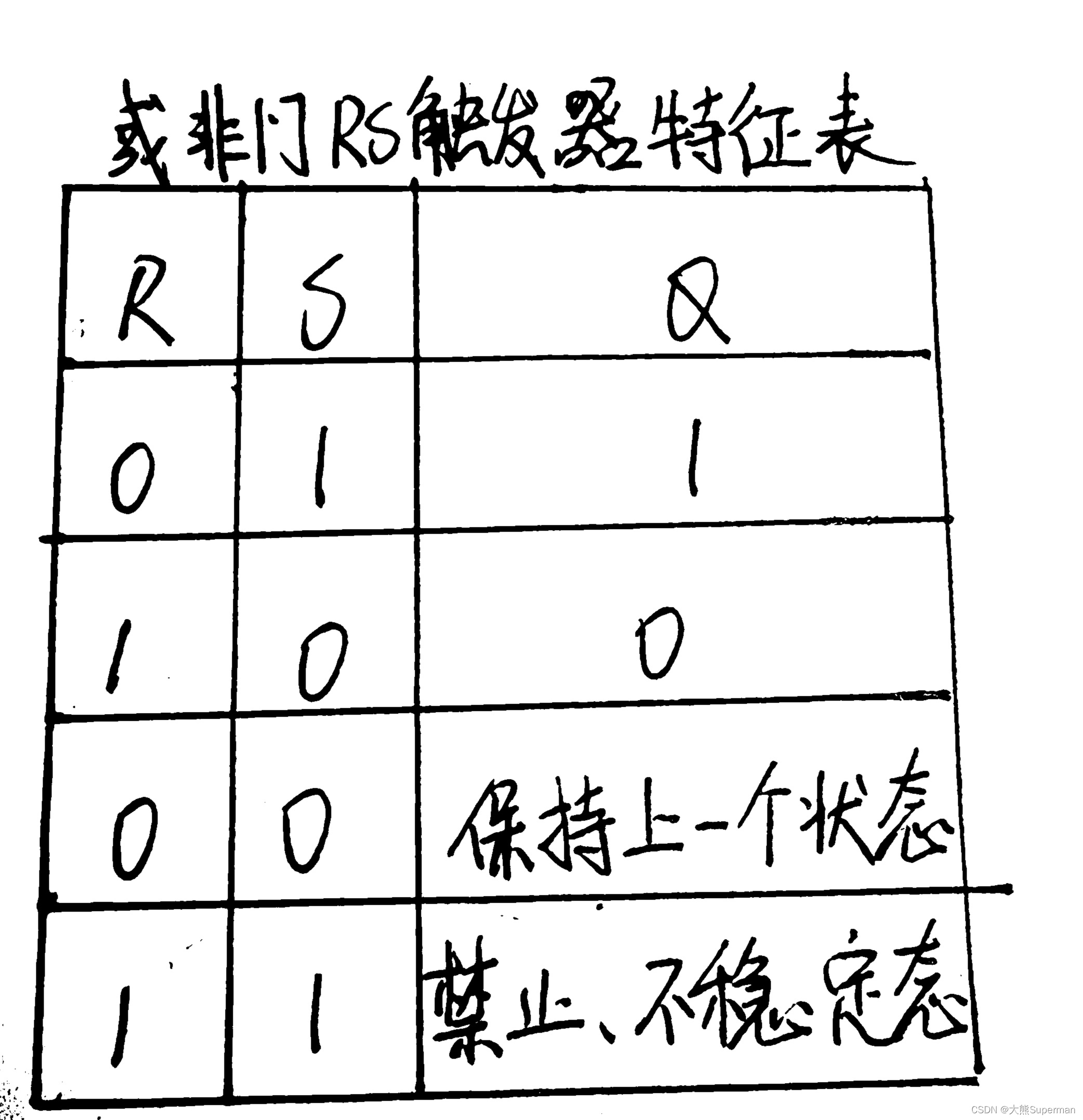

对于或非门实现的RS触发器,其特征变如图:

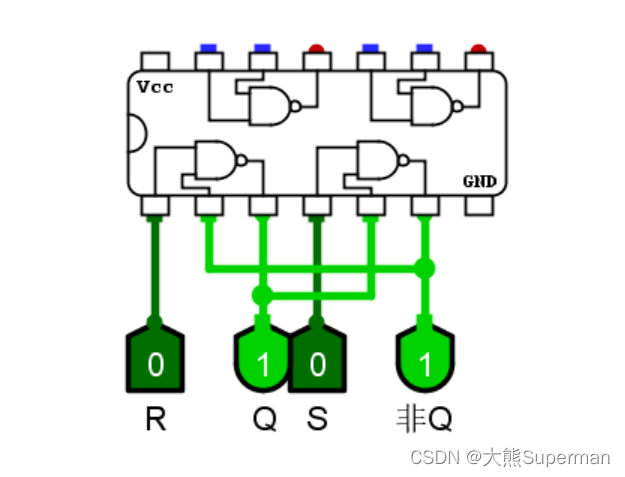

在Logisim上采用74LS00芯片中的两个与非门实现RS触发器电路,其电路如图:

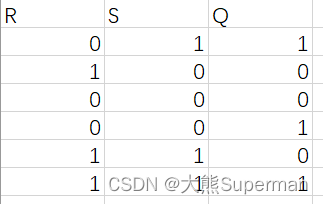

其真值表如图所示:

当R和S都为0时,Q有两个值,这体现了保持上一个状态的特性,及当R和S都为0时,上一个状态可能为0也可能为 1。当R和S都为1时,Q也有两个状态,这体现的不稳定态这个特性,及当R和S都变为1时,Q可能变成0也可能变成1。

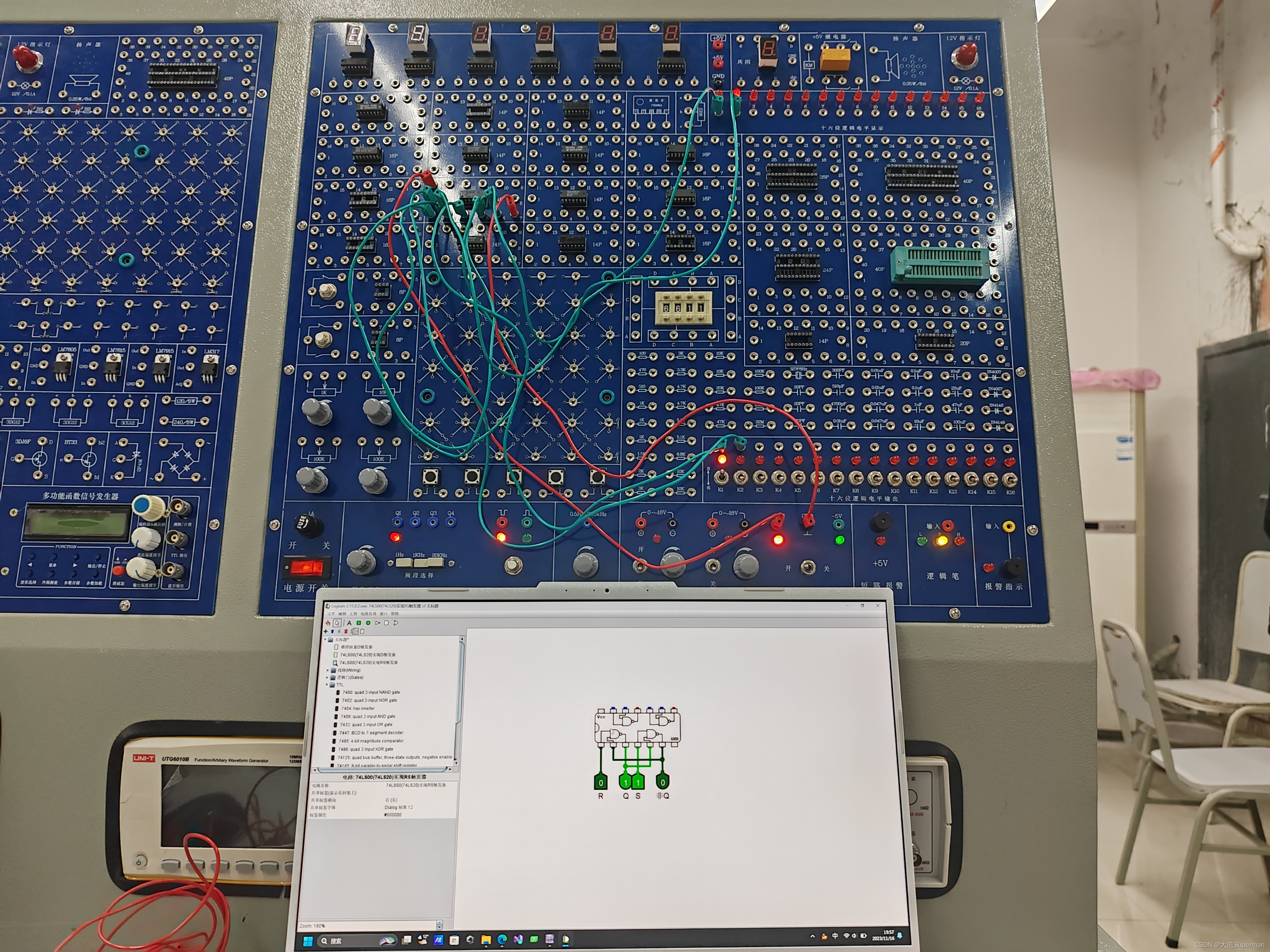

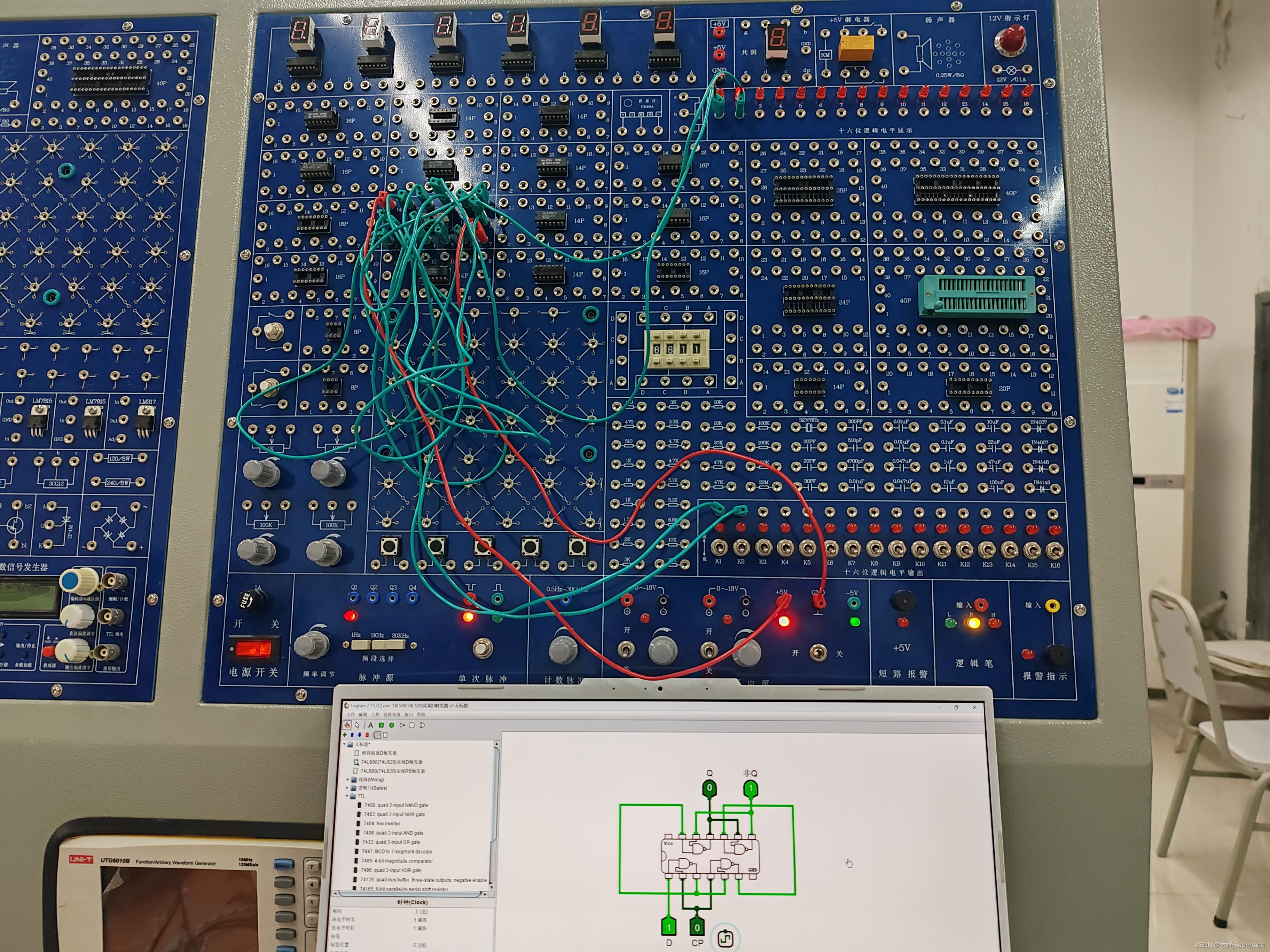

用74LS00硬件来实现RS触发器,其实际电路如图:

二、在Logisim上采用74LS00芯片设计D触发器

D触发器也叫D锁存器,D触发器实际上是在RS触发器的基础上加上一个控制们。这里我们以用与非门来实现D触发器为例。

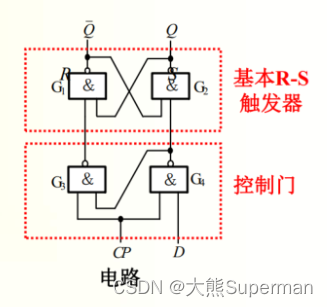

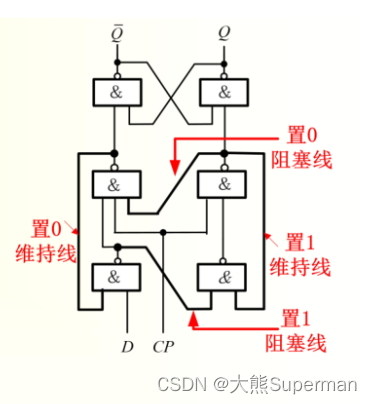

对于与非门实现的D触发器电路如图:

对于与非门实现的D触发器,其工作原理如图:

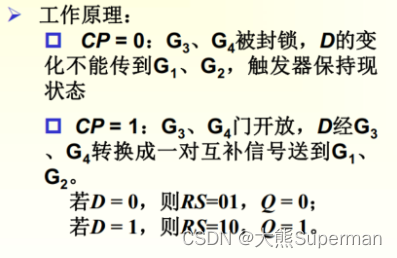

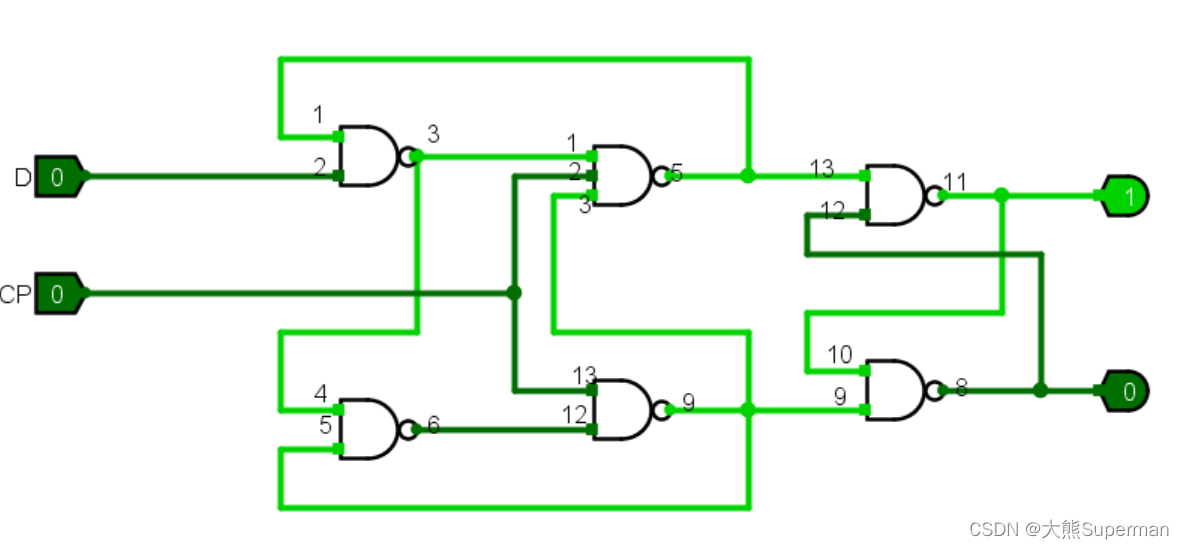

在Logisim上采用74LS00芯片实现D触发器电路,其电路如图:

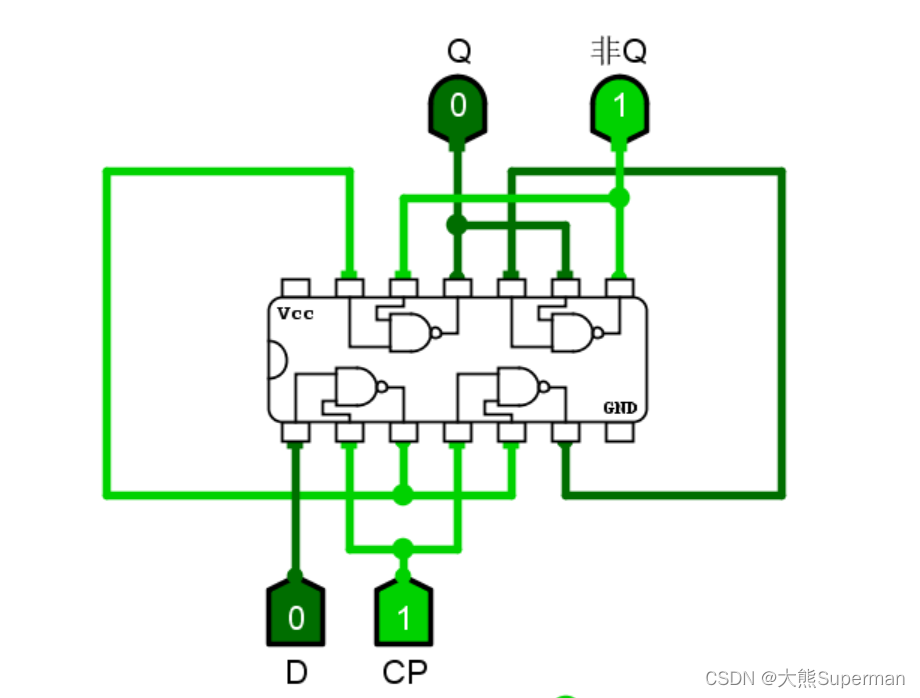

其真值表如图所示:

当CP为0时,无论D如何改变都不会影响Q的值,及Q保持上一个状态,所以会出现真直表中的四种情况;当CP为1时,Q始终与D的值相等。

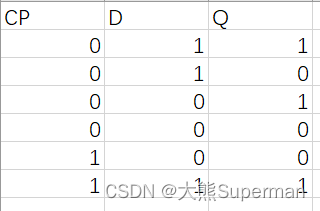

用74LS00硬件来实现D触发器,其实际电路如图:

三、在Logisim上采用74LS00芯片设计维持阻塞D触发器

维持阻塞D触发器是用来解决“空翻”问题的触发器,及仅当CP的上升沿出现的一瞬间,D端的数据才能置入触发器。

其电路如图:

在Logisim上采用门电路来实现维持阻塞D触发器电路,其电路如图:

其真值表如图:

用门电路硬件来实现维持阻塞D触发器,其实际电路如图:

3709

3709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?