应用场景:接收模块不能即时读取发送模块数据时,可能出现数据阻塞的情况

简单示例:顶层模块pipeline_top中包含三级流水线,pipeline_top存在上下游模块,且pipeline_top仅通过握手信号获知上下游数据的valid/ready情况

module pipeline_top(

input wire clk,

input wire rst,

input wire [15:0] din,

output wire [15:0] dout,

input wire i_vld, // 输入有效 - 上游模块数据有效

output wire i_rdy, // 输入就绪 - 本模块已准备好接收数据

output wire o_vld, // 输出有效 - 本模块数据有效

input wire o_rdy // 输出就绪 - 下游模块已准备好接收数据

);

// 级间握手信号

wire [15:0] data_1_2, data_2_3;

wire vld_1_2, vld_2_3;

wire rdy_2_1, rdy_3_2;

// 第一级

stage_1 stage_1_inst(

.clk (clk ),

.rst (rst ),

.din (din ),

.dout (data_1_2 ),

.previous_stage_valid (i_vld ),

.this_stage_ready (i_rdy ),

.this_stage_valid (vld_1_2 ),

.next_stage_ready (rdy_2_1 )

);

// 第二级

stage_2 stage_2_inst(

.clk (clk ),

.rst (rst ),

.din (data_1_2 ),

.dout (data_2_3 ),

.previous_stage_valid (vld_1_2 ),

.this_stage_ready (rdy_2_1 ),

.this_stage_valid (vld_2_3 ),

.next_stage_ready (rdy_3_2 )

);

// 第三级

stage_3 stage_3_inst(

.clk (clk ),

.rst (rst ),

.din (data_2_3 ),

.dout (dout ),

.previous_stage_valid (vld_2_3 ),

.this_stage_ready (rdy_3_2 ),

.this_stage_valid (o_vld ),

.next_stage_ready (o_rdy )

);

endmodule

stage_1、stage_2、stage_3分别对数据进行+1、+2、+3操作,以stage_1为例,模块实现

module stage_1(

input wire clk,

input wire rst,

input wire [15:0] din,

output reg [15:0] dout,

input wire previous_stage_valid, // 上级数据有效

output wire this_stage_ready, // 本级已就绪

output reg this_stage_valid, // 本级数据有效

input wire next_stage_ready // 下级已就绪

);

assign this_stage_ready = ~this_stage_valid || next_stage_ready; // 本级已就绪 = 本级数据为空(数据无效的情况) 或 下级已准备好接收数据(流水线顺畅运行的情况)

always_ff @(posedge clk) begin

if (rst)

dout <= 'd0;

else if (previous_stage_valid && this_stage_ready) // 如果上级数据有效 且 本级已就绪 - 则读取上级数据并完成运算

dout <= din + 'd1;

else // 否则保持输出数据不变

dout <= dout;

end

always_ff @(posedge clk) begin

if (rst)

this_stage_valid <= 'b0;

else if (this_stage_ready) // 如果本级已就绪 - 则寄存上级数据valid标志

this_stage_valid <= previous_stage_valid;

else

this_stage_valid <= this_stage_valid;

end

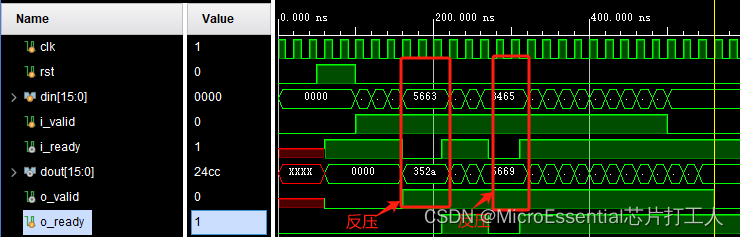

endmodule仿真波形:可以看到在o_valid为高但o_ready为低时,输出数据保持;当o_valid和o_ready同时为高时完成一次握手,数据传输

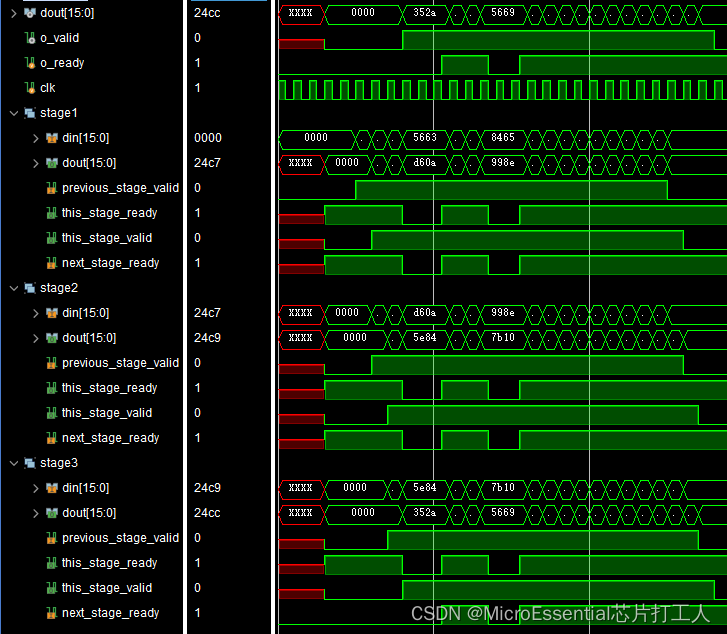

见stage_1、stage_2、stage_3模块内部波形,o_ready拉低会对内部数据流水线形成反压

1445

1445

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?