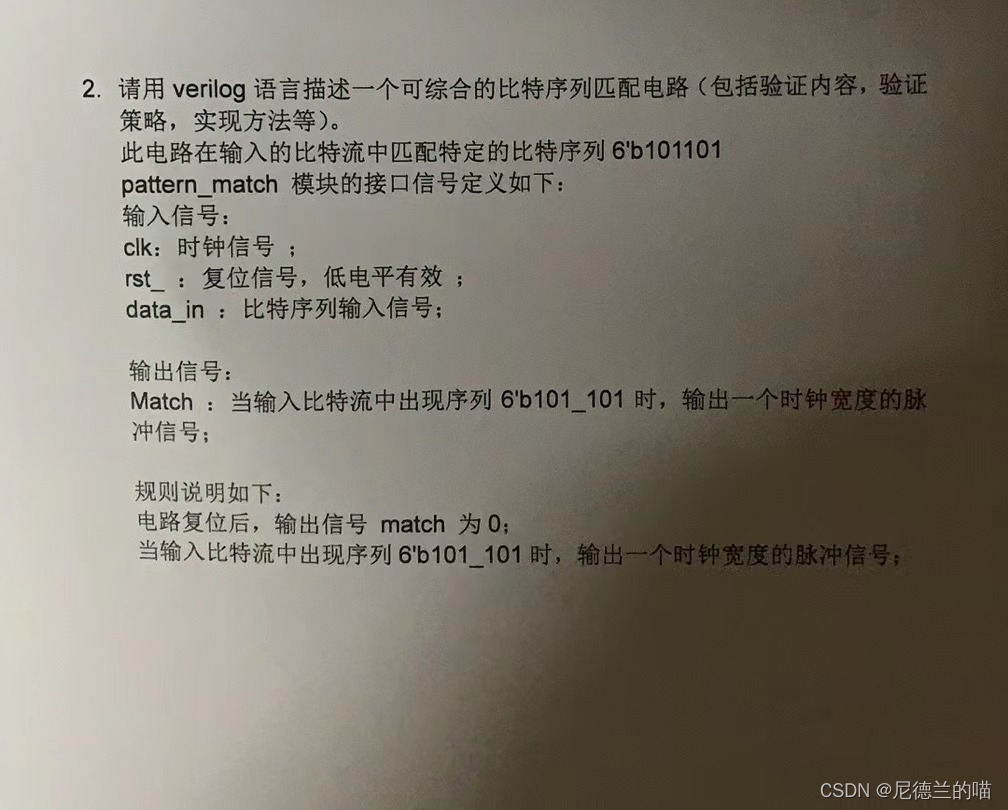

题目

几天前收到了这样一份笔试试题,希望能提供一份参考。恰好最近在家里没事做鼓捣鼓捣还看了点书,因此非常愉快的接下了这个笔试题。

RTL

这个rtl其实是比较容易实现的,单比特输入,只需要在rtl内部做移位寄存即可,当匹配上对应序列的时候即输出一个单比特脉冲的match信号。当然了,可以做一步参数化,把要匹配的序列作为parameter输入,我觉得也就差不多了吧:

module bit_match #(

parameter VALUE = 6'b101101

)(

input clk,

input rst_n,

input data_in,

output match

);

reg [6 -1:0]shift_reg;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

shift_reg <= 6'b0;

end

else begin

shift_reg <= {shift_reg[5 -1:0], data_in};

end

end

assign match = (shift_reg == VALUE);

endmoduleCTL

接下来做CTL,先观察以下这个RTL结

本文介绍了一次笔试试题,涉及比特序列匹配电路的RTL设计和CTL验证。RTL部分通过移位寄存实现,参数化匹配序列。CTL验证环境中,使用自定义interface和transaction,对输入序列进行控制和比较,确保与RTL行为一致。

本文介绍了一次笔试试题,涉及比特序列匹配电路的RTL设计和CTL验证。RTL部分通过移位寄存实现,参数化匹配序列。CTL验证环境中,使用自定义interface和transaction,对输入序列进行控制和比较,确保与RTL行为一致。

订阅专栏 解锁全文

订阅专栏 解锁全文

7448

7448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?