ICL(Instrument Connective Language):描述了测试网络的硬件结构。Instrument类似verilog的instance,只不过,ICL里面的Instrument就是tap,sib,tdr,edt等。

通过一个例子来看ICL的语法:

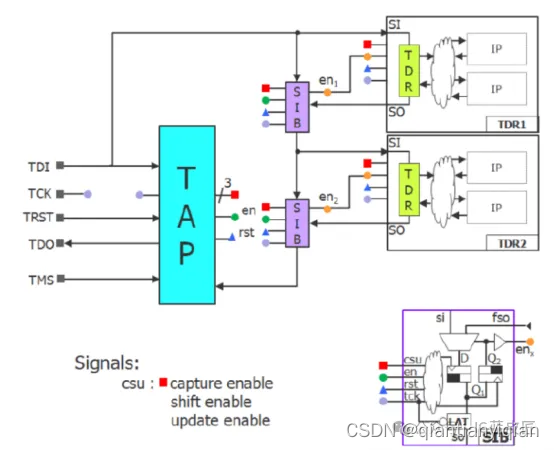

如下图结构:

首先定义SIB1的ICL

Module sib1 {

ResetPort rst { //定义reset port,以及active 极性

ActivePolarity 0;

}

SelectPort en; //定义select port

ScanInPort si; //定义 si

CaptureEnPort ce; //定义capture enable

ShiftEnPort se; //定义shift enable

UpdateEnPort ue; //定义update enable

TCKPort tck; //定义clock

ScanOutPort so { //定义scanout port,注意这个sib是下一个

Source sib; // tdr的host,要注意下源头

}

ToSelectPort en1 ;//作为host,送给tdr的select port

ScanInPort fso ; //client tdr送来的scanin

ScanInterface client { //作为tap的client

Port si;

Port so;

Port en;

}

ScanInterface host { //作为tdr的host定义

Port fso;

Port en1;

}

ScanRegister sib { //定义scan register名字以及属性

ScanInSource scan_in_mux;

ResetValue 1’b0;

}

ScanMux scan_in_mux SelectedBy sib { //定义scan mux的名字以及属性

1’b0 : si;

1’b1 : fso;

}

}

接着我们在看TDR1

Module tdr1{

ResetPort rst { //定义reset port,以及active 极性

ActivePolarity 0;

}

SelectPort en; //定义select port

ScanInPort si; //定义 si

CaptureEnPort ce; //定义capture enable

ShiftEnPort se; //定义shift enable

UpdateEnPort ue; //定义update enable

TCKPort tck; //定义clock

ScanOutPort so { //定义tdr的output

Source tdr[0];

}

DataOutPort data_out[0:0] { //定义TDR的DataOutPort属性

Source tdr[0];

}

ScanInterface client { //定义tdr作为client的属性

Port si;

Port so;

Port en1;

}

ScanRegister tdr[0:0] { //定义scan register tdr[0]

ScanInSource si;

DefaultLoadValue 1’b0;

ResetValue 1’b0;

}

}

接着看SIB2(类似SIB1)

Module sib2 {

ResetPort rst { //定义reset port,以及active 极性

ActivePolarity 0;

}

SelectPort en; //定义select port

ScanInPort si; //定义 si

CaptureEnPort ce; //定义capture enable

ShiftEnPort se; //定义shift enable

UpdateEnPort ue; //定义update enable

TCKPort tck; //定义clock

ScanOutPort so { //定义scanout port,注意这个sib是下一个

Source sib; // tdr的host,要注意下源头

}

ToSelectPort en2 ;//作为host,送给tdr2的select port

ScanInPort fso ; //client tdr送来的scanin

ScanInterface client { //作为tap的client

Port si;

Port so;

Port en;

}

ScanInterface host { //作为tdr的host定义

Port fso;

Port en2;

}

ScanRegister sib { //定义scan register名字以及属性

ScanInSource scan_in_mux;

ResetValue 1’b0;

}

ScanMux scan_in_mux SelectedBy sib { //定义scan mux的名字以及属性

1’b0 : si;

1’b1 : fso;

}

}

接着我们在看TDR2(类似TDR1)

Module tdr2{

ResetPort rst { //定义reset port,以及active 极性

ActivePolarity 0;

}

SelectPort en; //定义select port

ScanInPort si; //定义 si

CaptureEnPort ce; //定义capture enable

ShiftEnPort se; //定义shift enable

UpdateEnPort ue; //定义update enable

TCKPort tck; //定义clock

ScanOutPort so { //定义tdr的output

Source tdr[0];

}

DataOutPort data_out[0:0] { //定义TDR的DataOutPort属性

Source tdr[0];

}

ScanInterface client { //定义tdr作为client的属性

Port si;

Port so;

Port en2;

}

ScanRegister tdr[0:0] { //定义scan register tdr[0]

ScanInSource si;

DefaultLoadValue 1’b0;

ResetValue 1’b0;

}

}

最后看下TAP定义

Module tap {

TCKPort tck;//定义tap的TCK

ScanInPort tdi; //定义tap的tdi

ScanOutPort tdo ; //定义tap的tdo

TMSPort tms ;//定义tap的tms

TRSTPort trst ;//定义tap的trst

ToCaptureEnPort cn; //定义送给sib的capture enable

ToShiftEnPort shift_en; //定义送给sib的shift enable

ToUpdateEnPort update_en; //定义送给sib的update enable

ToResetPort rst;//定义送给sib的rst

ToSelectPort en ; //定义送给sib的en信号

ScanInterface tap_client { //定义tap_client的属性,声明这是个tap

Port tdi;

Port tdo;

Port tms;

}

ScanInterface host { //作为tdr的host定义

Port fso;

Port en;

}

}

下面看下顶层的连接,我们需要把TAP,SIB1,SIB2,TDR1,TDR2都在顶层声明,类似verilog的例化

Module chip {

TCKPort tck ; //定义IJTAG TCK port

ScanInport tdi ; //定义IJTAG TDI port

ScanOutPort tdo { //定义IJTAG TDO port

Source tessent_tap.tdo

};

TMSPort tms ; //定义IJTAG TMS port

TRSTPort trst ; //定义TRST port

Instance tessent_tap of tap { //例化tap

InputPort tck = tck ; //接到tck port上

InputPort tdi = tdi ; //接到tdi port上

InputPort tms = tms ; //接到tms port上

InputPort trst = trst ; //接到trst port上

InputPort fso = tessent_sib2.so ; //接到sib2的so

}

Instance tessent_sib1 of sib1 { //例化sib1

InputPort rst = tessent_tap.rst ; //接到tap的rst

InputPort si = tdi ; //接到tdi

InputPort en = tessent_tap.en ; //接到tap的en

InputPort ce = tessent_tap.ce ; //接到tap的ce

InputPort ue = tessent_tap.us ; //接到tap的ue

InputPort se = tessent_tap.se ; //接到tap的se

InputPort fso = tessent_tdr1.so //接到tdr的so

}

Instance tessent_sib2 of sib2 { //例化sib2

InputPort rst = tessent_tap.rst ;

InputPort si = tessent_sib1.so ; //接到sib1的so

InputPort en = tessent_tap.en ;

InputPort ce = tessent_tap.ce ;

InputPort ue = tessent_tap.us ;

InputPort se = tessent_tap.se ;

InputPort fso = tessent_tdr2.so //接到tdr2的so

}

Instance tessent_tdr1 of tdr1 { //例化tdr1

InputPort rst = tessent_tap.rst ;

InputPort si = tdi ; //接到tdi

InputPort en = tessent_tap.en ;

InputPort ce = tessent_tap.ce ;

InputPort ue = tessent_tap.us ;

InputPort se = tessent_tap.se ;

}

Instance tessent_tdr2 of tdr2 { //例化tdr1

InputPort rst = tessent_tap.rst ;

InputPort si = tessent_sib1.so ; //接到sib1的so

InputPort en = tessent_tap.en ;

InputPort ce = tessent_tap.ce ;

InputPort ue = tessent_tap.us ;

InputPort se = tessent_tap.se ;

}

}

分享更多内容关注WX:IC蓝皮匠

原创链接:https://mp.weixin.qq.com/s/6HrmEt2X45VEcHCmwYJxVA

6656

6656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?