1. 编译vivado ip仿真库

注意:modelsim10.5不支持仿真vivado2019.2版本的库,需要modelsim2019版本才可以。

预计编译需要30min,耐心等待。

2.库路径添加至modelsim

首先,找到vivado ip库路径在:刚才编译ip库的文件夹,目录下会有一个modelsim.ini文件,包含所有vivado ip仿真文件路径。打开文件并找到“;mvc_lib = $MODEL_TECH/../mvc_lib”,将下面包含的路径连续的行复制。

然后,在modelsim安装路径下找到modelsim.ini文件,取消其只读属性,然后打开,

找到“modelsim_lib = $MODEL_TECH/../modelsim_lib”处

准备粘贴,刚刚复制的vivado ip库路径。

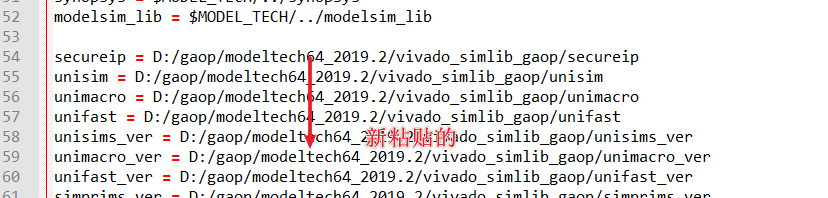

粘贴之后是这样的:

保存,打开modelsim,看到了我们新增的库,就是添加ok啦

end

5131

5131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?