CREE第二代SiC MOSFET驱动电路原理图及PCB板设计

MOSFET驱动电路原理图及PCB板设计)

电路原理图

整个驱动电路分为三个部分。

一个是光耦隔离电路,负责把功率侧和逻辑侧隔离开来,防止强电侧电路干扰弱点侧电路。与传统的隔离措施相比,光耦隔离具有体积小、成本低、电磁兼容强的特点。这里选择的光耦隔离芯片是ACPL-4800,隔离电压高达3.75kVRMS。

一个是功率放大电路,负责给SIC开关管的开通与关断提供驱动电流。这里选择的芯片是IXDN-609,输出峰值电流为9A。

最后一个是隔离电源,负责给光耦隔离电路和功率放大电路提供驱动电压,也负责提供SIC的开通关断电压的参考值。这里采用的隔离电源芯片是QA01C,输入为+15V,输出为+20V,0V,-4V

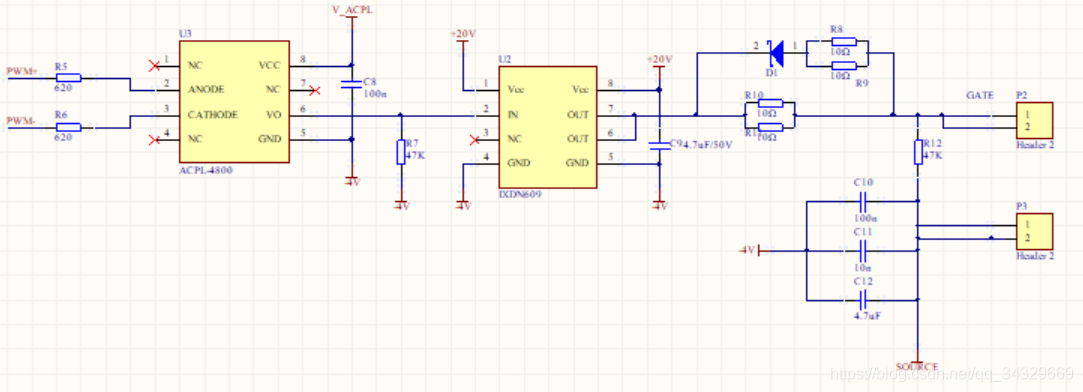

光耦隔离电路和功率放大电路原理图

电路的优点:

电路的优点:

1、用二级管将栅极开通关断电阻分开,能够通过实验分别调整开通关断电阻的阻值,获得更好的开通关断波形。

2、R12可以在开关管关断后给栅源电容放电,防止管子击穿。

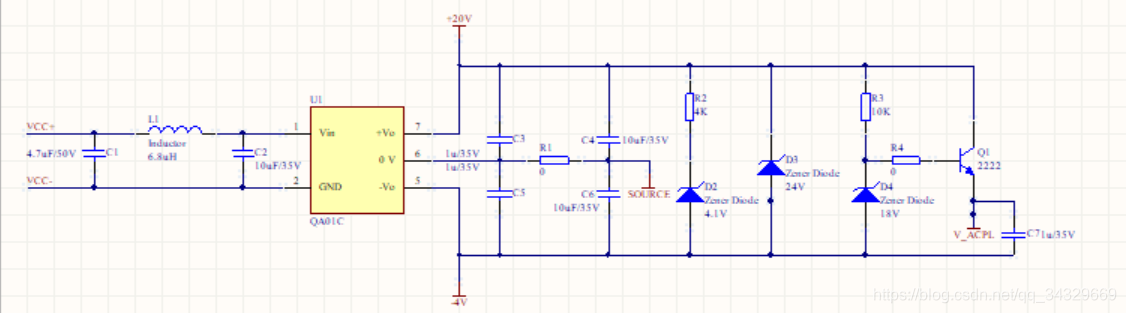

隔离电源电路原理图

电路的优点:

1、设计QA01C输入滤波电路,增加抗EMI干扰的能力。

2、由于ACPL-4800的供电电压幅值为4.5V-20V&

本文详细介绍了CREE第二代SiC MOSFET驱动电路的设计,包括光耦隔离、功率放大和隔离电源的电路原理图。电路采用ACPL-4800光耦隔离芯片,IXDN-609功率放大器和QA01C隔离电源芯片。PCB布局上,通过四层板设计优化了隔离性能和栅极-源极之间的杂散电感,确保良好的电磁兼容性和可靠性。此外,分享了电路设计中的一些实用技巧,如过孔连接规则的设定。

本文详细介绍了CREE第二代SiC MOSFET驱动电路的设计,包括光耦隔离、功率放大和隔离电源的电路原理图。电路采用ACPL-4800光耦隔离芯片,IXDN-609功率放大器和QA01C隔离电源芯片。PCB布局上,通过四层板设计优化了隔离性能和栅极-源极之间的杂散电感,确保良好的电磁兼容性和可靠性。此外,分享了电路设计中的一些实用技巧,如过孔连接规则的设定。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5268

5268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?