1.查找表(LUT)原理与结构

①查找表简称LUT,本质上就是一个RAM。目前FPGA中多数使用的是4输入的LUT,所以可以看成一个有4位地址线的RAM。

②当描述了一个逻辑电路以后,FPGA 开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

2.FPGA基本结构

目前主流 FPGA 都采用了基于 SRAM 工艺的查找表结构,其组成部分主要有:

①可编程输入/输出单元(IOB)

简称 I/O 单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA 内的 I/O 按组分类(即每个bank),每组都能够独立 地支持不同的I/O 标准。通过软件的灵活配置,可适配不同的电气标准与 I/O 物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

②基本可编程逻辑单元(CLB)

FPGA 的基本可编程逻辑单元是由查找表和寄存器组成的,查找表完成纯组合逻辑功能。FPGA 内部寄存器可配置成触发器或锁存器。Altera 基本可编程单元 LE 配置为 1 寄存器加一个查找表。

③嵌入式块 RAM

目前大多数FPGA都有内嵌的块RAM。嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构。

④丰富的布线资源

布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。由于在设计过程中,往往由布局布线器自动根据输入的逻辑网表的拓扑结构和约束条件选择可用的布线资源连通所用的底层单元模块,所以常常忽略布线资源。

⑤底层嵌入功能单元

底层嵌入功能单元是指通用程度较高的嵌入式功能模块。如锁相环(Phase Locked Loop,PLL)、DLL(Delay Locked Loop)、DSP(Digital Signal Processing)和CPU等。

⑥内嵌专用硬核

与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱的功能模块,不是所有FPGA器件都包含硬核。

补充:

IP软核通常是经过RTL级设计优化和功能验证的硬件语言代码,但其中不含有任何具体的物理信息。可以综合出正确的门电路级设计网表,并可以进行后续的结构设计,具有很大的灵活性,软IP内核也称为虚拟组件。

IP固核的设计程度则是介于软核和硬核之间,除了完成软核所有的设计外,还完成了门级电路综合和时序仿真等设计环节。

IP硬核是基于半导体工艺的物理设计,已有固定的拓扑布局和具体工艺,并已经过工艺验证,具有可保证的性能。其提供的是电路物理结构掩模版图和全套工艺文件,是可以拿来直接用的全套技术。

3.FPGA的RAM、ROM、CAM

①RAM:分为SRAM和DRAM,具体看存储器的6.2小节

②ROM:只读存储器,具体看存储器的6.3小节

③CAM:内容地址存储器;CAM在其内部的每个存储单元中都有一个比较逻辑,写入CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。

FPGA 中可以综合实现为 RAM、ROM、CAM 的三种资源分别是块RAM(Block RAM)、触发器(FF)、查找表(LUT),当然值得注意的是,在生成 RAM 等存储单元时,应该首选 block ram 资源;第一,使用 Block RAM 等资源可以节约更多的 FF 和 LUT 等底层可编程单元,是最大程度发挥器件效能,节约成本的一种体现;第二,Block RAM 是一种可以配置的硬件结构,其可靠性和速度与用 LUT 和 寄存器构建的存储器更有优势。

4.硬件语言的层次

系统级

算法级

行为级(RTL)

门级

开关级

5.寄生效应

寄生效应就是在PCB电路中大肆破坏、原因不明的小故障——渗入高速电路中的寄生电容和寄生电感。在直流或者低频的情况下,寄生效应是不怎么体现的。在交流或者高频条件下,这种寄生效应也是很难克服的,只能通过优化线路,尽量使用管脚较短的贴片原器件来减少影响,做不到完全消除。

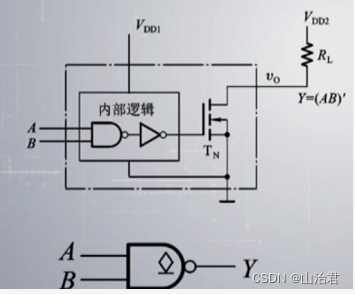

6.线与逻辑

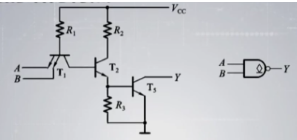

线与逻辑:两个信号相与。线与要用到OC门或者OD门来实现。想不到这么简单的逻辑需要复杂的门电路吧!

①在CMOS门电路中,实现线与功能的是漏极开路输出门电路,也就是OD门。OD门在使用时,必须将输出经上拉电阻到电源,不能独立存在,只是用来改善电路的。

②在TTL门电路中,实现线与功能的是集电极开路输出门电路,也就是OC门。工作时同样要外接上拉电阻。

具体可以看此链接的第8小节

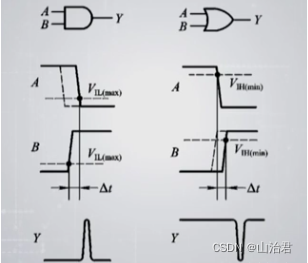

7.竞争冒险

竞争: 两个输入信号同时向相反逻辑电平跳变。通俗的说,就是两个输入,一个从1变0,同时另一个从0变1。

竞争-冒险:由于竞争在电路输出端可能产生尖峰脉冲的现象。

注意:有竞争不一定产生尖峰脉冲,只有在存在不同步的跳变时,某输入先跳变而另一输入还未跳变时产生尖峰脉冲。(输入信号进入电路时有先后,不同步)

判断准则:只要输出端的逻辑函数在一定条件下能简化成Y=A+A’或Y=A·A’则可判定存在竞争-冒险现象。

8.消除竞争冒险的方法

①滤波电容:因为尖峰脉冲很窄,用很小的电容就能削弱尖峰到Vth一下,但由于电容会增加电压波形的上升时间和下降时间,会破坏原有波形。

②引入选通脉冲:利用选通脉冲,在电路达到稳定后,P的高电平期间的输出信号不会出现尖峰。(就是再加一个区别信号来防止尖峰出现)

③修改逻辑设计:防止Y=A+A’或Y=A·A’的出现(并不是万能的,办法有限,但效果很好)

参考:

【1】 FPGA笔试面试(五)

【2】https://www.cnblogs.com/lifan3a/articles/4229952.html

1263

1263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?