这是数电实验的部分内容, 实验采用的开发板芯片是 Cylone II EP2C8Q208C8, 时钟主频50MHz, 生成400Hz的频率主要用于数码管显示。

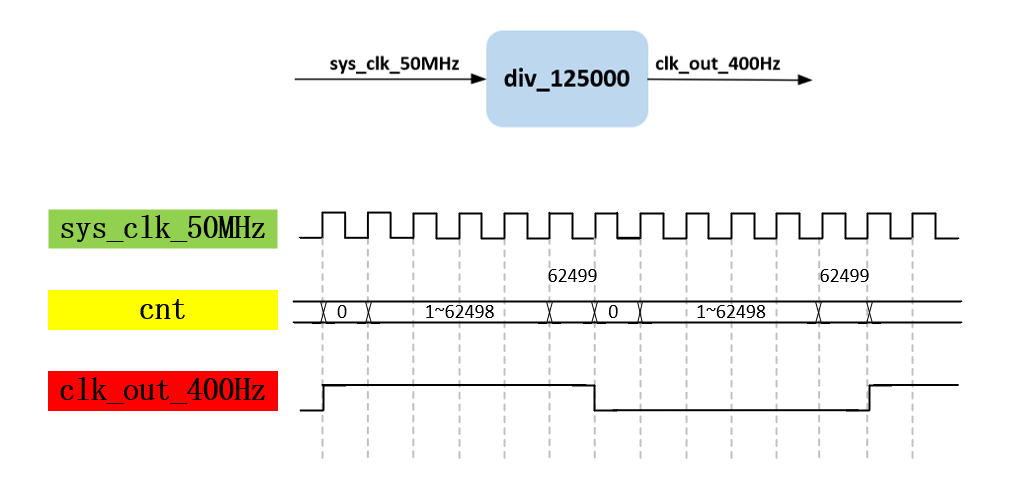

要将50MHz转换成400Hz, 则需要125000分频, 是偶分频。即信号sys_clk_50MHz的125000个周期相当于信号clk_out_400Hz的一个周期。当计数器从0计数到62499时, 将输出信号反转一次, 从而形成周期为输入信号125000个脉冲的输出信号。

时序原理图如下:

Verilog代码如下:

module f_400Hz

(

input sys_clk, //50M输入

output reg clk_400 //输出400

)

reg [19:0] cnt;

always@(posedge sys_clk)

if(cnt == 20'd62499)

cnt <= 20'd0;

else

cnt <= cnt + 20'd1;

always@(posedge sys_clk)

if(cnt == 20'd62499)

clk_400 <= ~clk_400;

else

clk_400 <= clk_400;

endmodule

1170

1170

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?