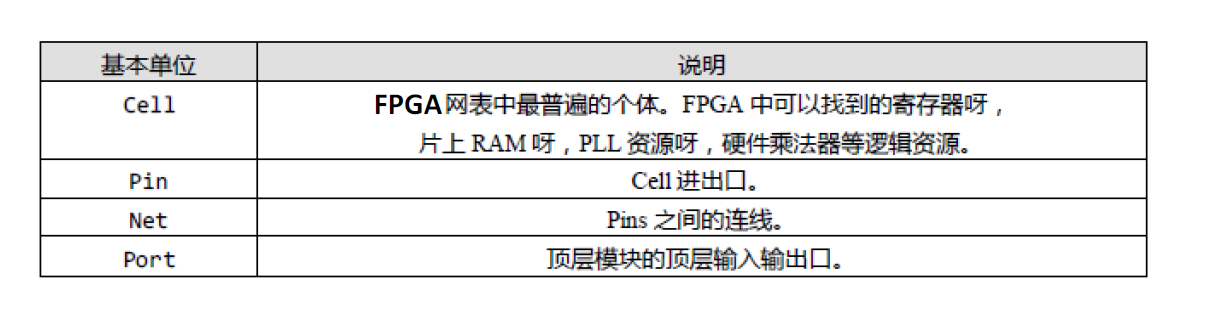

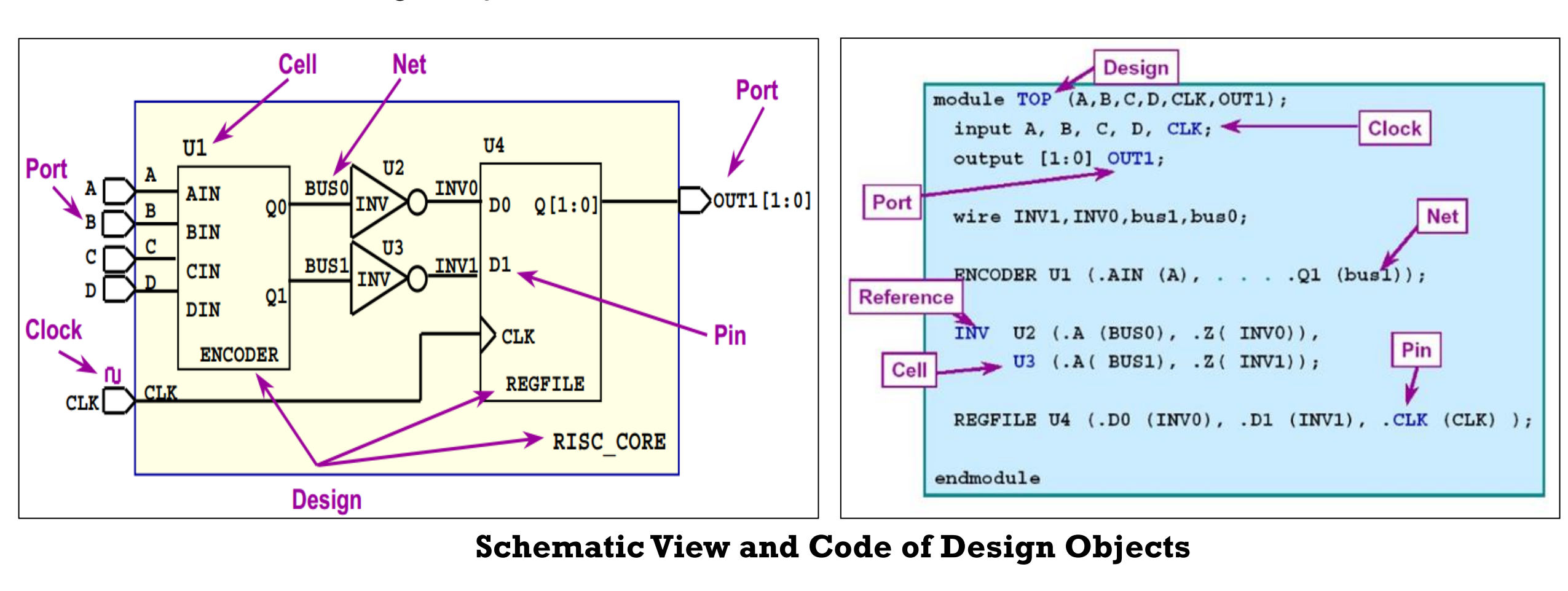

(1) Cells :器件中的基本结构单元( 例如,查找表、寄存器、IO 单元、PLL 、存储器块等) 。

(2) Pins:Cell 的输入输出端口。注意:这里的Pins 不包括器件的输入输出引脚。

(3) Nets:同一个Cell 中,从输入pin 到输出pin 经过的逻辑。注意,网表中连接两个相邻Cell 的连线不被看作Net,而被看作同一个点,等价于Cell 的pin 。虽然连接两个相邻Cell 的连线不被看作Net,但这个连线还是有其物理意义的,即等价于FPGA 器件中的一段布线逻辑,会引入一定的延迟。

(4) Ports :顶层逻辑的输入输出端口。对应已经分配的器件引脚。

数字设计中的port,cell,pin,design

于 2023-09-20 15:08:27 首次发布

本文详细解析了FPGA设计中的关键概念,包括基本结构单元如查找表和寄存器,以及Pins、Nets和Ports的作用。特别强调了Net在逻辑连接中的角色,以及顶层逻辑的输入输出端口与物理FPGA布线的关系和延迟影响。

本文详细解析了FPGA设计中的关键概念,包括基本结构单元如查找表和寄存器,以及Pins、Nets和Ports的作用。特别强调了Net在逻辑连接中的角色,以及顶层逻辑的输入输出端口与物理FPGA布线的关系和延迟影响。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?