时序违例可以分为两种情况,分别为建立时间违例和保持时间违例

建立时间违例

降低频率

时钟频率定的太高,导致Tcycle太小,使得不满足建立时间要求。当然最简单的就是降低时钟频率,但是一般一个电路架构定下来的时候为了满足速度与吞吐率的要求,频率一般不允许有太大的改动。

提升工艺

那就是工艺定的实在不合适,基本cell延时很大,可以换更先进的工艺。

上面两种可能性在实际真正的项目里面发生的可能不大,因为一般项目实际编码之前,架构师对工艺与频率都是评估过的。

实际让我们工程师去解决的问题就是由于两级寄存器之间的组合逻辑延时太大造成的问题。我们可以从前端和后端两个角度来进行考虑:

前端设计

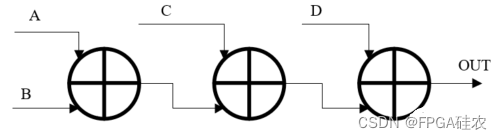

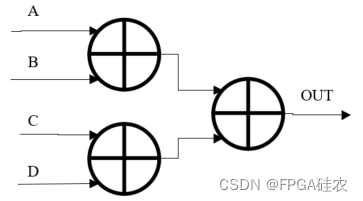

1.可以考虑关键路径上的逻辑并行化(重排),减少链路延时。举个简单的例子,比如out = a+b+c+d。

未优化前

优化后(采用树结构)

2.可以考虑有些功能电路的更优设计以降低延时,比如,超前进位加法器比行波逐位进位链加法器的延时更短。

3. 再就是卡诺图化简,较少门级资源同时也会对速度有所优化,但是一般综合工具可以做到。

4. 如果上述都解决不了,建立时间违例比较严重,就需要考虑插入寄存器,形成流水线(pipline)。

后端设计

- 后端设计可以通过调整关键路径的时钟SKEW来解决,但是一般只是针对小范围的违例(对于建立时间来说,skew越大越好)。

- 可以采用多阈值单元,从半导体器件原理大家都知道,mos管阈值越小,其延时越小,因此可以在关键路径采用阈值小的单元。

- 可以采用面积更小的门级单元,面积大容载大,自然延时大(当然面积大的单元其驱动能力强)。(可参考电容的时间常数t=RC)

其他

- 可以通过适当提高工作电压来解决,电路的延时本质就是充放电的延时,如果电压越高,充放电时间就会越快,延时越小。因此也可以通过提高关键模块的工作电压,划分不同的工作电压域。

- 寄存器平衡 (Register Balancing)。

寄存器平衡就是在你的关键路径中移动你的寄存器。第一就是你手动移动 —— 改代码。第二就是设定综合器让它自己移动 —— 不到万不得已不这么干,因为这么做容易导致代码移植性变差。整体设计策略:移动寄存器位置,平衡各组合逻辑路径的门延时。 - 逻辑展开(Flatten Logic Structures)

逻辑复制是一种通过增加面积来改善时序条件的优化手段,最常使用的场合是调整信号的扇出。如果某个信号需要驱动后级很多单元,此时该信号的扇出非常大,那么为了增加这个信号的驱动能力,一种办法就是插入多级Buffer,虽然这样能增加驱动能力,但是也增加了这个信号的路径延时。为了避免这种情况,此时可以复制生成这个信号的逻辑,用多路同频同相的信号驱动后续电路,使平均到每路的扇出变低,这样不需要插入Buffer就能满足驱动能力增加的要求,从而节约该信号的路径延时。

在大部分逻辑设计中,高扇出信号多为同步信号,即寄存器信号,所以进行逻辑复制时是对寄存器进行复制。由于高扇出信号会增加布局布线的难度,减缓布线速度,因此可以通过寄存器复制解决两个问题:减少扇出,缩短布线延时; 复制后每个寄存器可以驱动芯片的不同区域,有利于布局布线。 - 消除代码中的优先级。这里需要多说一句:现在的工具很智能,就算你写成if-else 有优先级的结构,有时候也能综合出并行结构。如果并行也符合你的设计要求,为了安全起见,最好还是写成case这种并行结构比较好。

保持时间违例

保持时间裕量与建立时间裕量是一对互斥的关系,上述可以用于优化建立时间裕量的方法,都不能用于优化保持时间裕量。

保持时间违例可以通过如下方式解决

- 在组合逻辑中插入延时buffer,或者链路拉长,使得 T l o g i c T_{logic} Tlogic变大

- 可以在后端调整时钟SKEW,使得违例寄存器的时钟SKEW变得更小(相对于正SKEW)

3647

3647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?