RDC问题定义

在芯片设计中,RDC是reset domain crossing 的缩写,类似于CDC(clock domain crossing),由于现在SOC芯片是有很多ECUs组成,为了使整个系统能够快速从复位中恢复, 用户希望SOC里面每个ECU模块都可以有自己独立的异步复位信号,这样可以在出问题的时候只复位有错误逻辑的模块,而使其它模块保持正常工作。

RDC问题描述

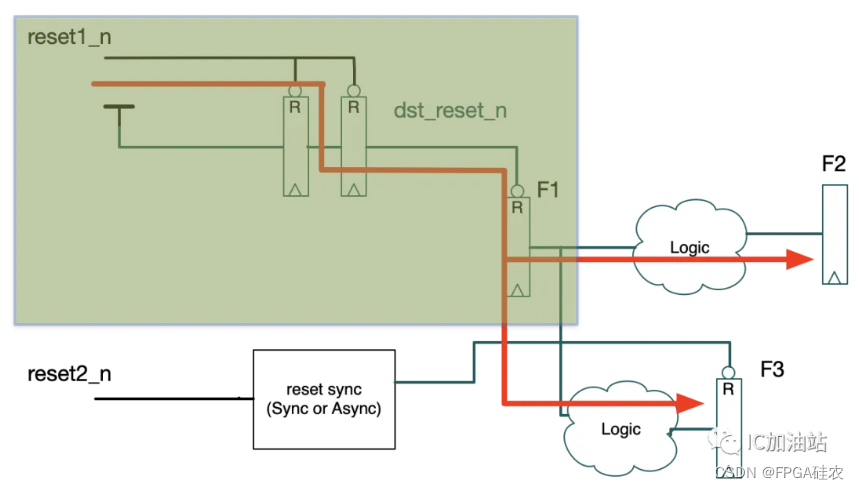

RDC的一个例子如下:

在上图中,有2个reset信号,分别是reset1_n和reset2_n。其中flop F1是被reset1_n给异步reset的。而F3是被reset2_n给异步reset的。F2可能是被同步reset给复位,也可能没有reset。而这其中,F1的输出Q是F2和F3输入D的fan-in,也就是说F1的变化会影响到F2和F3的值。

考虑这种情况:

reset1_n assert了,但是reset2_n并未assert,即F3和F2仍然工作在正常模式,并没有被复位,那么F2和F3可能会产生meta

本文详细介绍了数字IC设计中RDC(Reset Domain Crossing)问题的定义、原因及其对芯片逻辑错误的影响。通过具体示例阐述了RDC可能导致的亚稳态问题,并提出了三种解决方法:使用clamp细胞、停止相关时钟以及同步器的添加。随着SoC复杂性的增加,理解和解决RDC问题对于保证芯片设计的正确性和可靠性至关重要。

本文详细介绍了数字IC设计中RDC(Reset Domain Crossing)问题的定义、原因及其对芯片逻辑错误的影响。通过具体示例阐述了RDC可能导致的亚稳态问题,并提出了三种解决方法:使用clamp细胞、停止相关时钟以及同步器的添加。随着SoC复杂性的增加,理解和解决RDC问题对于保证芯片设计的正确性和可靠性至关重要。

订阅专栏 解锁全文

订阅专栏 解锁全文

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?