前言

2023.4.7

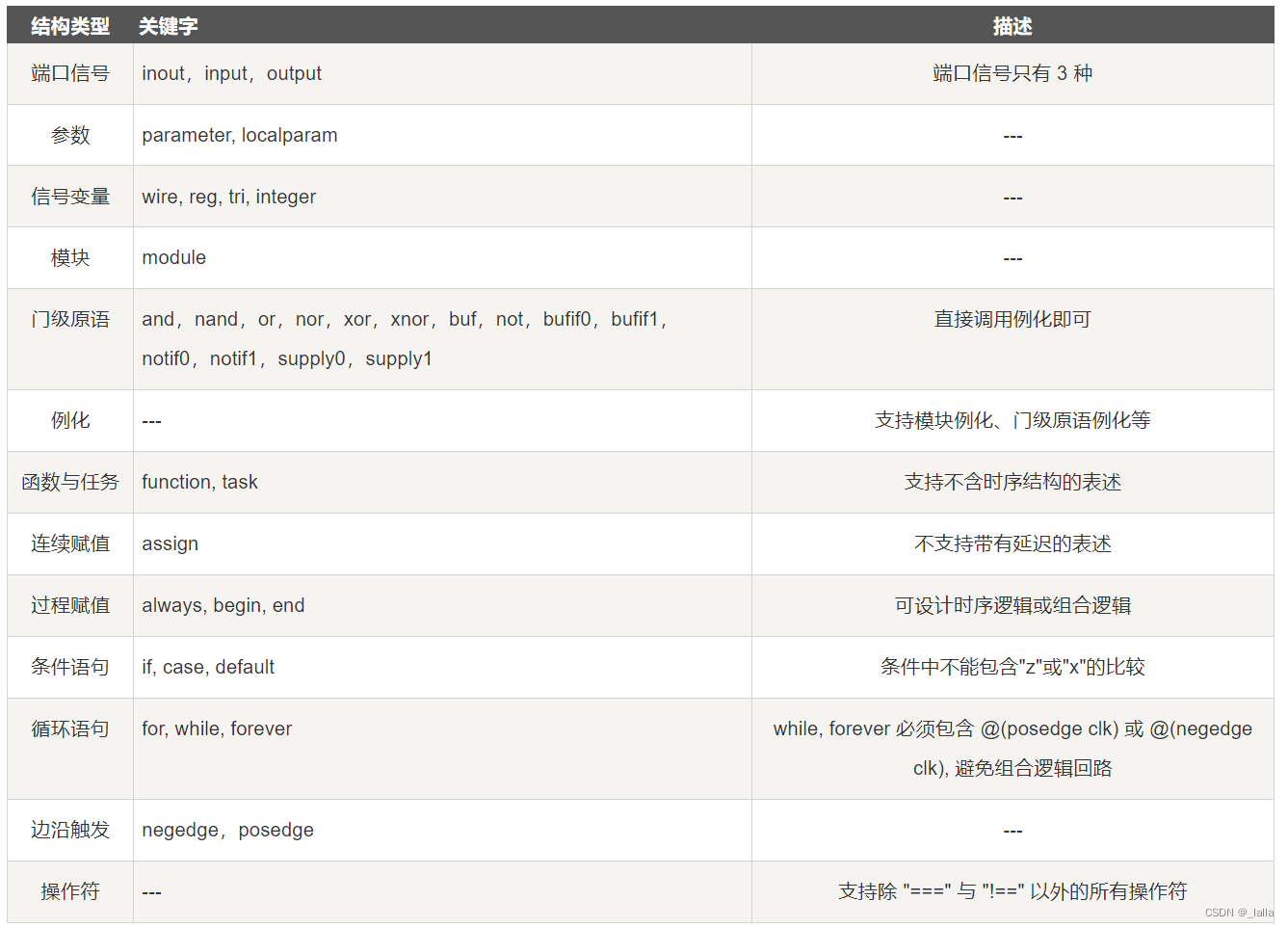

一、verilog可综合设计

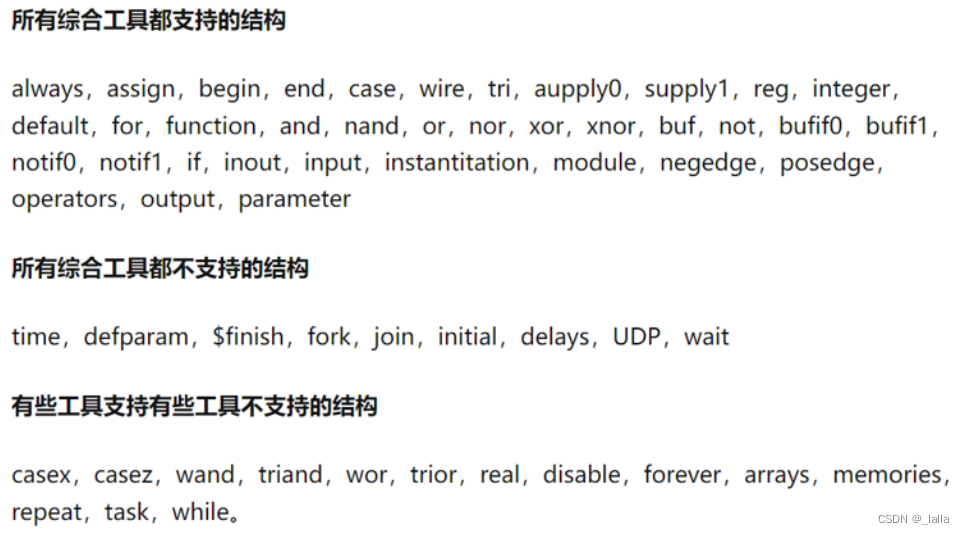

1、所有综合工具都支持

- task、assign里面不包含时序或延迟

- always、assign、begin/end、generate、module、

posedge、negedge - 函数:function、

for、if、case/default - 变量:reg、wire、tri、integer、parameter

- 输入输出:inout、input、output

- 逻辑门:and、nand、or、xor、nor、xnor、not

2、所有综合工具都不支持

- 变量

time(64位) - 大多数系统任务,

$finish,$fopen,$display initial:用于变量初始化和在仿真平台产生激励信号fork-join:仿真的适合用来描述并行结构- 延时语句

# - 电平触发敏感:

wait,多用于仿真信号的检测启动 - 强制赋值和释放:

force和release - 操作符

===和!== defparam:当一个模块引用另外一个模块时,高层模块可以改变低层模块用parameter定义的参数值,defparam adder.LENGTH = 5- cmos、nmos、pmos

3、可能支持

- 变量

real,常用于仿真时的精确计算 casex和casezdisable,终止过程块的执行,大部分综合工具都不支持UDP,用户自定义原语,大多数都支持,古老的不支持repeat,while,forever,循环次数为常量时可能综合- wand,triand,wor,trior,当信号有多个驱动源时使用,现在不怎么用了

- 除法/和取余%也不一定,一般不行

4、建立可综合模型的原则

- 不使用initial。

- 不使用#10。

- 不使用循环次数不确定的循环语句,如forever、while等。

- 不使用用户自定义原语(UDP)。

- 尽量使用同步方式设计电路。

- 除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

- 用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。

- 所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

- 对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。

- 不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。

- 如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。

- 避免混合使用上升沿和下降沿触发的触发器。

always@(posedge clk or negedge clk)是不可综合的 - 同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。

- 避免在case语句的分支项中使用x值或z值。

609

609

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?