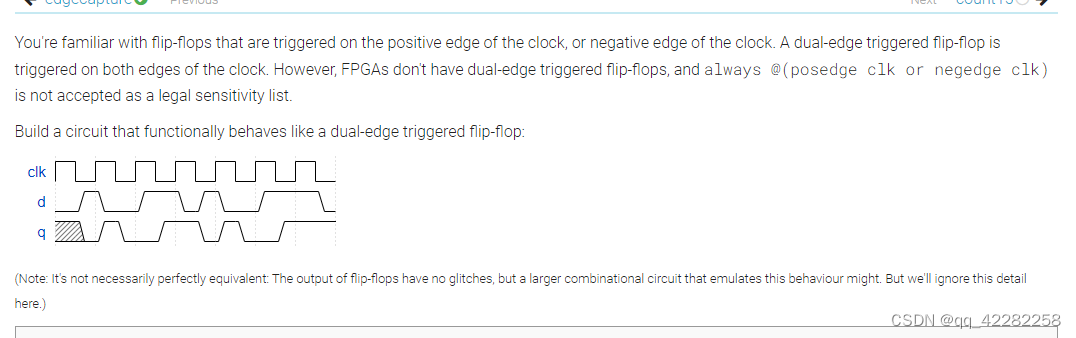

1.原题复现

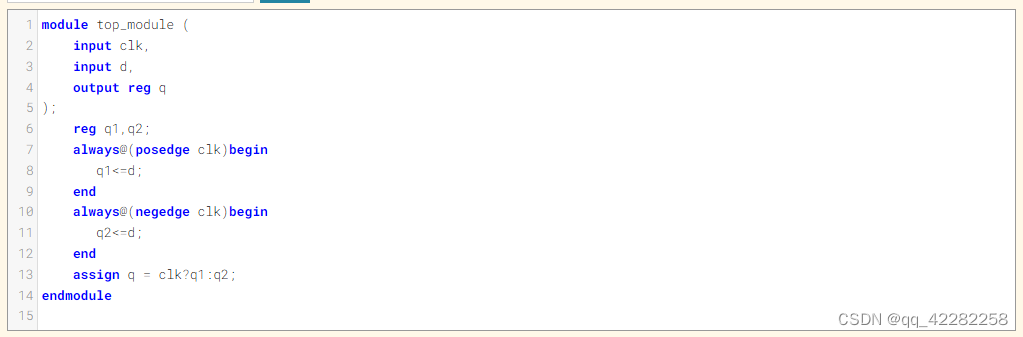

2.代码

首先要知道是的:verilog不能够支持同时触发上边沿和下边沿,FPGA中只有单边沿触发器,没有双边沿触发器这种器件。(唯一的例外是DDR,但是DDR也是通过实例化来实现的)可以参考:【 Verilog 】always@()的敏感源中为什么不能双边沿触发?为什么不能双时钟触发?

自己的做法:

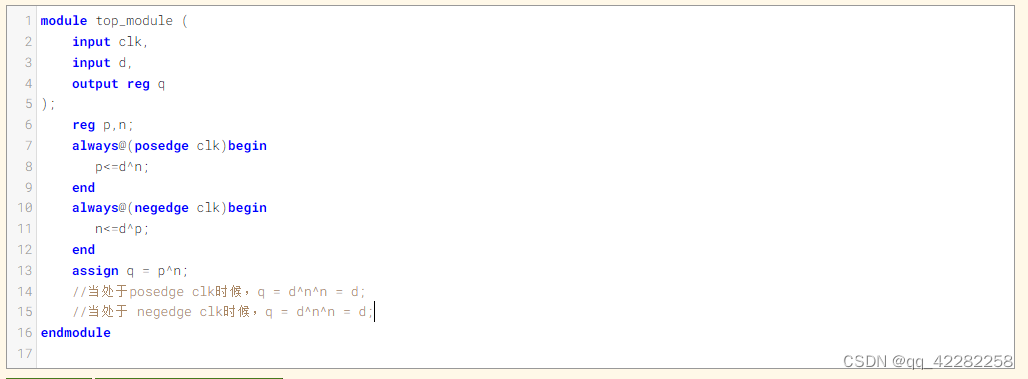

但经过查询对比其他的代码之后,发现这样做会有一个毛刺(gitch)的问题存在,至于为什么会出现毛刺:可以参考该篇博客FPGA中如何实现双边沿采样? 因此,给出了第二种代码做法:

补充一下异或的用法:

1.两个相同的数字异或结果为0

2.如果其中一个数为0,那么结果将会是另外一个数。

相关的参考博客为:

verilog实现双边沿触发器Dual-edge triggered flip-flop

1039

1039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?