Structural Sequential Loops and Handling

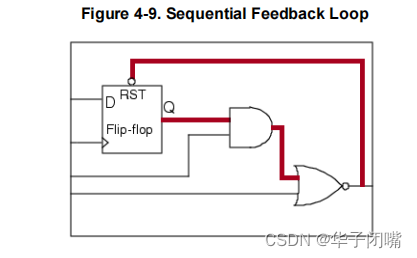

当锁存器或触发器的输出直接或通过其他逻辑反馈给其中一个输入时,就会出现顺序反馈回路。

处理方式 如下:虽然ATPG工具可能会因顺序循环而损失一些测试覆盖率,但这些循环不会像组合循环那样给工具带来广泛的问题。就其本质而言,ATPG tool使用“非扫描单元的ATPG处理”中描述的模拟基元,对设计中的非扫描顺序元素重新建模。插入这些基元后,以某种方式自动打断循环。(改变就会自动的打断)

Redundant Logic

在大多数情况下,应避免使用冗余逻辑,因为具有冗余逻辑的电路会导致可测试性问题。首先,对冗余故障进行分类需要大量的分析工作。

此外,冗余故障本质上是不可测试的,因此会降低故障覆盖率。

某些电路需要冗余逻辑;例如,消除竞争条件的电路或在设计中建立高可靠性的电路。在这些情况下,应该添加测试点以在测试过程中消除冗余。

Asynchronous Sets and Resets

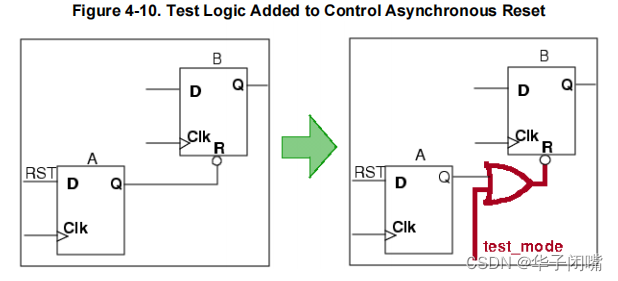

可扫描性检查将不可控集合和重置行驱动的序列元素视为不可扫描。可以通过以下两种方法之一来纠正这种情况:1.可以添加测试逻辑以使信号可控 2.在测试期间使用初始化模式来控制这些内部生成的信号。

在本例中,Tessent Scan添加了一个OR门,它使用test_mode(而不是Scan_enable)信号在测试过程中保持触发器B的复位处于非活动状态。然后将test_mode信号限制为1,这样触发器B在测试期间就永远不会复位。要插入这种类型的测试逻辑,可以使用Tessent Scan命令set_test_logic 。

Gated Clocks

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3653

3653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?