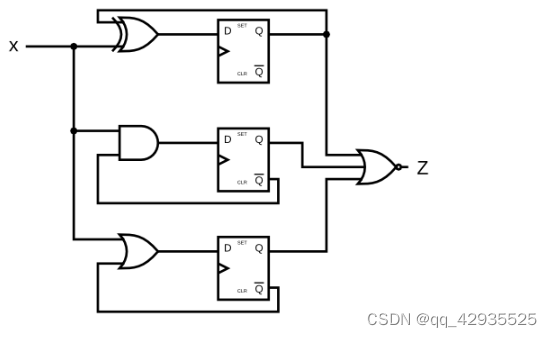

Given the finite state machine circuit as shown, assume that the D flip-flops are initially reset to zero before the machine begins.

Build this circuit.)

HDLbits上的一道题,用实例化做的:

module top_module (

input clk,

input x,

output z

);

wire d1,d2,d3,d4,d5,d6;

wire q2,q3;

assign d1 = d4 ^ x ;

assign d2 = ~d5 & x ;

assign d3 = ~d6 | x ;

D_D DD1(.d(d1), .q(d4), .clk(clk) );

D_D DD2(.d(d2), .q(d5), .clk(clk) );

D_D DD3(.d(d3), .q(d6), .clk(clk) );

assign z = ~( d4 | d5 | d6 );

endmodule

module D_D(

input d,

input clk,

output q

);

always@(posedge clk)begin

q <= d;

end

endmodule

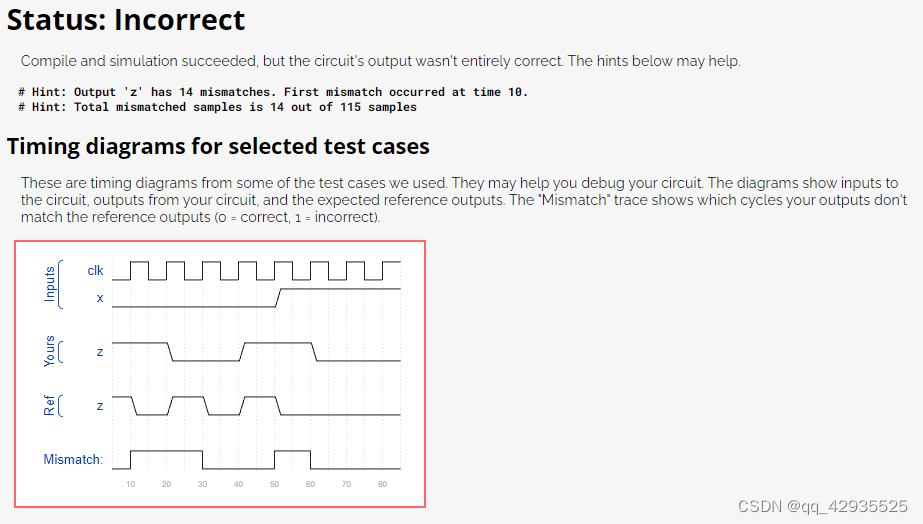

编译通过了,这里我最开始把D触发器的~q端也定义为一个output,后来编译不通过,如下:

module D_D(

input d,

input clk,

output q,

output q1

);

always@(posedge clk)begin

q <= d;

q1 <= ~ q;

end

endmodule

省略这个输出端口反而对了,以后的D触发器对于反向端是不必要定义的啊,记录一下。

983

983

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?