3.1.1 基于Block RAM的IP核简介

Xilinx FPGA内部的Block RAM硬核可用于数据内容的长时间或临时存储。Block RAM在Xilinx Spartan-2系列中首次启用。随着器件工艺水平和用户需求的不断增加,FPGA内部的Block RAM容量从最初的16Kb提高到了5000Kb以上。从Virtex-5系列开始,单个RAM硬核的存储规模已经18Kb增加到36Kb,即由两个18kb存储器构成。在简单双口模式中的数据宽度从36位增加到72位,单口RAM的带宽提高了一倍。Virtex-6系列FPGA中嵌入Block RAM硬核可以配置成独立的36Kb Block

RAM使用,或配置成两个独立的18Kb RAM分开使用。

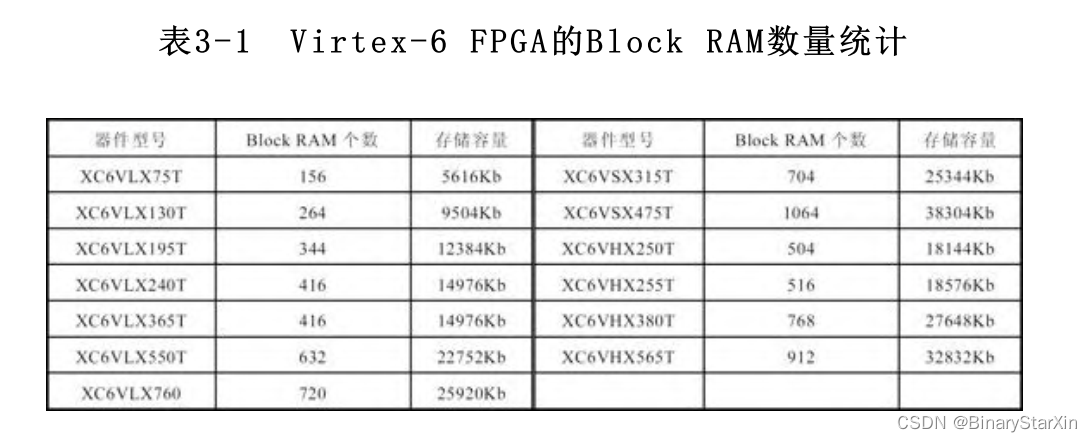

Virtex-6系列各FPGA型号所含有的Block RAM个数各不相同,具体参数如表3-1所示。

以Block RAM硬核作为基础缓存资源,根据用户需求在XilinxCORE Generator工具下例化生成单端口ROM、双端口ROM、单端口RAM、双端口RAM、内容可寻址存储器(CAM)、FIFO存储器,其中FIFO包括同步FIFO、异步FIFO和数据宽度转换FIFO等。

1.单端口和双端口ROM功能简述

ROM(Read Only Memory,只读存储器)IP核是只有数据读取接口,没有数据写入功能的存储器。通过对ROM导入初始配置文件,可以给ROM内部的各个地址赋初值,用户再通过地址接口读取ROM对应地址存储的数据。在RO

订阅专栏 解锁全文

订阅专栏 解锁全文

293

293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?