4.5.3 环路为什么不能锁定

行为仿真用于检查程序的语法功能,时序仿真可真实地反映程序运行情况,两种仿真过程中的使用及操作方法本身没有区别,下面以行为仿真为例讲解仿真过程及 ModelSim 的使用方法。

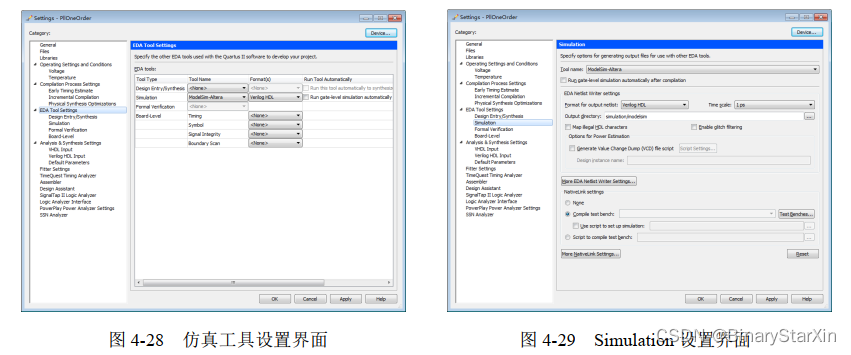

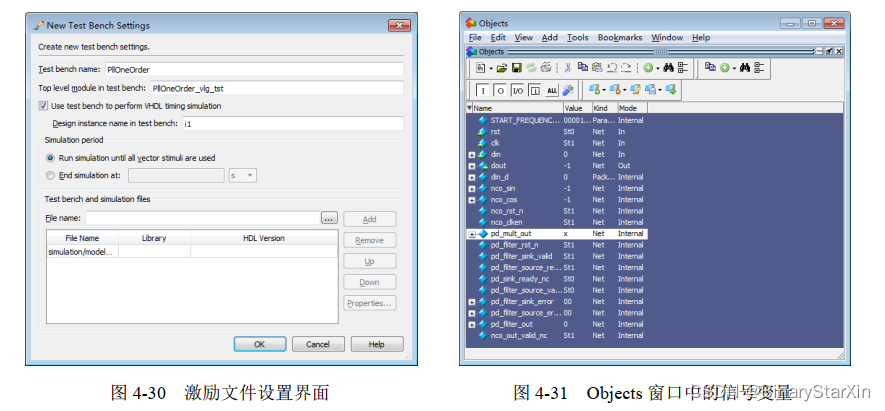

在采用 ModelSim 仿真之前,还需要对仿真工具及参数进行简单设置。单击 Quartus II 软件工作界面菜单“ Assignments→settings”选项,打开设置对话框,如图 4-28 所示。选中“ EDA Tool Settings”选项,设置“ Simulation”的“ Tool Name”为Modelsim-Alrtera,“ Format( s)”为 Verilog HDL;选中“ EDA Tool Settings→Simulation”选项,打开仿真界面设置,如图 4-29 所示。在“ Simulation”设置界面中将“ Tool name”设置为 Modelsim-Altera,在“ NativeLink settings” 中单击“ Test Benches…” 按钮,新建 Test Bench文件,打开图 4-30 所示的 TestBench 设置界面。

单击“ Test bench and simulation files”右侧的浏览按钮,选中编写好的激励文件PllOneOrder.vt,单击“ Add”按钮添加进当前环境中。选中“ Use test bench to perform VHDL

timing simulation”,设置“ Design instance name in test bench”为“ i1”( i1 是 PllOneOrder.vt中的 PllOneOrder 实例的名称)。在“ Test bench name”中填入激励名称“ PllOneOrder”,在

“ Top level module in test bench”中填入“ PllOneOrder_vlg_tst”,单击“ OK”按钮完成激励参数设置。

单击 Quartus II 软件工作界面菜单“ Tools→Run Simulation Tool→RTL Simulation” 选项,启动 ModelSim 软件进行功能仿真(行为仿真)。程序自动调用 ModelSim 软件进行仿真,且很快弹出一个选择对话框“ Are you sure you want to finish?”。这是因为在 PllOneOrder.vt 文件中我们将仿真结束时间设置为 200 ns,因此很快就完成了 200 ns 的仿真,程序弹出对话框,询问是否需要结束仿真。选择“No”,继续回到 ModelSim 的仿真界面。

这时, 我们会发现波形窗口(wave) 中, 仿真波形只运行了 200 ns 时间, 且输入数据(din)的信号显示为一条红线。这是因为 ModelSim 读取的外部测试数据,必须放置在工程目录中的modelsim 目录下“D:\PllPrograms\Chapter_4\E4_1\PllOneOrder\simulation\modelsim”。将 din.txt文件复制到这个目录下,重新运行仿真程序,可以发现此时波形界面中显示的顶层文件接口信号 rst、 clk、 din、 dout 和 pattern(激励文件中定义的读数据序号)都显示确定的数据值。

对于一阶锁相环电路来讲,上面这几个信号不足以方便地查看环路的锁定情况。我们希望看到对输入信号同步及限幅后的信号( din_d)、 NCO 输出信号( dout)之间的相位变化情况,还要查看鉴相乘法器输出的信号( pd_mult_out) 和鉴相滤波器后的信号( pd_filter_out)

的变化情况。 ModelSim 提供了非常方便的波形信号添加功能。单击 ModelSim 界面中的“ Sim”标签,选中“ i1”模块;单击“ Objects”标签,此时窗口中显示出所有 i1 模块中的信号变量,如图 4-31 所示。选中所要观察的信号( pd_mult_out、pd_filter_out),在单击右键弹出的菜单中选中“ Add Wave”选项,将相应信号添加到波形窗口中。

返回波形显示界面后,单击工具栏上的“ ”( Rull-all)按钮继续仿真,而后单击“ ”( Break)按钮停止仿真,单击工具栏上的“ ”( Zoom In、 Zoom Out、 Zoom Full)调整波形的显示区域。分别右键单击 din_d、 pd_mult_out、 pd_filter_out 信号,在弹出的菜单中依次选中“ Radix→Decimal”设置数值显示为十进制格式;重新分别右键单击 din_d、pd_mult_out、 pd_filter_out 信号,在弹出的菜单中依次选中“ Format→Analog( automatic)”将信号显示为模拟波形,如图 4-32 示。

看到图 4-32 波形,多少有些出乎意料,从鉴相滤波器输入输出信号波形可以看出,鉴相滤波器明显滤除了高频分量,且输出信号的频率受鉴相滤波器输出信号的控制。但环路没有如我们预想的那样锁定!反复检查一下 FPGA 工程设计代码,以及各 IP 核的参数设计,实在找不出错在哪里。

回想一下第 3 采用 SystemView 仿真一阶环的内容,造成环路不锁定的原因,最可能是鉴相滤波器带宽或环路增益设置不合理。鉴相滤波器带宽过渡带设计为 300~600 Hz 应该没有什么问题,因此最有可能的是环路增益过大的原因。在模拟一阶锁相环中,根据第3 的仿真结论,只要环路增益小于 VCO 的固有振荡频率即可,但在本实例设计的数字一阶锁相环中,这个结论仍然适合吗?按照这个思路,我们修改一下环路增益参数,看看结果如何?

改变一阶数字锁相环的增益的方法很多,可以通过增加 NCO 的相位字位宽来降低增益,或者降低乘法器、低通滤波器的有效位宽来降低总增益。根据前面的讨论,鉴相乘法器输出有效位宽为 19 比特,即取的是低 9 比特。我们将乘法结果向右移一位,即直接取高 19比特,则相当于增益降低了一倍。这样,在程序代码上的更改更小一些。具体来讲,将程序 PllOneOrder.v 中的

.ast_sink_data (pd_mult_out[18:0]),//取乘法结果的低 19 位

修改为

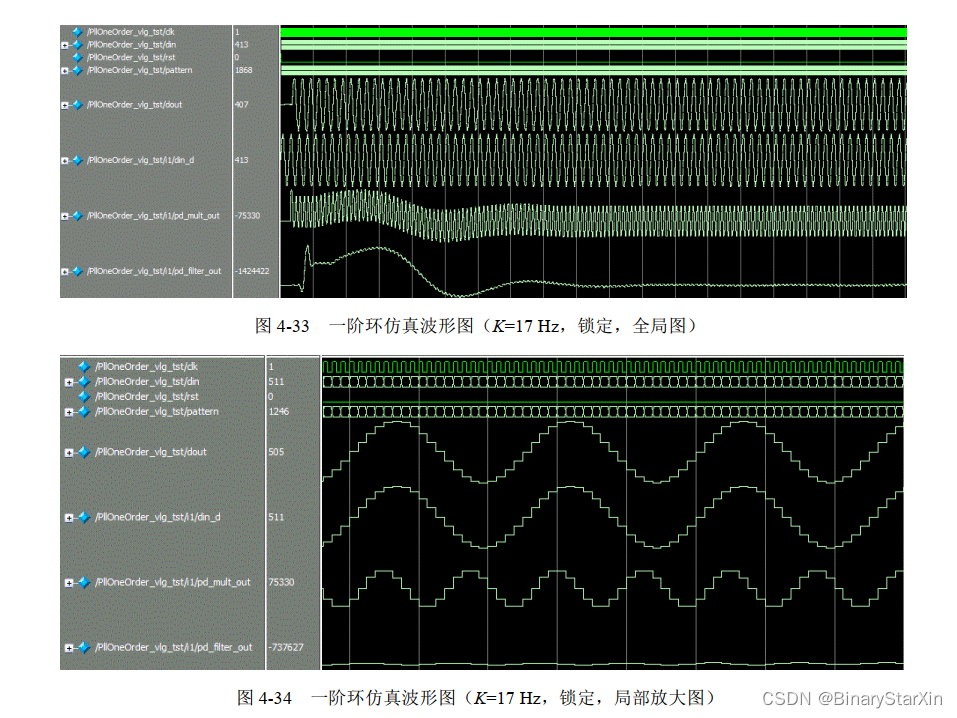

.ast_sink_data (pd_mult_out[19:1]),//取乘法结果的高 19 位重新进行仿真测试,得到图 4-33、图 3-34 所示的波形图。

环路完美锁定!

从图中可以看出,图 4-33 鉴相滤波器输出的信号很快收敛成一条近似直线,从图 4-34可以看出,锁定后 din_d 与 dout 完全同频同相(观察两路信号的峰值点是否对齐)。

为什么一阶数字锁相环路的最大环路增益相比模拟环有明显下降呢?可以简单地解释为,数字环路中的乘法器、低通滤波器等环路部件具有明显的处理时延。好在最大增益值是相对于 NCO 的固有频率而言的,也就是说,一阶环路的最大增益与 NCO 的固有频率成一定比例关系(在本例中,最大增益约为固有频率的 4%)。随着 NCO 固有频率的增加,比如达到 1 MHz,则最大增益可达 40 kHz(捕获带宽),这已经是一个很大的范围。本书后面章节还会讲到,通常来讲,锁相环更关注锁定后的稳态相差,在需要较大捕获带宽的情况下,通常采用其他的频率辅助捕获手段。

4.5.4 继续仿真分析环路性能

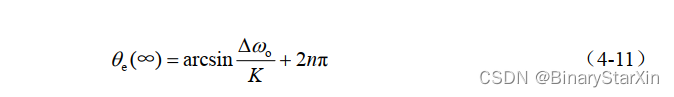

经过我们的努力,一阶锁相环电路已能够正确地锁定。其中的环路增益( K=17 Hz)是我们通过理论设计出来的结果,接下来我们还需要通过进一步仿真来实际测试一下这个增益值。如何测试呢?根据一阶环的工作原理,锁定后的相差

在 MATLAB 仿真测试数据时,输入信号为 400 Hz 的单频信号,采样频率为 8 000 Hz,因此每个波形周期采样 20 个点,每两个点之间的相位为 18°。因此,我们可以通过设定不同的初始频差,通过观察 ModelSim 波形中的相差,测试环路增益值 K 。需要注意的是,式

( 4-11)中,如果频差用 rad/s 为单位,则增益值也必须采用 rad/s。

首先来测试一下环路锁定的极限频差,即当频差与增益相同时,环路中的输入信号与NCO 信号的相位相差为 90°。

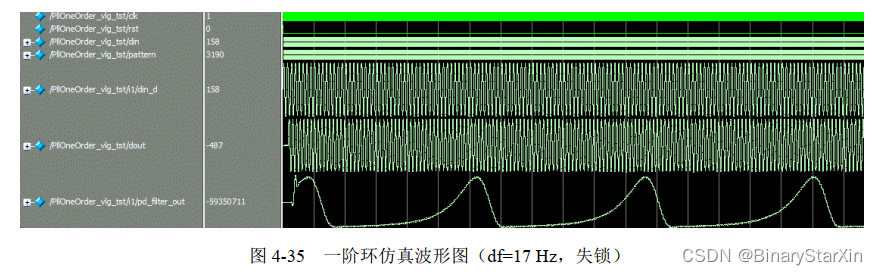

为此,我们调整顶层 FPGA 文件 PllOneOrder.v 中的部分代码, 改变 NCO 初始频率常量( START_FREQUENCY)的值,来实现改变初始频差的目的。根据式( 4-4),当 NCO 输出频率为 417 Hz 时, START_FREQUENCY= 1 791 001 362。修改初始频率值后,重新仿真,如图 4-35 所示。

从波形图看,环路竟然不能稳定地锁定!但对比一下图 3-32 与图 3-35 可以看出, 图 4-35

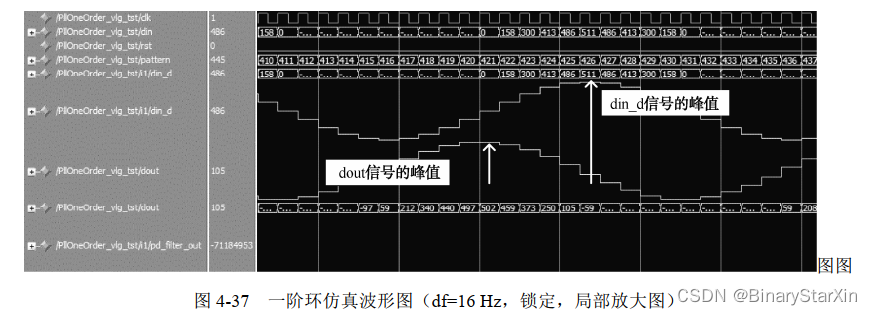

明显有一个更长的锁定过程。这并不是什么错误,仅仅是一点误差罢了。将初始频差减小一点,设置成 16 Hz, START_FREQUENCY= 1 791 001 362。再重新仿真,环路稳定锁定!调整仿真波形大小,观察 din_d 与 dout 信号之间的相位差,如图 4-36、图 4-37 所示。从图中可以看出, din_d 与 dout 信号之间的相位差刚好为 5 个采样点,每个采样点相差18°,正好相差 90°。据此,可以初步确定环路增益在 16~17 Hz 之间。

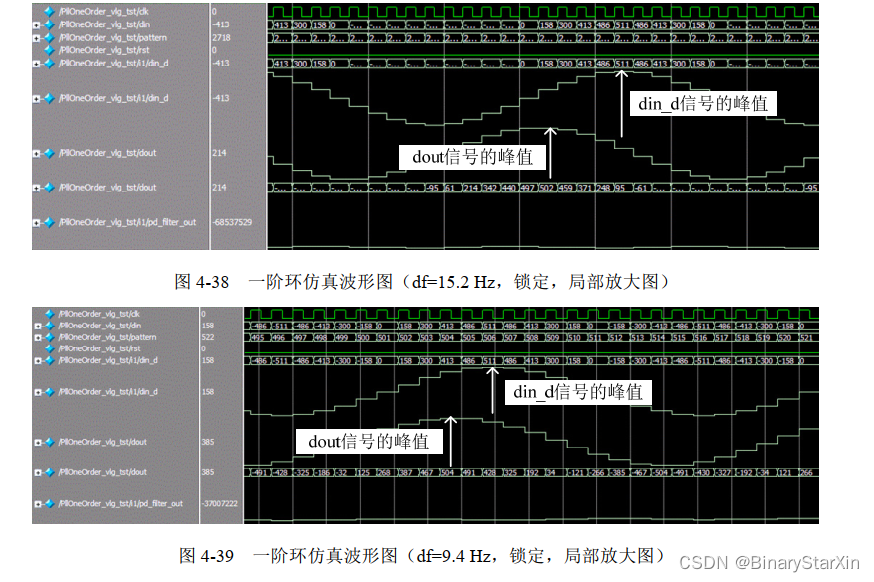

再进一步,根据确定出的环路增益(取 16 Hz),分别设置频差为 15.2 Hz、 9.4 Hz,查看仿真结果是否分别出现相差 4 个采样点(相差为 72°)和 2 个采样点(相差为 36°)。从图 4-38、图 4-39 可以看出,仿真结果与设计值完全一致。这样,我们可以确切地认为环路的增益为 16~17Hz。

再进一步,根据确定出的环路增益(取 16 Hz),分别设置频差为 15.2 Hz、 9.4 Hz,查看仿真结果是否分别出现相差 4 个采样点(相差为 72°)和 2 个采样点(相差为 36°)。从图 4-38、图 4-39 可以看出,仿真结果与设计值完全一致。这样,我们可以确切地认为环路的增益为 16~17Hz。

前几章,我们主要从环路基本概念的角度,对环路进行了分析和仿真,从而初步建立起对锁相环路工作机理的认识。要深入研究锁相环技术,必须建立环路的系统模型,而后采用数学方法对模型进行精确的分析。一讲到数学分析,估计很多读者就开始感觉“头大”了。但是,要想深入掌握它,无论多“头大”的事,除了想办法克服它,并没有什么其他的捷径可走。回想一下小学时学过的一句谚语:“困难像弹簧,你强它就弱,你弱它就强。”先给自己鼓下劲,也许那些看似复杂的分析,并没有想象得那么难以理解。就好比已经发展到无比复杂的计算机科学,其最基本的原理仅仅是由“ 0”和“ 1”为元素而形成的布尔代数一样。

这一章我们从最基本的线性时不变系统知识开始,逐步建立起锁相环路的数学模型,为后续的分析打下坚实的基础。在建立模型的过程中,我们会发现,所有的知识,所有的公式其实都是在大学的一些基础课程中学习过的。

5.1 线性时不变系统

5.1.1 线性系统的概念

我们在 3.1.3 节讨论鉴相器特性时,提到过,我们总希望在分析问题时能够有更为简单的模型,对于鉴相器来讲,如果鉴相特性具有线性特性是最好的。为什么具有线性特性的模型是最好分析的模型呢?

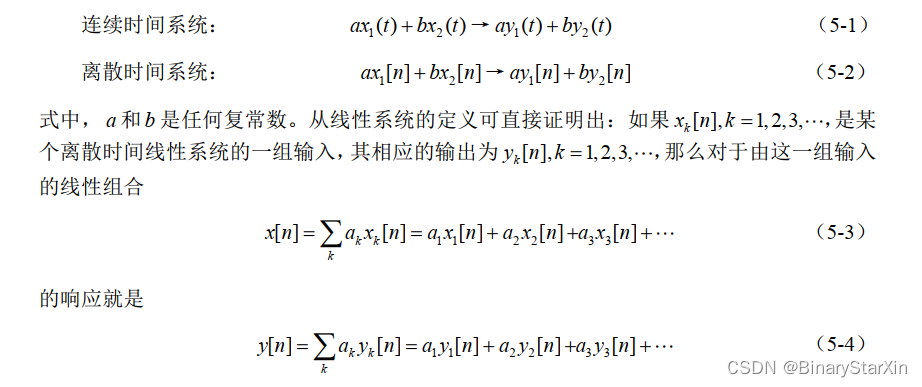

我们先从最简单的问题入手。什么是线性?其实线性的概念是我们在中学的数学课上学习到的。所谓“线性”,就是具有直线的特性。线性方程,就是方程中任一个变量都为一次幂的代数方程,如 y =2 x +3。因为这种方程的图形为一条直线,所以称为线性方程。对于一个系统来讲,线性系统(连续时间或离散时间)是指满足可加性和齐次性的系统。用数学方式表示出来,可以简单地写成

这个很重要的事实就称为叠加性质,对连续时间和离散时间线性系统都成立。按照线性系统的定义,我们来考察一下前面提到的线性方程 y = 2 x +3 所表示系统,这个系统可写成

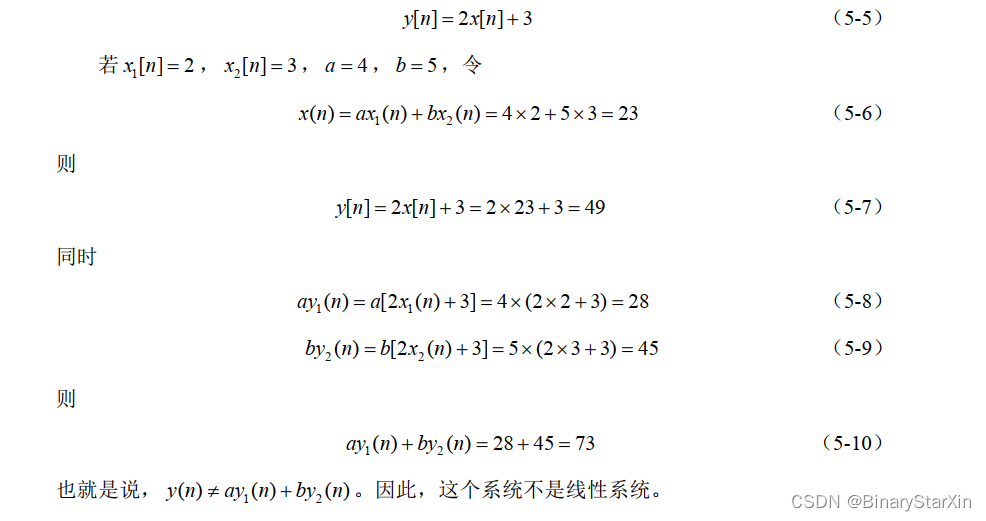

可以用线性方程表示的系统,不一定是线性系统?是的。这个系统之所以不是线性系统,是因为方程中有一项与输入量无关的常量(常数 3)。这样的系统可以表示为一个线性系统与另一个等于该系统零输入响应的信号之和。对于前面考察的这个系统,可以用图 5-1来表示。

事实上,在连续时间和离散时间系统中存在着大量的一类系统,也就是系统的总输出由一个线性系统的响应与一个零输入响应的叠加来组成,这样的系统相当于一类增量线性系统( Incrementally Linear Systems),即在连续或离散时间系统中,其响应对输入中的变化是线性的。换句话说,对增量线性系统而言,对任意两个输入的响应的差是两个输入差的线性函数(可加的,且齐次性的)。

我们再回想一下第 3 章讨论鉴相器特性时,如果将环路输入相位与 VCO 信号相位采用相同的参考相位,当鉴相器工作在线性区间时, 1( ) t 与2( ) t 之间会相差一个 π/2 固定值,因此,锁相环可以用图 5-2 所示的增量线性系统结构表示。

与线性系统相比,增量线性系统只是在输出端增加了一个常数,因此可以将增量线性系统用线性系统的方法进行分析,得出线性系统的输出响应后,加上一位常量即可。

5.1.2 时不变系统的概念

什么是时不变系统?顾名思义,就是指系统的特性不因时间变化而变化的系统。例如我们用来学习过的绝大多数电路实验板,其中的电阻、电容、电感等元件的特性是不随时间而变化的(实际上,这些元件的特性值会因为使用时间、环境温度等条件产生变化,但在我们使用的很长一段时间内,这种变化是可以忽略不计的), 这个电路系统就是时不变的。我们会预期到:今天用这个电路做一个实验所取得的结果与明天来做同一个实验所取得的结果是相同的。另一方面,如果这个系统中的元件参数随时间产生明显的变化,每次做同样的实验都会产生不同的结果,我们就很难对这个系统进行实验分析了。

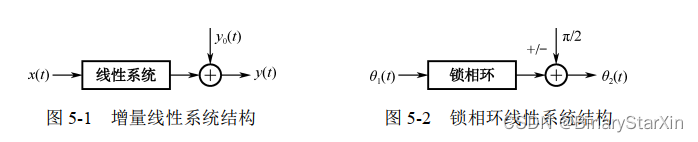

用“信号与系统”课程中学过的语言来描述,如果一个系统的参数和特性不随时间变化,即系统的运算关系在整个运算过程中不随时间变化,则该系统为时不变系统。也就是说,如果系统的输入序列移动 n0 个取样点,则输出也跟着移动 n0 个取样点,且数值保持不变,即满足

容易得出,这个系统不是时不变的。

考察一下时变及时不变系统的差别,可以看出,因为式( 5-15)中有一个时变的增益因子,因此构成一个时变系统;式( 5-13)只有一个常数增益因子,因此构成一个时不变系统。

527

527

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?