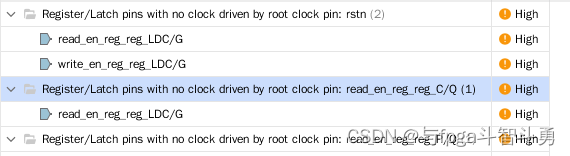

今天在使用vivado进行时序检查时遇到了这样一个问题:Register/Latch pins with no clock driven by root clock pin,它是在no_clock中提示的

通过查看电路图发现这是一个锁存器

锁存器大多数是由于代码写的不符合规范造成的,经过检查,发现工程的代码中存在问题。

原来的代码

always@(posedge clk or negedge rstn)begin

if(rstn=='b0)begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

end

else begin

if(system_state_reg==STATE_WRITE)begin

write_data_reg<=write_data_reg+'b1;

write_addr_reg<=write_addr_reg+'d1;

read_en_reg<='b0;

write_en_reg<='b1;

end

else if(system_state_reg==STATE_READ)begin

read_addr_reg<=read_addr_reg+'d1;

read_en_reg<='b1;

write_en_reg<='b0;

end

else if(system_state_reg==STATE_IDLE)begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

read_en_reg<='b0;

write_en_reg<='b0;

end

else begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

read_en_reg<='b0;

write_en_reg<='b0;

end

end

end

修改后的代码

always@(posedge clk or negedge rstn)begin

if(rstn=='b0)begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

read_en_reg<='b0;

write_en_reg<='b0;

end

else begin

if(system_state_reg==STATE_WRITE)begin

write_data_reg<=write_data_reg+'b1;

write_addr_reg<=write_addr_reg+'d1;

read_en_reg<='b0;

write_en_reg<='b1;

end

else if(system_state_reg==STATE_READ)begin

read_addr_reg<=read_addr_reg+'d1;

read_en_reg<='b1;

write_en_reg<='b0;

end

else if(system_state_reg==STATE_IDLE)begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

read_en_reg<='b0;

write_en_reg<='b0;

end

else begin

write_data_reg<='b0;

read_addr_reg<='d0;

write_addr_reg<='d0;

read_en_reg<='b0;

write_en_reg<='b0;

end

end

end

在复位时未对其中的两个寄存器进行复位,锁存器也有可能是由于if else组合写的不全而导致的。

3942

3942

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?