转自:https://blog.csdn.net/yundanfengqing_nuc/article/details/106055702

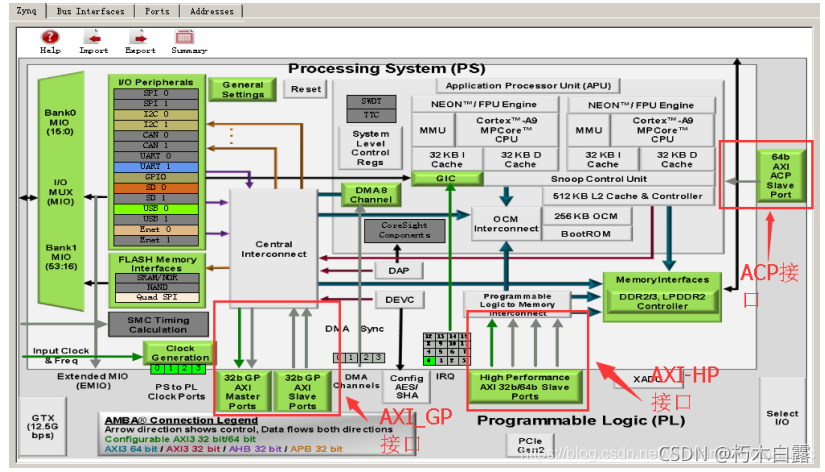

在ZYNQ芯片内部用硬件实现了AXI总线协议,包括9个物理接口,分别为AXI-GP0-AXI-GP3,AXI-HP0~AXI-HP3,AXI-ACP接口。

AXI-ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

AXI-HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)。

AXI-GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

可以看到,只有两个AXI-GP是Master Port,即主机接口,其余7个口都是Slave Port(从机接口)。主机接口具有发起读写的权限,ARM可以利用两个AXI-GP主机接口主动访问PL逻辑,其实就是把PL映射到某个地址,读写PL寄存器如同在读写自己的存储器。其余从机接口就属于被动接口,接受来自PL的读写,逆来顺受。

另外这 9 个 AXI 接口性能也是不同的。 GP 接口是 32 位的低性能接口,理论带宽 600MB/s,而 HP 和 ACP 接口为 64 位高性能接口,理论带宽 1200MB/s。有人会问,为什么高性能接口不做成主机接口呢?这样可以由 ARM 发起高速数据传输。答案是高性能接口根本不需要 ARM CPU来负责数据搬移,真正的搬运工是位于 PL 中的 DMA 控制器。

位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相位的AXI协议。Xilinx在Vivado开发环境里提供现成IP如AXI-DMA,AXI-GPIO,AXI-Dataover,AXI-Stream都实现了相应的接口,使用时直接从Vivado的IP列表中添加即可实现相应的功能。

下面为几个常用的 AXI 接口 IP 的功能介绍:

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

AXI-Datamover:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过这次是完全由 PL 控制的, PS 是完全被动的。

AXI-VDMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过是专门针对视频、图像等二维数据的。

AXI-CDMA:这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。

2546

2546

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?