看论文时的一些疑问和常用的知识:

CFET和MOS的区别:

MOS和FET都是指半导体器件类型:

FET(Field-Effect Transistor)

- 场效应晶体管。

- 通过电场控制电流。

- 包括多种类型,如JFET(结型FET)和MOSFET。

MOS(Metal-Oxide-Semiconductor)

- 一种特定类型的FET。

- MOSFET是最常见的MOS器件。

- 由金属栅极、氧化物绝缘层和半导体材料组成。

区别

- FET是一个更广泛的类别,涵盖所有场效应晶体管。

- MOS专门指使用金属-氧化物-半导体结构的FET,具有更好的开关速度和功耗性能。

简言之就是FET是指场效应晶体管,mos是一种工艺。

CMOS和MOSFET的区别:

A MOSFET is a kind of transistor. A Field Effect Transistor, no less. The MOS means it’s a form of Metal Oxide Semiconductor, whereby the transistor is composed of a metal gate electrode on top of an insulating layer which is itself on top of a semiconductor layer.

MOSFET (Metal Oxide SemiconductorField Effect Transistor) is a switch which can be classified as:

- NMOS (n-channel MOSFET )— enhancement type or depletion type

- PMOS ( p- channel MOSFET)— enhancement type

It consists of either individual NMOS or PMOS transistor.

CMOS is a manufacturing process, and is by some margin the dominant approach to manufacturing semiconductors these days. Before CMOS we had NMOS, and before NMOS we had TTL technology.

SPICE模型

Spice模型是指SPICE(Simulation Program with Integrated Circuit Emphasis)仿真程序使用的半导体器件电路模型。

Spice模型的主要特徴和作用如下:

- Spice模型使用电路元素如電阻、電容器、誘电体等描述器件的物理特性。

- 例如MOS管模型包含阻抗参数、截止电流等多Reach方程參數。

- Spice模型可以反映器件在不同电压、电流条件下的动态变化特性。

- 常用的器件模型包括MOS管模型、BJT模型、Diod模型等。

- Spice模型參數需要根據真實器件和工艺技術測量得出。

- Spice模型文件通常為.model格式,包含在PDK中提供给設計軟件。

- 使用Spice模型可以在電路級進行AC/DC等多種時域和頻域仿真分析。

- 通過匹配實驗數據校正模型參數,提高仿真精度。

總之,Spice模型融合了器件物理特性與电路模擬,為半導體器件在整個設計流程中的電路級分析提供重要參考,是SPICE類工具的核心組成部分之一。

Library Characterization

半导体库参数化(Library Characterization)是一个很重要的过程,它指的是:

-

根据实际生产出的器件样品,利用测试装置获取其电学参数。

-

这些参数包括阈值电压、离子掺杂浓度、导电率等物理量。

-

将获取的实测参数反馈到原有的SPICE模型参数里面。

-

通过修改模型参数,使SPICE仿真结果与实测结果高度匹配。

-

这一过程需要重复多次,调整不同条件下的模型,提高精度。

-

最后生成的SPICE模型就是加入了实际生产参数的“定型模型”。

-

这些定型模型整合进PDK,提供给后续电路设计使用。

这个过程的主要作用有:

-

反映真实生产条件下器件的性能。

-

消除原模型与真实差异,提高仿真精度。

-

给出器件在生产线上可以接受的范围规范。

-

预测电路性能,制定后续优化设计方案。

所以半导体库参数化是PDK质量和工艺精准度的重要保障。

FEOL ,MOL, BEOL

在半导体制造中,FEOL、BEOL、和MOL是指芯片制造过程中的不同阶段,每个阶段涉及特定的层。

FEOL (Front-End of Line)

FEOL是指在晶圆制造的初始阶段,主要涉及晶体管的形成。包括:

- 晶体管层:创建MOSFET等基本器件。

- 栅极层:形成栅极电极,控制器件开关。

- 源漏极层:形成源极和漏极,实现电流通道。

- 绝缘层:使用氧化硅等材料实现器件隔离。

MOL (Middle of Line)

MOL连接FEOL和BEOL部分,主要涉及连接和接触点的形成。

- 接触层:形成金属接触,连接FEOL的器件和BEOL的互连。

- 过渡层:提供从器件到互连层的桥接。

BEOL (Back-End of Line)

BEOL涉及芯片的互连和其他后处理步骤。

- 金属层:多层金属用于实现电路互连。

- 介电层:绝缘金属层间,防止短路。

- 钝化层:保护芯片免受物理和化学损伤。

每个阶段和层在生产中都扮演着至关重要的角色,确保半导体器件的功能和性能。

在半导体制造中,FEOL、MOL和BEOL各个层的材料选择和工艺流程至关重要,确保芯片的功能和性能。

每个层的材料选择和工艺流程

FEOL (Front-End of Line)

-

晶体管层:

- 材料:硅(Si)、应变硅、硅锗(SiGe)。

- 工艺流程:外延生长、光刻、离子注入、蚀刻。

-

栅极层:

- 材料:多晶硅、金属栅(如钛、钨)。

- 工艺流程:热氧化、化学气相沉积(CVD)、光刻、蚀刻。

-

源漏极层:

- 材料:掺杂硅。

- 工艺流程:离子注入、退火。

-

绝缘层:

- 材料:二氧化硅(SiO₂)、高介电常数材料。

- 工艺流程:热氧化、沉积。

MOL (Middle of Line)

-

接触层:

- 材料:钨、钛硅化物。

- 工艺流程:化学机械抛光(CMP)、沉积、蚀刻。

-

过渡层:

- 材料:钛、钛氮化物。

- 工艺流程:CVD、溅射、蚀刻。

BEOL (Back-End of Line)

-

金属层:

- 材料:铜(Cu)、铝(Al)。

- 工艺流程:电镀、CVD、光刻、蚀刻。

-

介电层:

- 材料:低介电常数材料(如SiO₂、SiN)。

- 工艺流程:旋涂、CVD、蚀刻。

-

钝化层:

- 材料:氮化硅(Si₃N₄)、氧化硅。

- 工艺流程:等离子增强CVD(PECVD)、溅射。

每个阶段的材料和工艺选择都经过精心设计,以满足性能、可靠性和制造成本的要求。

在这段话中,gear ratio 是指金属层和鳍片之间的间距比,它用于衡量标准单元中可用的金属轨道数量。详细来说:

- M2 pitch:第二层金属(M2)轨道之间的间距。

- Fin pitch:晶体管中鳍片之间的间距。

Gear Ratio 的含义:

- 计算方法:gear ratio = M2 pitch / Fin pitch

- 用途:该比率用于评估在标准单元中布线的灵活性。

- 意义:

- 更高的gear ratio:表示更多的M2轨道可用,增加布线灵活性。

- 更低的gear ratio:可能限制布线能力,影响复杂电路的实现。

通过这个比率,可以优化设计以满足不同性能和密度的需求。

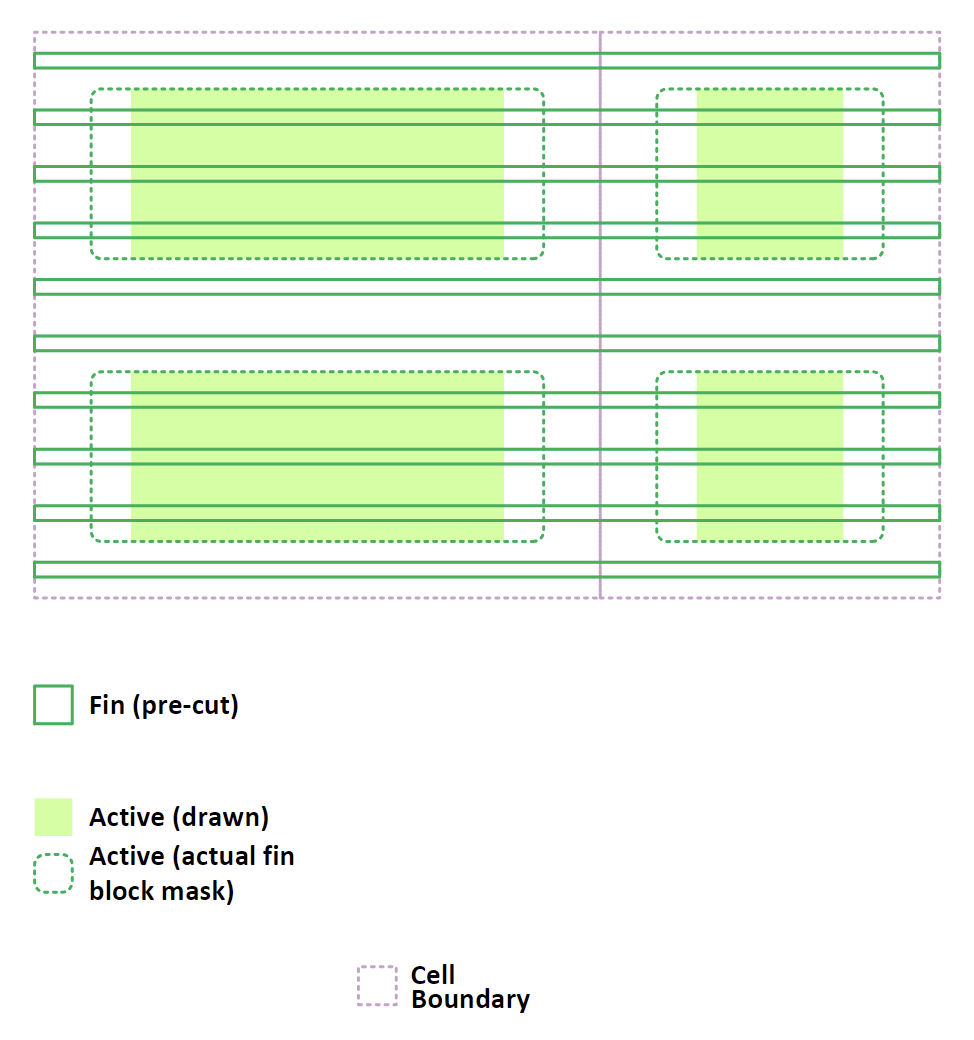

Double Diffusion Break (DDB)

是现代集成电路设计中一种重要的技术,通常用于FinFET和其他先进半导体工艺节点。它主要用于隔离不同类型的晶体管(如PMOS和NMOS晶体管),并防止在它们之间出现不希望的电气耦合或干扰。

所以就是在pmos区和nmos区中间有两个dummy fin!

以下是DDB的功能、用途和工作原理的详细解释:

1. Double Diffusion Break (DDB) 的定义

-

DDB (Double Diffusion Break) 是指在PMOS和NMOS晶体管之间放置的一种结构,用于在物理上和电气上将它们隔离开来。它通过在两种不同类型的扩散区域(n型和p型扩散区)之间引入隔离区域,避免了扩散层的连续性,从而防止寄生效应。

-

DDB不仅仅是一个简单的物理隔离,它实际上是通过在PMOS和NMOS之间插入一段没有扩散的区域,打断扩散层的连续性,从而实现有效的隔离。

2. DDB的作用

DDB的主要作用是隔离不同类型的晶体管(如PMOS和NMOS),并确保它们之间的电气性能保持独立,防止不希望的寄生效应。这对高性能和高密度集成电路尤其重要。

2.1 防止寄生晶体管的形成

- 在CMOS制造工艺中,PMOS和NMOS通常放置在同一硅片上,并且它们的源极和漏极扩散区域会非常接近。如果没有DDB,p型扩散区(PMOS)和n型扩散区(NMOS)之间的区域可能形成寄生晶体管,导致漏电流、噪声和其他不希望的电气效应。DDB通过在它们之间插入一段没有扩散的区域,防止这种寄生晶体管的形成。

2.2 提高电路的噪声隔离能力

- DDB还可以显著提高噪声隔离能力。在高密度集成电路中,PMOS和NMOS晶体管之间的电气噪声耦合可能会严重影响电路性能,特别是在模拟电路和射频电路中。通过使用DDB,PMOS和NMOS之间的噪声干扰可以被显著减少,提升电路的可靠性和性能。

2.3 提高制造工艺的可控性

- DDB在制造过程中还有助于控制扩散区域的精度。在没有DDB的情况下,PMOS和NMOS之间的扩散区域可能会因为光刻和扩散的不精确导致交错或者不规则,从而影响电路的性能。DDB通过明确的物理隔离,可以提高制造工艺的精度,确保扩散区域的边界清晰且可控。

3. DDB的应用场景

在现代半导体工艺中,DDB主要用于以下场景:

3.1 CMOS反相器(Inverter)设计

- 在CMOS反相器中,需要一个PMOS晶体管和一个NMOS晶体管。为了防止这两个晶体管之间的扩散层相互影响,通常在它们之间插入一个DDB,从而实现物理和电气上的隔离。

3.2 高密度集成电路(高性能逻辑电路)

- 在高密度CMOS电路中,DDB可以有效地隔离相邻的PMOS和NMOS,避免它们之间的干扰和寄生效应。这在先进工艺节点(如14nm、7nm、5nm及更小的节点)中尤为重要,因为随着晶体管尺寸的缩小,扩散区域之间的距离也在缩小,寄生效应变得更加显著。

3.3 射频电路和模拟电路

- 在射频电路和模拟电路中,信号的完整性非常重要,任何寄生电容或寄生电阻都会影响电路的性能。DDB的使用可以减少这些寄生效应,确保PMOS和NMOS晶体管之间的电气干扰最小化,从而提高电路的线性度和噪声性能。

4. DDB与其他隔离技术的比较

在集成电路设计中,除了DDB,还有其他几种常用的隔离技术,如Shallow Trench Isolation (STI) 和 Deep Trench Isolation (DTI)。以下是DDB与其他隔离技术的比较:

| 隔离技术 | 功能 | 优点 | 缺点 |

|---|---|---|---|

| DDB | 在不同扩散区之间提供物理和电气隔离 | 有效抑制寄生效应,适用于紧密布局 | 需要额外的布局面积 |

| STI | 通过浅沟槽填充二氧化硅进行隔离 | 工艺成熟,适用于大多数平面工艺 | 在FinFET中可能不够有效 |

| DTI | 通过深沟槽填充二氧化硅进行隔离 | 提供更强的隔离能力,适用于高电压电路 | 成本高,制造复杂 |

相比于传统的STI和DTI,DDB的优势在于它专门为FinFET和其他先进工艺节点设计,可以在高密度集成电路中有效地减少寄生效应,同时保持较低的工艺复杂性。

5. DDB与FinFET的关系

在FinFET中,DDB尤为重要,因为FinFET是三维结构,鳍片(Fin)的形状和布局更加复杂,寄生效应的风险也更高。FinFET的栅极围绕着鳍片的三面,提供更好的电流控制,但也使得不同类型的晶体管之间的扩散区域更容易相互影响。因此,DDB在FinFET工艺中可以有效地隔离PMOS和NMOS,防止它们之间的扩散层交互,并减少由此引发的寄生效应。

总结:

- Double Diffusion Break (DDB) 是一种用于在PMOS和NMOS晶体管之间实现物理和电气隔离的技术,主要通过打断扩散层的连续性来防止寄生效应。

- DDB在高密度集成电路、射频和模拟电路中尤为重要,因为它可以减少噪声和寄生效应,提高电路性能。

- DDB与传统的隔离技术(如STI、DTI)相比,具有更高的灵活性和适应性,尤其适用于现代FinFET工艺节点。

Via Merging(通孔合并)

是集成电路(IC)设计和制造中的一种技术,主要用于优化电路的互连结构。它涉及将多个**通孔(via)**合并为一个更大或更少数量的通孔,以改进电气性能、提高制造的可行性,并减少制造工艺中的一些潜在问题。

1. Via的概念

在集成电路中,通孔(via) 是用于连接不同金属层(通常是金属互连层)的垂直导电路径。例如,在多层金属布线中,通孔用来将一层金属与另一层金属相连,形成电气信号的传输路径。

2. Via Merging(通孔合并) 的定义

Via Merging 是指在IC设计中,将多个较小的通孔合并为更少的、更大的通孔,以优化电路的布局和制造工艺。通过减少通孔的数量或增大通孔的尺寸,设计者可以在不改变电气连接的前提下改进设计的性能和制造的可靠性。

3. Via Merging 的目的和优势

使用Via Merging 技术带来了以下几个主要优势:

3.1 提高电气性能

- 减少电阻和电容:单个通孔的电阻和电容会随着其尺寸和数量的变化而变化。通过合并多个通孔,可以减少整体的电阻和寄生电容,从而提高信号传输的速度并减少电气延迟。

- 增强电流承载能力:在高电流路径中,多个小通孔可能会限制电流的流动,导致电流密度过高,引起发热或其他可靠性问题。合并多个通孔可以增加电流的承载能力,减少电流密度,从而提高电路的可靠性。

3.2 提高制造可行性

- 减少制造缺陷:在实际制造过程中,通孔的尺寸和位置可能会有些许偏差,尤其是在制造工艺节点较小的情况下(如7nm、5nm甚至更小)。通过将多个小通孔合并成一个或几个较大的通孔,可以减少制造过程中的对准误差,从而提高制造的成功率。

- 降低通孔堵塞的风险:在制造过程中,较小的通孔可能会因为填充不完全而导致堵塞或连接不良。合并通孔后,较大的通孔更容易保证填充完全,减少潜在的制造缺陷。

3.3 优化布局面积

- 节省芯片面积:通过合并通孔,可以减少通孔占据的面积,从而节省芯片的版图空间。这对于高密度集成电路设计尤为重要,因为它可以为其他电路元件腾出更多的空间,优化整体电路的布局。

3.4 提高可靠性

- 减少EM(电迁移)效应:电迁移(Electromigration)是高电流密度下的一种失效机制,会导致金属原子迁移并最终破坏电路。通过合并通孔,可以有效地分散电流,降低每个通孔的电流密度,从而减少电迁移的风险,提高电路的长期可靠性。

4. Via Merging 的应用场景

Via Merging 技术在以下几个场景中尤为常见:

4.1 高电流路径

- 在电源和地(VDD、VSS)等需要传输大电流的路径中,通孔的电流承载能力非常重要。通过合并多个通孔,可以显著降低电流密度,确保电路在高负载下的可靠性。

4.2 信号完整性要求较高的路径

- 在高速信号传输路径中,信号的完整性和延迟非常关键。将多个通孔合并为一个更大的通孔,可以减少信号路径上的寄生电阻和电容,从而提高信号传输的速度和完整性。

4.3 先进工艺节点

- 随着半导体工艺节点的缩小(如7nm、5nm及以下),通孔的尺寸也在不断缩小,制造变得更加困难。通过合并通孔,可以减少制造过程中的难度,并提高通孔的填充质量和对准精度。

5. Via Merging 的挑战

虽然Via Merging 带来了诸多优势,但在实际应用中也面临一定的挑战:

5.1 设计复杂度增加

- 在进行通孔合并时,设计者需要仔细平衡通孔的尺寸和数量,以确保电气性能的优化和制造可行性。这可能会增加设计的复杂性,尤其是在高密度电路中。

5.2 热管理问题

- 虽然合并通孔可以提高电流的承载能力,但如果设计不当,可能会导致局部的热效应,增加芯片的温度。因此,设计者需要考虑热管理问题,以确保合并通孔不会导致局部过热。

5.3 布线限制

- 通孔的合并可能会限制某些布线的自由度,尤其是在高密度的布线区域。设计者需要在布线资源和通孔合并之间找到一个平衡点,以确保整体设计的可行性和性能。

6. Via Merging 在先进工艺中的重要性

随着半导体工艺节点的不断缩小,Via Merging 技术变得越来越重要。因为在7nm、5nm及以下的工艺节点中,通孔的尺寸和间距变得非常小,制造难度和缺陷率都显著增加。通过使用Via Merging,可以在不影响电路性能的前提下,简化制造工艺并提高可靠性。

特别是在FinFET和**GAA(Gate-All-Around)**结构中,金属互连的复杂性增加,通孔的优化显得尤为重要。Via Merging 可以帮助这些新型晶体管结构实现更高的电气性能和制造良率。

7. 总结

- Via Merging(通孔合并) 是一种通过合并多个较小通孔来优化电路互连结构的技术。其主要目的是提高电气性能(减少电阻、电容,增强电流承载能力)、提高制造的可靠性(减少对准误差和堵塞风险)、以及节省芯片面积。

- 这种技术在高电流路径、高速信号传输路径 和 先进工艺节点 中尤为常见。

- 虽然Via Merging带来了诸多优势,但需要设计者在电气性能、布线自由度 和 热管理 之间找到合理的平衡点,以确保最终设计的可行性和可靠性。

Via Merging 已成为现代集成电路设计中优化互连结构、提升性能和改进制造工艺的重要手段。

RVT,LVT,SLVT

在现代集成电路(IC)设计中,MOSFET(金属氧化物半导体场效应晶体管)通常根据其阈值电压(Threshold Voltage, Vt)的不同,被分类为RVT、LVT 和 SLVT。这些不同类型的MOSFET用于满足不同的性能、功耗和速度需求。以下是它们的区别和应用场景:

1. RVT(Regular Threshold Voltage)

RVT,即普通阈值电压,是最常见的MOS晶体管类型,具有中等的阈值电压。RVT MOSFETs在性能和功耗之间提供了一个折中平衡。

特点:

- 阈值电压适中:RVT的阈值电压通常在中等水平,这意味着该类型的MOSFET在开启时需要一个适中的栅极电压。

- 功耗适中:RVT MOSFET在关断状态下具有较低的漏电流,因此其静态功耗较低。但由于阈值电压较高,与LVT和SLVT相比,动态功耗(开关时的功耗)相对较高。

- 速度适中:RVT MOSFET的开关速度相对较慢,因为较高的阈值电压意味着晶体管在开启和关闭时需要更多的时间来达到阈值电压。

应用:

- RVT MOSFETs常用于那些需要平衡功耗和性能的逻辑电路中,例如中等性能的数字逻辑和通用标准单元。

- 适合低功耗应用,如嵌入式系统或移动设备的核心部分。

2. LVT(Low Threshold Voltage)

LVT,即低阈值电压的MOSFET,具有较低的阈值电压,因此在同样的栅极电压下能够以更快的速度导通。

特点:

- 阈值电压较低:LVT MOSFET的阈值电压较低,因此在较小的栅极电压下就能开启。这使得它在逻辑电路中具有更高的开关速度。

- 速度更快:由于阈值电压较低,LVT MOSFET的开关速度更快,适合那些要求高性能的电路。

- 功耗较高:LVT的漏电流相对较大,尤其是在关断状态下的静态漏电流更高,因此它的静态功耗会比RVT和HVT(高阈值电压)MOSFET高。

应用:

- LVT MOSFETs通常用于高性能电路,如处理器的核心逻辑、时钟电路,以及其他需要高速度的数字逻辑单元。

- 在一些对功耗不太敏感的区域,如高频运算或高速接口电路中,LVT晶体管是理想选择。

3. SLVT(Super Low Threshold Voltage)

SLVT,即超低阈值电压的MOSFET,具有非常低的阈值电压,因此可以实现极快的开关速度。它通常用于那些对速度要求极高的电路中。

特点:

- 阈值电压非常低:SLVT MOSFET的阈值电压比LVT还要低,使其具有最快的开关速度。

- 速度最快:SLVT MOSFET的开关速度最快,因此适合用于对延迟(latency)要求极高的电路。

- 功耗最高:由于其极低的阈值电压,SLVT MOSFET在关断状态下的漏电流非常大,导致静态功耗最高。因此,SLVT MOSFET通常只在对性能要求极高的电路中使用,而不会大面积应用于整个芯片中。

应用:

- SLVT MOSFETs主要用于关键路径电路,即那些决定整个系统速度的电路部分。它们也用于需要极低延迟的高速逻辑中。

- 由于其高功耗,SLVT通常只在少数对速度要求极高的地方使用,如高速缓存的关键逻辑或时钟驱动电路。

4. 比较与应用总结

| 类型 | 阈值电压 | 开关速度 | 静态功耗(漏电流) | 应用场景 |

|---|---|---|---|---|

| RVT | 中等 | 中等 | 低 | 平衡功耗和性能的逻辑电路,如标准单元库中的常规逻辑 |

| LVT | 低 | 快 | 较高 | 需要高性能的逻辑电路,如处理器核心电路 |

| SLVT | 非常低 | 非常快 | 高 | 关键路径、高速逻辑,对延迟要求极高的电路 |

5. 选择不同阈值电压的原因

在设计集成电路时,设计师会根据电路的速度需求和功耗预算选择不同的MOSFET类型。一般来说,阈值电压越低的MOSFET,开关速度越快,但代价是静态功耗更高。因此,不同类型的MOSFET会被用于不同的电路部分:

- RVT:用于那些不需要极高速度且静态功耗较为敏感的部分,这类电路通常对性能要求不是很高,但需要保持较低的静态功耗。

- LVT:用于那些需要较高性能的部分,比如处理器的计算核心部分,虽然增加了静态功耗,但其快速的开关速度可以保证系统的整体性能。

- SLVT:用于对速度要求极高的关键路径电路,比如高速缓存、内存接口或时钟驱动电路。这类电路对功耗的要求较低,更关注延迟和速度。

6. 实际设计中的平衡

在芯片设计中,通常不会全部采用某一种类型的MOSFET,而是会根据不同部分的需求进行混合使用。比如:

- 在处理器的设计中,关键路径(影响处理器速度的逻辑)可能会使用SLVT或LVT,以提高开关速度,而不涉及关键路径的部分会使用RVT来减少功耗。

- 在低功耗设计中,设计师可能会避免使用SLVT MOSFET,尽量选择RVT或甚至HVT(高阈值电压) MOSFET来降低功耗。

总结

- RVT(Regular Threshold Voltage)MOSFET具有中等的阈值电压,适合平衡功耗和速度的电路应用。

- LVT(Low Threshold Voltage)MOSFET具有较低的阈值电压,提供更高的速度,但伴随着更高的静态功耗,适用于高性能电路。

- SLVT(Super Low Threshold Voltage)MOSFET具有最低的阈值电压,提供最快的开关速度,但静态功耗最大,通常用于关键路径中的高速逻辑。

计中,关键路径(影响处理器速度的逻辑)可能会使用SLVT或LVT,以提高开关速度,而不涉及关键路径的部分会使用RVT来减少功耗。

- 在低功耗设计中,设计师可能会避免使用SLVT MOSFET,尽量选择RVT或甚至HVT(高阈值电压) MOSFET来降低功耗。

总结

- RVT(Regular Threshold Voltage)MOSFET具有中等的阈值电压,适合平衡功耗和速度的电路应用。

- LVT(Low Threshold Voltage)MOSFET具有较低的阈值电压,提供更高的速度,但伴随着更高的静态功耗,适用于高性能电路。

- SLVT(Super Low Threshold Voltage)MOSFET具有最低的阈值电压,提供最快的开关速度,但静态功耗最大,通常用于关键路径中的高速逻辑。

在实际设计中,根据电路的不同需求,设计师会选择合适的MOSFET类型,以在性能和功耗之间达到最佳平衡。

8190

8190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?