ASAP工艺的一些知识理解

为什么要用两个pin namely ‘well’ pin 和PSUB pin?同时什么是WELL TAP,为什么需要它?

In this PDK, there are two layers provided namely well pin and PSUB pin, these are added to the well layer and substrate area of the Figure 3.3. Layout of a minimum sized inverter. standard cell. Their purpose is to simplify the LVS and PEX extraction of the cell by eliminating the need for adding a well tap in the layout.

什么是 Well 和 PSUB?

在 CMOS 工艺中,Well(阱) 和 PSUB(P-Substrate,P型衬底) 是半导体中的基础区域,它们用于定义不同类型的晶体管以及它们的电气隔离。

-

Well(阱):

- 在 CMOS 工艺中,为了制造 NMOS 和 PMOS 晶体管,硅片上会掺杂不同类型的杂质形成 N型或P型区域。

- N-well:这是在 P型衬底(P-Substrate) 上掺入 N 型杂质形成的区域,通常用于制造 PMOS 晶体管。

- P-well:这是在 N型衬底(N-Substrate) 或 N型外延层 上掺入 P 型杂质形成的区域,通常用于制造 NMOS 晶体管。

-

PSUB(P-Substrate,P型衬底):

- P-Substrate(P型衬底) 是整个晶圆的基础区域,它通常是 P 型掺杂的硅材料,所有的器件(包括 N-well 和 P-well)都在这个衬底上制造。

- 在一般的 CMOS 工艺中,NMOS 晶体管直接在 P型衬底上制造,而 PMOS 晶体管则制造在 N-well 中。

什么是 Well Tap?

Well Tap 是一种特殊结构,用于将 Well 或 Substrate(衬底) 与电源或地相连。不同类型的晶体管需要将它们的 Well 或 Substrate 连接到电源或地,以确保电路的稳定性。

- N-well Tap:用于将 N-well 区域连接到 VDD(正电源)。

- P-well Tap 或 P-substrate Tap:用于将 P-well 或 P-Substrate 连接到 VSS(接地)。

通过 Well Tap,可以避免由于浮动 Well 或 Substrate 导致的潜在电气问题,例如漏电流或器件失效。

用处

在早期没有well tap cell的时候,每个标准单元都要一个N井连VDD,P衬底连VSS(接地),但是这种结构很耗费面积,之后一种Tapless cell应运而生,也就是在标准单元上没有well taping;

而为啥之前N井要接 power_supply 而P_sub要接ground 就是为了避免latch_up;

well tap cell的放置一般是在macro placement和 power rail 创建之后,也就是在正式布局之前;

well tap cell 是以规则的间距在每一排中都放置的;tap cell之间的最大距离必须符合特定库的DRC 规则;

解释这段话

在这个 PDK 中,提供了两种层,分别是 Well Pin 和 PSUB Pin,它们被添加到标准单元的 Well 层和 Substrate 区域。它们的目的是简化单元的 LVS 和 PEX 提取,消除了布局中添加 Well Tap 的需要。

这段话的意思是,在这个特定的 PDK(Process Design Kit,工艺设计套件) 中,Well Pin 和 PSUB Pin 是两种特别的标记层,它们用于简化设计中的电路检查和提取步骤。具体来说:

- Well Pin 是与 N-well 或 P-well 关联的层,用来标记这些区域的电气连接。

- PSUB Pin 是与 P-Substrate(P型衬底)关联的层,标记这些区域的电气连接。

通过使用这些特殊的 Well Pin 和 PSUB Pin,可以在版图中直接标记 Well 和 Substrate 的电气连接,而不需要在每个地方手动添加 Well Tap(通常是通过金属与 Well 或 Substrate 的连接来实现)。这种方法简化了版图设计,并且可以让 LVS(Layout Versus Schematic,版图与电路图一致性检查) 和 PEX(Parasitic Extraction,寄生参数提取) 工具自动识别这些区域的电气连接。

为什么这样做可以不用加 Well Tap?

在传统的布局设计中,需要手动添加 Well Tap 来将 N-Well 连接到电源(VDD),将 P-Well 或 P-Substrate 连接到地(VSS)。Well Tap 的作用是防止 Well 或 Substrate 中的电势漂移,从而保证晶体管正常工作。

但是,在这个 PDK 中,Well Pin 和 PSUB Pin 通过在版图中标记这些区域的电气连接,工具就能自动识别这些区域并进行正确的电连接仿真。因此,设计者不再需要在布局中手动添加额外的 Well Tap,而是依靠这些标记层来简化流程。

总结

- Well Pin 和 PSUB Pin 是设计简化工具,它们直接标记 Well 层(如 N-Well)和 P-Substrate 的电气连接,简化了布局设计过程。

- 通过这些标记层,设计者不需要手动添加 Well Tap 来连接 Well 和 Substrate,因为工具已经能够自动识别这些电气连接。

- 这不仅减少了设计中的复杂性,还可以加速 LVS 和 PEX 的验证过程。

这种方法有效地简化了设计流程,确保了布局的一致性,并减少了手动添加 Well Tap 的工作量。

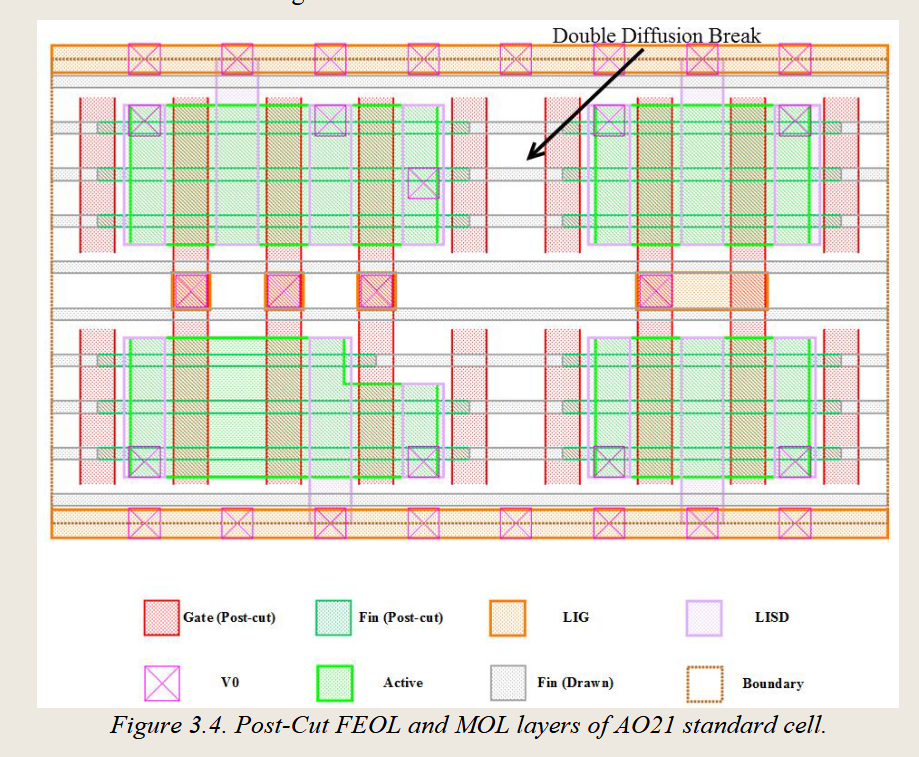

Double Diffusion Break

diffusion break的意义就是例如上面的图的箭头附近,如果没有break’的话,一个gate两边都有fin,就又形成一个transistor了。

TDDB 的基本概念

Time-Dependent Dielectric Breakdown (TDDB),即时依赖介质击穿,是半导体器件中常见的一种失效机制,特别是在现代集成电路的绝缘层(如氧化层)中。它描述了绝缘介质(通常是氧化物)在长时间的电场应力作用下逐渐退化,最终导致绝缘失效的现象。

在 CMOS 器件中,绝缘层(如栅极氧化层或金属层之间的介质)用于隔离导电层。这个绝缘层通常是氧化物材料(如硅氧化物 SiO₂)。然而,在长时间的使用过程中,当在这些绝缘层上施加电场时,氧化物材料会逐渐退化,最终可能导致介质击穿,表现为导电路径的形成,导致器件失效。

TDDB 描述的就是这种由于电场应力随时间推移而导致的氧化物介质退化和击穿现象。

TDDB 失效机制

-

电场应力:

- 当电场施加在绝缘层上(如 MOSFET 的栅极氧化层),某些载流子可能会通过量子隧穿机制穿过氧化物,或者由于缺陷和杂质的存在,部分电荷会被困在氧化物中。这些过程会导致氧化物的结构逐渐受到破坏。

-

缺陷累积:

- 由于电场应力,氧化物中的原子键逐渐被打破,形成缺陷。这些缺陷会逐渐累积,减弱氧化物的绝缘性能。

-

介质击穿:

- 当缺陷累积到一定程度后,氧化物的局部区域会形成导电路径,从而导致介质击穿。这种击穿可能是“软击穿”(Soft Breakdown,SBD),表现为微小的电流泄漏,或者是“硬击穿”(Hard Breakdown,HBD),表现为完全的电流通路,导致器件不可恢复的损坏。

TDDB 失效的影响因素

-

电场强度:

- 施加在氧化物上的电场强度越大,TDDB 的发生会越快。如果器件在高电场条件下工作,电场应力会导致更快的氧化物退化和击穿。

-

氧化物厚度:

- 氧化物层越薄,TDDB 的失效时间会越短。这是因为薄氧化物中的缺陷积累速度更快,且薄氧化物更容易受到电场应力的影响。随着半导体工艺节点的缩小,栅极氧化层的厚度也在不断减小,使得 TDDB 变得更加显著。

-

温度:

- 温度升高会加速氧化物中的缺陷生成和迁移,从而加速 TDDB 失效。因此,器件在高温条件下工作时,TDDB 失效可能会更早发生。

-

电荷捕获和陷阱:

- 在氧化物层中,电荷捕获和陷阱的存在会加速损伤的累积。捕获的电荷会导致局部电场增强,从而加速氧化物的退化。

TDDB 的测试和建模

为了评估集成电路中氧化物层的可靠性,业界通常会进行 TDDB 寿命测试。在这种测试中,器件的氧化物层会被施加高电压加速老化,以模拟实际使用中的长期电场应力。通过这种加速测试,可以预测氧化物层的寿命。

常见的预测模型包括:

-

Power Law Model(幂律模型):该模型假设氧化物的击穿时间与施加电场的强度成幂律关系。电场越强,击穿时间越短。

-

Thermochemical Model(热化学模型):该模型考虑了电场和温度共同作用下的介质击穿行为,假设氧化物中的缺陷随着时间的增加逐渐累积,最终导致击穿。

TDDB 的重要性

随着半导体工艺节点的不断缩小,栅极氧化层和金属间介质的厚度也在减少,使得 TDDB 成为影响器件可靠性的重要因素。特别是在以下场景中,TDDB 的影响尤为重要:

-

高性能计算和数据中心:这些系统往往长时间运行,且工作电压较高,TDDB 可能成为系统失效的主要原因之一。

-

汽车电子:汽车电子元件需要在高温和恶劣环境中工作,TDDB 失效可能会大幅缩短器件寿命。

-

移动设备和消费电子:虽然这些设备的工作电压相对较低,但由于长期使用,TDDB 失效仍然是需要考虑的设计因素。

如何减轻 TDDB 风险

为了减轻 TDDB 对器件寿命的影响,通常采取以下措施:

-

降低工作电压:通过降低器件的工作电压,可以减小电场强度,延缓氧化物的退化。

-

优化氧化物材料和工艺:通过选择更高质量、更耐久的氧化物材料,可以提高器件的抗击穿能力。

-

加强设计冗余:在设计中引入冗余电路或容错机制,当某些器件因为 TDDB 失效时,系统仍然能够继续运行。

-

使用更厚的氧化物:虽然工艺节点的缩小往往要求更薄的氧化物,但在某些关键电路中,设计者仍然可以选择适当加厚氧化物来提高可靠性。

总结

Time-Dependent Dielectric Breakdown (TDDB) 是指在长时间的电场应力作用下,半导体器件中的氧化物或绝缘层逐渐退化,最终发生介质击穿的现象。TDDB 主要受电场强度、氧化物厚度、温度等因素影响,随着半导体技术的进步,特别是在 FinFET 和其他先进工艺节点中,TDDB 已成为影响器件长期可靠性的重要问题。

kdown (TDDB)** 是指在长时间的电场应力作用下,半导体器件中的氧化物或绝缘层逐渐退化,最终发生介质击穿的现象。TDDB 主要受电场强度、氧化物厚度、温度等因素影响,随着半导体技术的进步,特别是在 FinFET 和其他先进工艺节点中,TDDB 已成为影响器件长期可靠性的重要问题。

8676

8676

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?