名称:基于FPGA的BCD码加法器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

BCD码加法器

采用DE2核心FPGA开发板,设计一个BCD码加法程序通过编程设计十进制求和电路,输入为两个2位BCD码加数A和B,低位进位端 cairy-in,,输出为两个加数的和(用三位BCD码表示)S2SlS0,注意处理和的最 大值:S2S1S0=99+99+1=199。

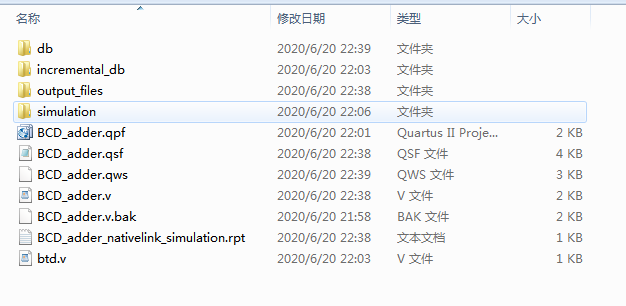

1. 工程文件

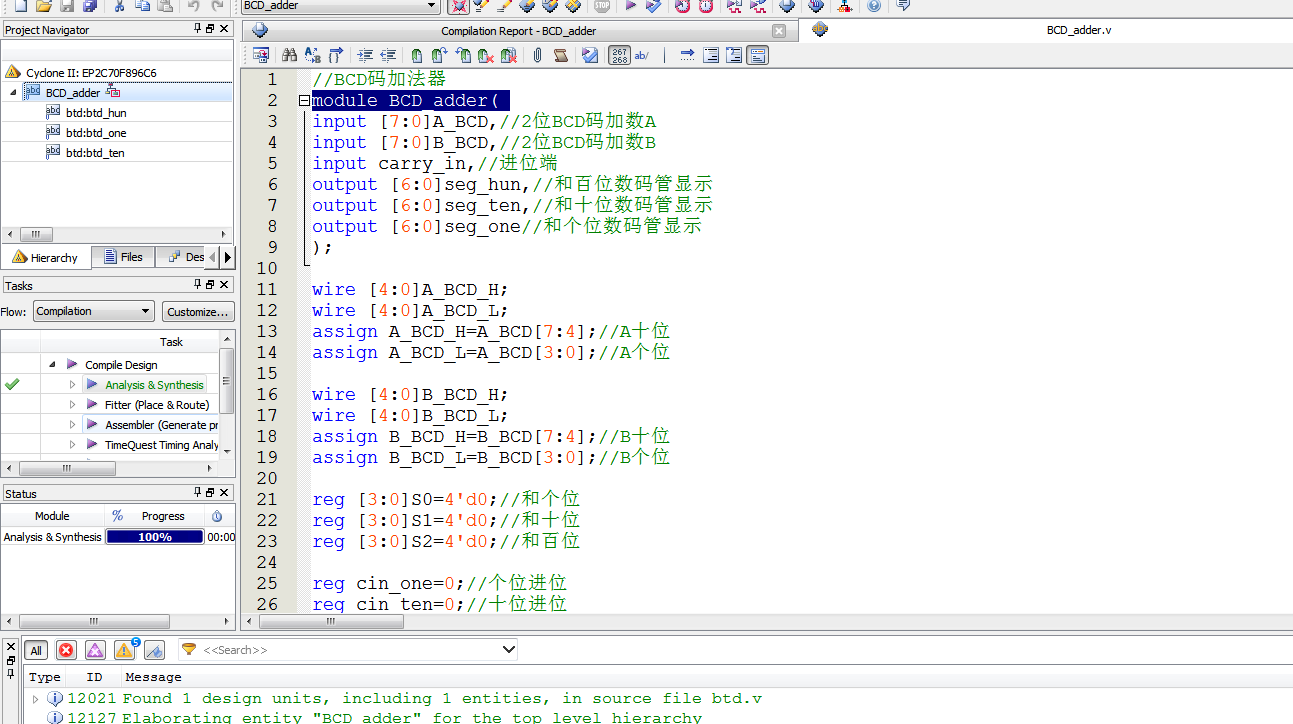

2. 程序文件

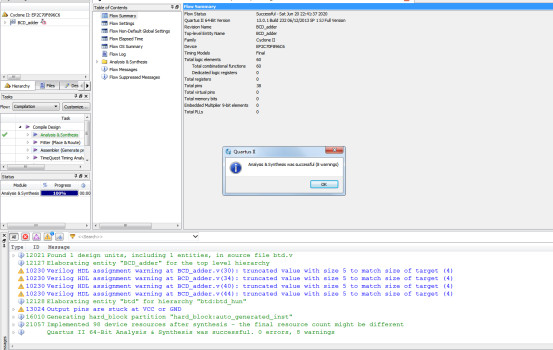

3. 程序编译

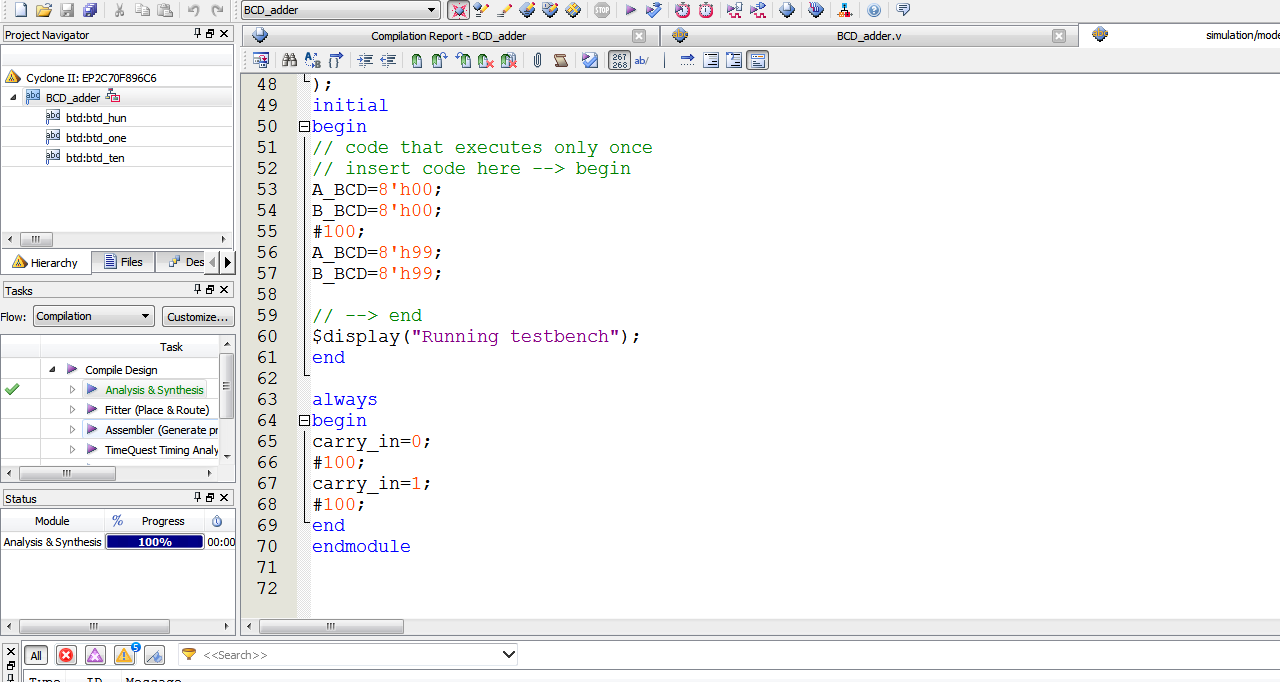

4. Testbench

5. 仿真图

部分代码展示:

//BCD码加法器 module BCD_adder( input [7:0]A_BCD,//2位BCD码加数A input [7:0]B_BCD,//2位BCD码加数B input carry_in,//进位端 output [6:0]seg_hun,//和百位数码管显示 output [6:0]seg_ten,//和十位数码管显示 output [6:0]seg_one//和个位数码管显示 ); wire [4:0]A_BCD_H; wire [4:0]A_BCD_L; assign A_BCD_H=A_BCD[7:4];//A十位 assign A_BCD_L=A_BCD[3:0];//A个位 wire [4:0]B_BCD_H; wire [4:0]B_BCD_L; assign B_BCD_H=B_BCD[7:4];//B十位 assign B_BCD_L=B_BCD[3:0];//B个位 reg [3:0]S0=4'd0;//和个位 reg [3:0]S1=4'd0;//和十位 reg [3:0]S2=4'd0;//和百位 reg cin_one=0;//个位进位 reg cin_ten=0;//十位进位 always@(*) if((carry_in+A_BCD_L+B_BCD_L)>=5'd10)begin//判断个位相加是否有进位 S0<=(carry_in+A_BCD_L+B_BCD_L)-5'd10;//减10 cin_one<=1;//个位进位 end else begin S0<=(carry_in+A_BCD_L+B_BCD_L);//个位和 cin_one<=0; end

源代码

扫描文章末尾的公众号二维码

939

939

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?