使用 SRAM 可以满足最小化高速缓存访问时间的需要。 然而,当缓存未命中时,我们需要尽快将数据从主存中移出,这就需要高带宽内存。 这种高内存带宽可以通过将构成主内存的许多 DRAM 芯片组织成多个内存条并使内存总线更宽来实现,或者两者兼而有之。

高带宽内存是一种利用3D堆栈工艺将多个DRAM芯片垂直堆叠在一起的内存技术,可以提供高达1TB/s的带宽,适用于高性能计算、人工智能、图形处理等领域。高带宽内存与传统的DDR内存相比,具有以下优势:

体积更小,可以节省空间和成本。

能耗更低,每比特功耗只有DDR的一半左右。

带宽更高,可以满足大数据和并行计算的需求。

兼容性更好,可以与不同类型的处理器配合使用。ps:DDR是一种内存技术,全称为双倍速率同步动态随机存取存储器(Double Data Rate Synchronous Dynamic Random Access Memory)。它的特点是在每个时钟周期内能够传输两次数据,从而提高了内存的数据传输率。DDR主要用于个人电脑和服务器等设备的内存条,也有一些低功耗的版本用于移动设备。

随着现在广泛用于闪存和 DRAM 中的突发传输存储器的引入,存储器延迟使用两种度量来引用——访问时间和循环时间。 访问时间是请求读取和所需字到达之间的时间,循环时间是不相关的内存请求之间的最短时间。

可以这样理解访问时间和循环时间的区别:访问时间是从发出请求到收到响应所花费的总时长,循环时间是从发出请求到可以发出下一个请求所花费的总时长。访问时间和循环时间都取决于内存的结构、工作方式和时钟频率等因素。一般来说,访问时间越短,循环时间越短,内存性能越好。

几乎所有计算机都将 DRAM 用作主存储器,将 SRAM 用作高速缓存,其中一到三层与 CPU 一起集成到处理器芯片上。

SRAM

SRAM是一种内存技术,全称为静态随机存取存储器(Static Random Access Memory)。它的特点是利用触发器(flip-flop)来存储每个数据位,只要有电源供应,就可以保持数据不变,不需要刷新。因此,SRAM的速度比DRAM(动态随机存取存储器)快,功耗也低。但是,SRAM的缺点是每个数据位需要多个晶体管来实现,导致芯片的容量较小,成本也较高。SRAM主要用于CPU的高速缓存(如L1、L2、L3缓存),以及一些特殊的设备和应用。

DRAM 中电路的动态特性要求数据在读取后写回——因此访问时间和循环时间之间存在差异,并且需要刷新。 SRAM 不需要刷新,因此访问时间非常接近循环时间。 SRAM 通常每位使用六个晶体管,以防止信息在读取时受到干扰。 SRAM 仅需极少的电量即可在待机模式下保持电量。

片上高速缓存 SRAM 通常按与高速缓存块大小相匹配的宽度组织,标签与每个块并行存储。 这允许将整个块读出或写入单个周期。 当将未命中后获取的数据写入缓存或写回必须从缓存中逐出的块时,此功能特别有用。 缓存的访问时间(忽略集合关联缓存中的命中检测和选择)与缓存中的块数成正比,而能量消耗取决于缓存中的位数(静态功率)和 块数(动态功率)。 设置关联缓存减少了对内存的初始访问时间,因为内存的大小更小,但增加了命中检测和块选择的时间。

DRAM

DRAM是一种内存技术(Dynamic Random Access Memory)。它的特点是利用电容器来存储每个数据位,但是电容器会漏电,所以需要定期刷新,才能保持数据不变。因此,DRAM的速度比SRAM(静态随机存取存储器)慢,功耗也高。但是,DRAM的优点是每个数据位只需要一个晶体管和一个电容器来实现,导致芯片的容量较大,成本也较低。DRAM主要用于计算机的主存储器,以及一些特殊的设备和应用。

DRAM有不同的类型,如SDRAM(同步动态随机存取存储器),DDR SDRAM(双倍速率同步动态随机存取存储器),RDRAM(Rambus动态随机存取存储器),FPM DRAM(快速页模式动态随机存取存储器),EDO DRAM(扩展数据输出动态随机存取存储器)等。

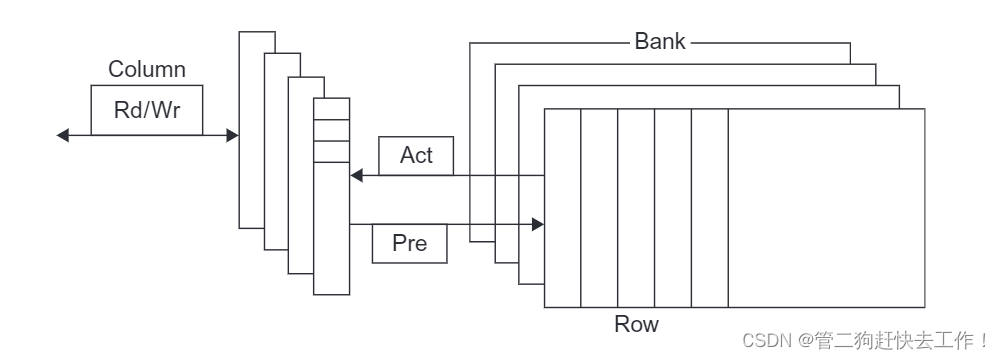

现代 DRAM 是按库组织的,DDR4 最多有 16 个。每个bank由一系列行组成。发送 ACT(激活)命令打开一个存储体和一行并将该行加载到行缓冲区中。当行在缓冲区中时,它可以通过连续的列地址在任何 DRAM 的宽度(在 DDR4 中通常为 4、8 或 16 位)或通过指定块传输和起始地址来传输。 Precharge 命令 (PRE) 关闭 bank 和 row 并准备好进行新的访问。每个命令以及块传输都与时钟同步。

随着早期 DRAM 容量的增长,具有所有必要地址线的封装的成本成为一个问题。 解决方案是多路复用地址线,从而将地址引脚的数量减半。

为了在每个芯片上封装更多位,DRAM 仅使用一个有效充当电容器的晶体管来存储位。 这有两个含义:首先,检测电荷的传感线必须预充电,这将它们设置为逻辑 0 和 1 之间的“中间”,允许存储在电池中的小电荷导致 0 或 1 被检测到读出放大器。 、

此外,为了防止由于单元中的电荷泄漏(假设未读取或写入)而丢失信息,每个位必须定期“刷新”。 因此,内存系统中的每个 DRAM 都必须在特定时间窗口(例如 64 毫秒)内访问每一行。

这个要求意味着内存系统偶尔会不可用,因为它正在发送一个信号告诉每个芯片进行刷新。 刷新的时间是行激活和同时写回行的预充电(这大约需要 2/3 的时间来获取数据,因为不需要列选择),这对于 DRAM 的每一行都是必需的。 因为 DRAM 中的内存矩阵在概念上是正方形的,所以刷新的步数通常是 DRAM 容量的平方根。

SDRAM

SDRAM是一种内存技术(Synchronous Dynamic Random Access Memory)。它的特点是与CPU的时钟同步,可以提高数据传输的效率和速度。SDRAM的速度用MHz来表示,而不是ns2。SDRAM是一种动态随机存取存储器(DRAM),也就是说它需要定期刷新,才能保持数据不变。SDRAM 还允许添加突发传输模式,在这种模式下可以在不指定新列地址的情况下进行多次传输。 SDRAM主要用于计算机的主存储器,以及一些特殊的设备和应用。

SDRAM 引入了 bank 以帮助进行电源管理、改进访问时间并允许对不同 bank 进行交错和重叠访问。对不同 bank 的访问可以相互重叠,并且每个 bank 都有自己的行缓冲区。

为了启动新的访问,DRAM 控制器发送一个存储体和行号(在 SDRAM 中称为激活,以前称为 RAS——行选择)。 该命令打开行并将整行读入缓冲区。 然后可以发送列地址,SDRAM 可以传输一个或多个数据项,具体取决于它是单项请求还是突发请求。 在访问新行之前,必须对存储区进行预充电。 如果该行在同一组中,则可以看到预充电延迟; 但是,如果该行位于另一个存储区中,则关闭该行和预充电可能会与访问新行重叠。 在同步 DRAM 中,这些命令周期中的每一个都需要整数个时钟周期.

DRAM与SDRAM的区别

- DRAM是动态随机访问存储器,SDRAM是同步动态随机访问存储器。DRAM利用电容器存储数据,需要定期刷新,而SDRAM是在DRAM的基础上增加了同步时钟,可以与CPU的时钟同步,提高了数据传输的效率。

- DRAM在两个读周期之间需要等待一段时间,用于充电操作,而SDRAM一个模组有两个bank,在对一个bank充电时,可以操作另一个bank,实现流水线。

- DRAM的传输速率较低,一般为66~133MHz,而SDRAM的传输速率较高,一般为100~200MHz。

- DRAM的工作电压为5V或3.3V,而SDRAM的工作电压为3.3V或2.5V。

GDRAMs

GDRAMs是一种基于 SDRAM 设计的特殊 DRAM,但专为处理图形处理单元的更高带宽需求而定制。 由于图形处理器单元(GPU)需要比 CPU 更高的每个 DRAM 芯片带宽,因此 GDDR 有几个重要的区别:

1. GDDR 具有更广泛的接口:32 位与当前设计中的 4、8 或 16 位相比。

2. GDDR 在数据引脚上具有更高的最大时钟速率。 为了在不产生信号问题的情况下实现更高的传输速率,GDRAM 通常直接连接到 GPU 并通过将它们焊接到电路板上来连接,这与 DRAM 通常排列在可扩展的 DIMM 阵列中不同。

GDDR是一种内存技术,全称为图形双倍速率同步动态随机存取存储器(Graphics Double Data Rate Synchronous Dynamic Random Access Memory)。它是为了设计高端显卡而特别设计的高性能DDR存储器规格,其有专属的工作频率、时钟频率、电压,因此与市面上标准的DDR存储器有所差异,与普通DDR内存不同且不能共用。GDDR的特点是与CPU的时钟同步,可以提高数据传输的效率和速度。GDDR有不同的代数,如GDDR3,GDDR4,GDDR5,GDDR6等,代数越高,一般意味着时钟频率越高,容量越大,电压越低,性能越好。GDDR主要用于显卡的显存,以及一些特殊的设备和应用。

堆叠式 DRAM

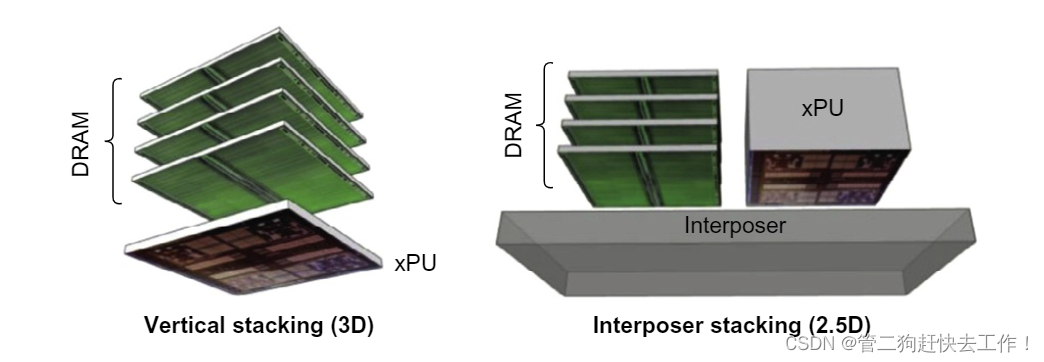

2017 年 DRAM 的创新是封装创新,而不是电路创新。 它将多个 DRAM 以堆叠或相邻的方式嵌入到与处理器相同的封装中。 将 DRAM 和处理器放置在同一封装中可降低访问延迟(通过缩短 DRAM 和处理器之间的延迟)并通过允许更多 处理器和 DRAM 之间更快的连接。

该技术的一种版本使用焊料凸块技术将 DRAM 芯片直接放置在 CPU 芯片上以连接它们。 假设有足够的热管理,多个 DRAM 芯片可以以这种方式堆叠。 另一种方法仅堆叠 DRAM,并使用包含连接的基板(中介层)将它们与 CPU 紧靠在单个封装中。

648

648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?