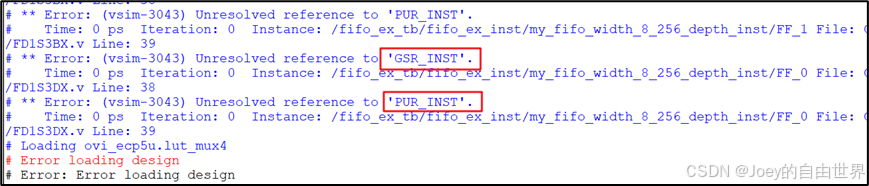

创建fifo IP核,编写好顶层文件和仿真文件,编译无误,设置仿真后,启动仿真,Modelsim会出现如下报错:

信息显示,PUR_INST和GSR_INST两个模块无法解析。

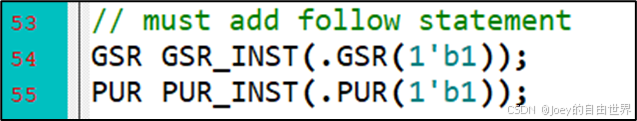

解决方法是,在仿真测试文件中添加如下语句:

重新编译综合后,再次启动仿真,仿真启动成功。

GSR GSR_INST(.GSR(1’b1));

PUR PUR_INST(.PUR(1’b1));

12-03

2503

2503

2503

2503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?