序:

本篇内容,基于阅读J. Bhasker • Rakesh Chadha著作《Static Timing Analysis for Nanometer Designs》后进行的总结以及自己的观点和感想,如有不正确的地方,还请指点。读者有微电子基础将更好理解内容。(图片内容绝大部分直接引用书中)

关于STA的概念,已经提到过很多次了,STA : Static Timing Analysis。做STA都需要准备哪些东西呢?从Timing Check – Timing signoff env中可以看到需要吃sdc/netlist/spef/lib等等。其中的每一项,都可以作为一个大的专题介绍,所以做STA并不是简简单单的run工具,需要对所有的数据输入键的内容非常了解,才能是STA check更加顺遂。书上本章内容,虽然名字写的STA环境配置,但是主要还是对SDC相关内容进行介绍。这一章节就详细的描述一下sdc相关内容。

1. 时钟定义

手机发布的时候,一般会有cpu频率多快,design里面如何去检查可以跑多块的时钟呢?这时候就需要在约束中定义时钟,定义时钟的频率,在这个频率的基础上进行check ,如果meet,那么说明这个design至少可以跑这么快,否则就需要eco 或者降频。

1.1 创建时钟

-

create_clock -name CLK -period 1 -waveform {0,0.5} [get_ports PAD0] -add 表示在PAD0处创建一个名字为CLK,周期为1ns,占空比为0.5的时钟。其中add表示不覆盖,比如还可以在PAD0创建新的其他时钟 -

set_clock_transition -rise/-fall 0.1 [get_clocks CLK] 表示CLK上升下降的trans均为0.1。这是针对于工具不能自动计算出trans的情况,没办法计算delay。所以自动给他设置上trans 。 这个trans在pr之前有用,pr之后因为有了真实的trans,这个就可以删掉。 -

set_clock_uncertainty -setup/hold 0.2 [get_clocks CLK] set_clock_uncertainty -from CLK -to CLK1 -setup/hold 0.2 第一条表示,和CLK相关的所有的timing check,无论setup/hold,uncertainty均设置为0.2 第二条表示,CLK到CLK1之间的path ,setup/hold均设置为0.2 uncertainty由来:由于时钟抖动/偏斜,时钟在工作时候可能不是我们认为的理想时钟的情况,所以这种情况也需要考虑进来,一般的 uncertainty计算根据项目,会和jitter和时钟周期有关系。 -

set_clock_latency 1 -rise/fall [get_clocks CLK] set_clock_latency 1 -rise/fall -source [get_clocks CLK] 第一个表示CLK的时钟网络延迟为1ns ,第二个指时钟源延迟为1ns。source latency指的是从时钟源到时钟定义点,对于创建时钟 来说,就可能是PLL到该时钟的定义点的delay。(对于生成时钟来说,就是master clock和generated clock之间的delay。) source latency在cts后仍然存在,network latency在cts由真实值代替。

1.2. 生成时钟

生成时钟(generate clock),源自于创建时钟(master clock),由master clock分频或者相移得到。为何非要generated clock,直接让master 流下去不行吗?因为对于分频时钟,比如三分频的逻辑,PT工具对于流过逻辑的时钟并不能认知。所以要在三分频逻辑后进行新的时钟定义。

-

create_generated_clock -name CLKDIV3 -master_clock CLK -source [get_PAD0] -divide_by 3 [get_pins reg0/Q] 表示在reg0/Q的位置生成一个CLK的三分频时钟,master_clock表示你想要分频的时钟,因为可能在一个位置create多 个时钟。source表示PAD0位置的波形传输到此处。PAD0的波形和reg0/Q的波形应该是同相位的。 -

当两个时钟同时过mux时候,如下图7-11所示。如果不定义generated clock,那么TCLK和TCLKDIV5都可以流过去,STA工具会 自动check TCLK和CLKDIV5,TCLK和TCLK,TCLKDIV5和TCLKDIV5之间最严格的path ,但是实际情况是,TCLK和CLKDIV5 不可同时存在的。此时可以通过两个clock设置physical_exclusive的group或者两个clock之间的path设置false path解决。

-

create_clock 0.1 [get_ports SYS_CLK] create_generated_clock -name CORE_CLK -divide_by 1 -source SYS_CLK [get_pins UAND1/Z] 当一个clock被clock gate住了,如下图7-12,因为SCTRL不能确保是一个确定的值,那么就需要在UAND1后面generated一个相同的 clock保证流向后面的寄存器的时钟是正常的。

-

create_clock -period 10 -waveform {0 5} [get_ports PCLK] create_generated_clock -name PCLKx2 -source [get_ports PCLK] -multiply_by 2 [get_pins UCLKMULTREG/Q] 不仅仅可以分频,还可以倍频,此表示2倍频。 -

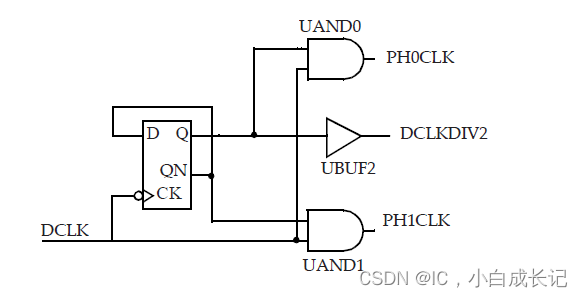

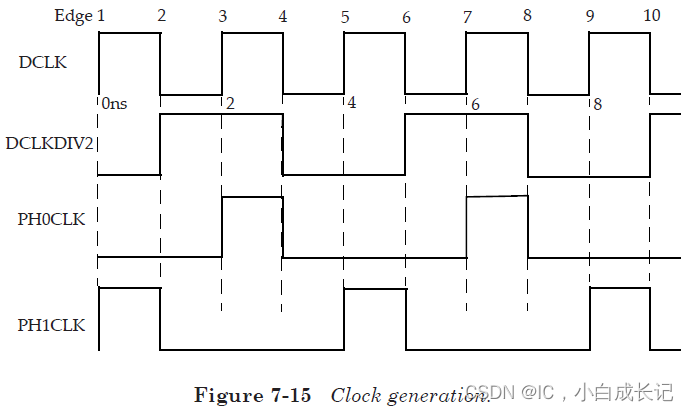

create_clock 2 [get_ports DCLK] create_generated_clock -name DCLKDIV2 -edges {2 4 6} -source DCLK [get_pins UBUF2/Z] create_generated_clock -name PH0CLK -edges {3 4 7} -source DCLK [get_pins UAND0/Z] create_generated_clock -name PH1CLK -edges {1 2 5} -source DCLK [get_pins UAND1/Z] 如下图,针对不同的clock,通过-edges方式进行分频或者占空比调整的处理。-edges 内的数字,表示master的第n个沿

-

create_clock -period 10 -waveform {0 5} [get_ports MIICLK] create_generated_clock -name MIICLKDIV2 -source MIICLK -edges {1 3 5} [get_pins UMIICLKREG/Q] create_generated_clock -name MIIDIV2 -source MIICLK -edges {1 1 5} -edge_shift {0 5 0} [get_pins UMIIDIV/Q] 通过edge_shift调整我们edges沿的相位关系。edge_shift中数值指的是沿移动的delay值。如下图所示:

-

create_clock -period 10 [get_ports CLK] create_generated_clock -name NCLKDIV2 -divide_by 2 -invert -source CLK [get_pins UINVQ/Z] 表示generated一个与master clock反相的二分频时钟。需要注意这种invert以为着逻辑里有真实的inverter才行,否则就是有问题的。

asic中经典的时钟分布图如下所示:

为何新的clock,用generated clock为而不用create clock,因为generated clock 的时钟和master 时钟默认是同一个clock domain,在cts时候会考虑他们的clock skew。另外master clock 和generated clock的时钟源延迟是一致的。

注意 clock不能定义在hier pin上。因为clock定义咋hier pin上之后,因为BE会有clone clock pin的操作去做clock tree,这样会导致clone的pin对应的path没有时钟,这样对STA有影响。

1.3. 虚拟时钟

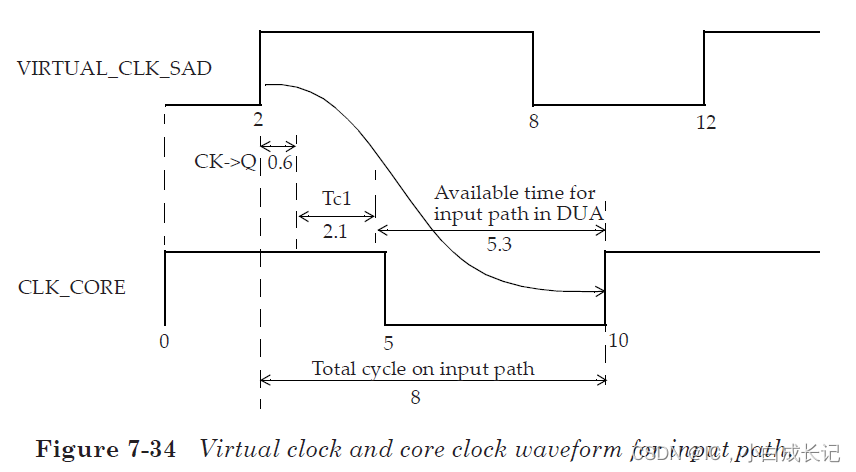

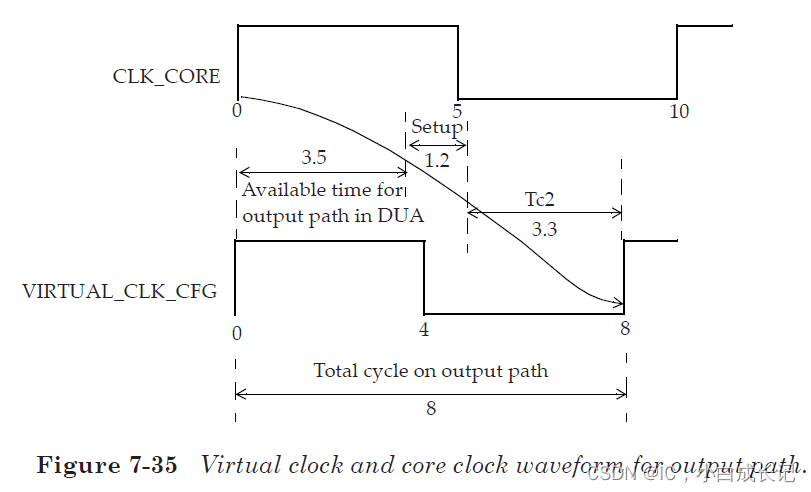

何为虚拟时钟,字面上理解就是假的clock,没有定义到pin或者port上的时钟,多用于STA check时候的IO处的timing check。如下图所示,红色虚线框为对应当前design,虚线框外为IO外部逻辑,在本级design中看不到。

-

create_clock -name VIRTUAL_CLK_SAD -period 10 -waveform {2 8} create_clock -name VIRTUAL_CLK_CFG -period 8 -waveform {0 4} 表示创建两个虚拟时钟 create_clock -period 10 [get_ports CLK_CORE] -

set_input_delay -clock VIRTUAL_CLK_SAD -max 2.7 [get_ports ROW_IN] set_output_delay -clock VIRTUAL_CLK_CFG -max 4.5 [get_ports STATE_O]

其对应的sta检查如下图所示,这里不做详细介绍。

那又为何要有虚拟时钟呢?而不是用内部的clock呢?主要是为了STA check时候的用处

3621

3621

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?