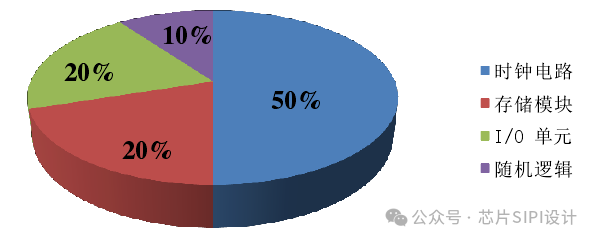

随着集成电路设计的不断发展,在追求性能方面的提升和面积减小之外,芯片的低功耗设计也已成为当下物理设计的主要标准之一。下图为IBM技术研讨会给出的典型芯片中功耗的近似分布,其中时钟电路的功耗比例最高,约占总功耗的50%。随着晶体管数量的增加和时钟频率的提高,电路的功耗特别是时钟网络的功耗也随着变大,所以,在时钟树综合阶段有必要对时钟网络进行功耗分析与优化。

CMOS 电路功耗来源

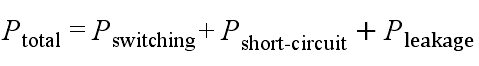

CMOS 电路的功耗主要分为动态功耗和静态功耗,动态功耗指芯片在工作中晶体管处于跳变状态所产生的功耗,主要包括 CMOS 逻辑门输出节点电压产生逻辑转换时,电源对输出节点电容充放电所产生的开关功耗和开关过程中因PMOS 和 NMOS 短时间内同步导通而在电源和地间形成直流通路所产生的短路功耗。静态功耗是指电路处于等待或不激活状态下泄漏电流所产生的功耗,泄露电流主要分为反偏二极管泄漏电流、门栅感应漏极泄漏电流、亚阈值泄漏电流和门栅泄漏电流等。因此,CMOS 电路的总功耗可以表示为:

其中,Pswitching为节点电压逻辑转换时对输出节点电容充放电产生的动态开关功耗;Pshort-circuit为开关过程中因 PMOS 和 NMOS 短时间内同步导通而在电源和地间形成

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

647

647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?