-

什么是ICG?

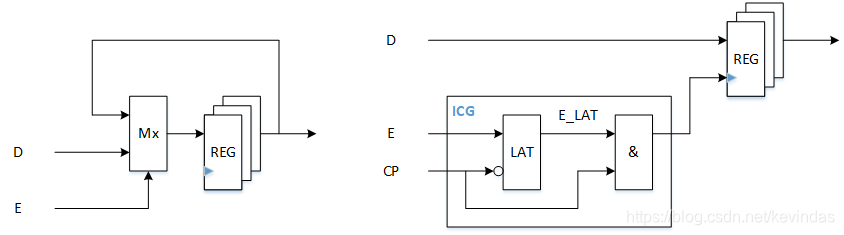

在时序级的设计中,我们经常遇到这样的情况:电路存在一个使能信号E,当使能信号无效时,输出保持。我们通常的做法是使用一个Mux来对输入进行选择(下图左侧)。在综合阶段,可以通过选项将该类型的电路综合成带ICG的电路结构(下图右侧)。ICG单元一般由foundry厂家的库提供,比如TSMC 28nm库该类器件名称为CKLNQDxxx。

-

为什么要使用ICG?

在数字IC设计中,时钟树的功耗占比可能高达30%,而使用ICG电路后,可以从两个方面节省功耗:

-

减少了时钟端的翻转

-

使用ICG的电路资源消耗相对减少

-

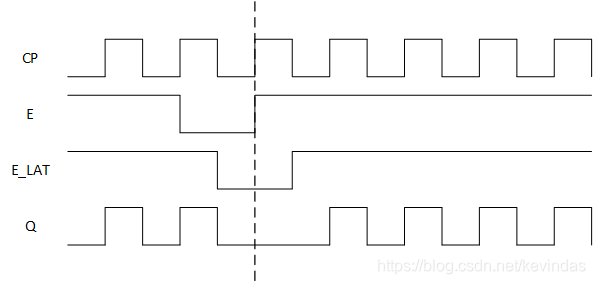

ICG的功能时序

-

ICG的行为描述

reg E_LAT;

always @(*) begin

if(CP == 1'b0)

E_LAT = E;

else

E_LAT = E_LAT;

end

assign Q = CP & E_LAT;-

参考链接

4935

4935

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?