摘要

一、Latch up分类

二、实验机台

三、测试流程与步骤

四、判断依据

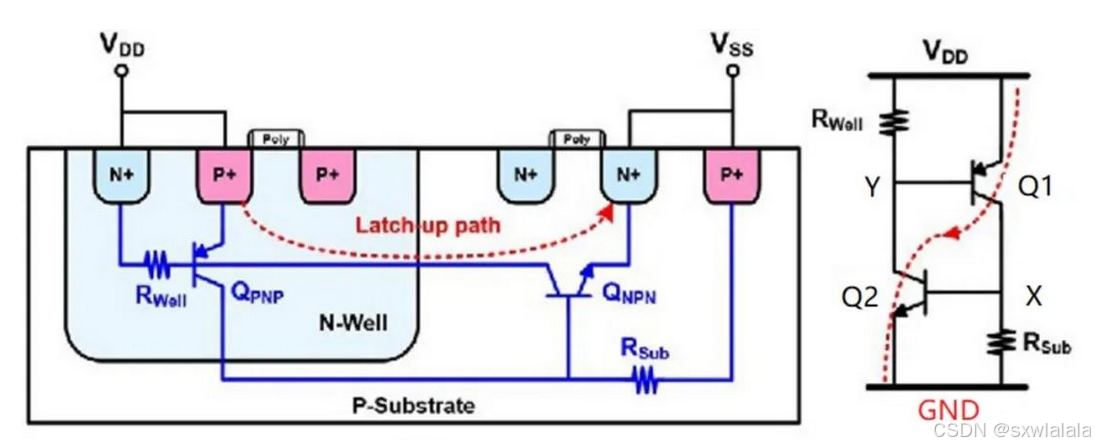

Latch up测试从侧面来说就是SCR结构:触发PNPN结构,形成正反馈回路导致电源和地之间形成低阻抗通路;【大家可以网上搜下正反馈通路,或者我抽空出一篇文章用大白话讲下Latch up原理】

摘要

CSDN和知乎上面有很多的图来介绍在CMOS平面结构,如下图所示(随便找的一张图,如有侵权请联系删除;网上这种结构一搜一大堆 都差不多):

大家记住这张图,脑子里有这张图后就知道里面的PNP和NPN分别对应CMOS结构里面的哪些

P-sub Nwell等等...............

一、Latch up分类:

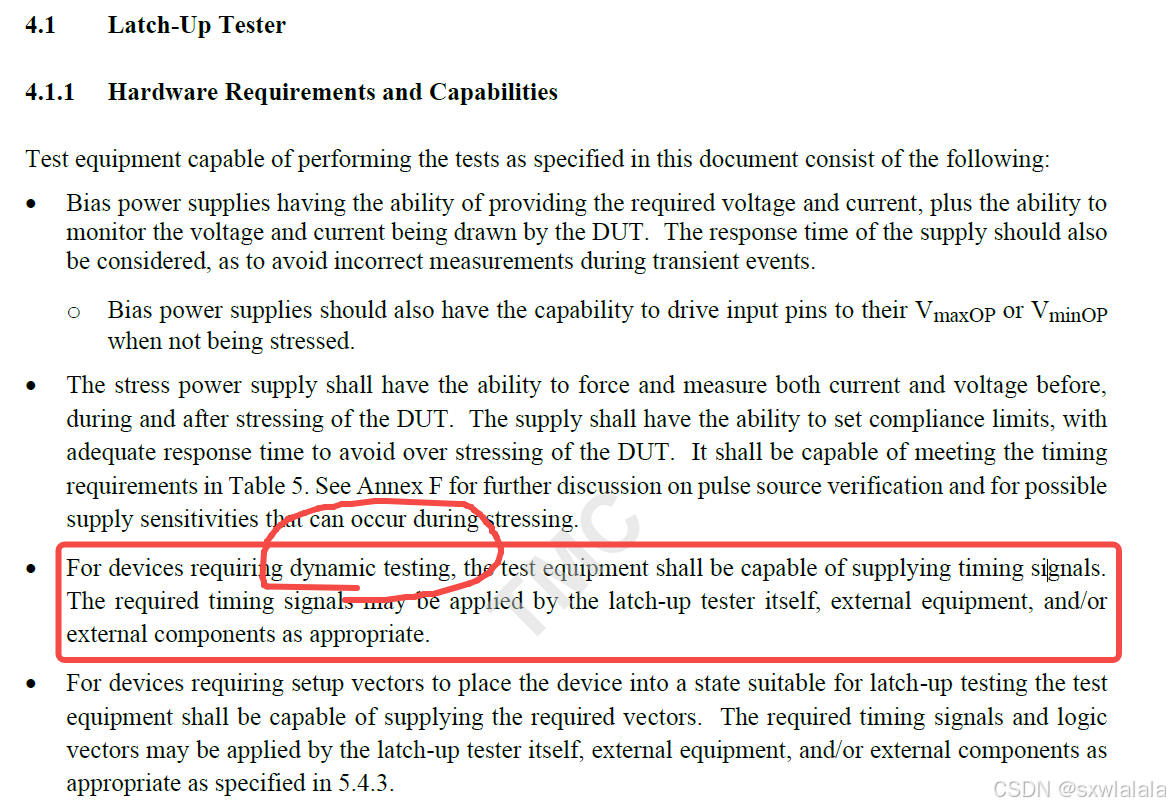

(1)大类分为:静态和dynamic

一般常规的或者说大部分的芯片设计公司都是按照静态来走

而一些大厂或者国外公司,对于可靠性要求高的会按照dynamic来打,他需要制作类似于EVB/ATE的板子来灌pattern,FPGA芯片的话还需要给位流,在芯片工作的情况下进行测试

一般的第三方实验室(季丰,宜特类)都是按照静态来打,dynamic一般设计公司自己执行

(2)小类分为常温测试和高温测试:

工规或者消规,按照Jedec标准来说,没有特别要求高温测试

车规AECQ100里面对于Latchup 则明确提到了ClassⅡ按照标注的最高环境温度进行测试

(3)再小类区分:

I-test和V-test E-test:大家一开始的会理解过电压测试为电压和电流测试;power pin给1.5Vmax测试&IO管脚 ±100/200mA测试

但实际是另外一种说法:就是IO在电流测试不过的情况下,可以用E test来代替

二、实验机台

MK2,MK4,和测HBM的机台是同一种

这和时候突然想到 补充说一句:CDM用的是Orin机台

三、测试流程及步骤:

在测试的时候,首先要置一种状态

Power pin和GND按照正常接法,power要接高,正常电源状态

(1)电压测试power pin的时候,接最大输入电压,测量Inom;对待测芯片施加1.

5Vmax激励,再测量power的I电流

(2)I-test的时候,IO管脚在±电流测试情况下,需要分别置于高低(应用状态)两种状态及测4次,在逻辑状态下施加电流,power pin正常接Vmax

四、判断依据:

即标准里面提到的Inom里面的电流变化,上图也展示了(这里面注意是power电源管脚的电流!!!)

同时如果FT fail 同样也是fail,需要找到root cause

Note:这里注意一点,在测试过程中也会反馈能看到电流,测试过程中的电流也是出发了latch up,只是后面电流也回复正常了;可以向第三方实验室要测试过程中的电流记录

4068

4068

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?