随着集成电路工艺的发展与换代,芯片尺寸变得越来越小,芯片集成度也越来越高,芯片单位面积上实现的电路功能也越来越复杂。集成电路性能的提高,对芯片内部时序约束提出了更高的要求。静态时序分析(Static Timing Analysis)是 VLSI 一个重要的方面,本文主要介绍集成电路静态时序分析需要掌握的基本概念。

目录

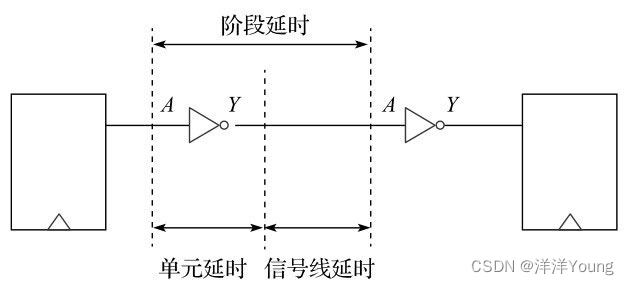

1 阶段延时

阶段延时(stage delay)由单元延时和信号线延时两部分组成,阶段延时是静态时序分析中重要讨论的部分。

(1)单元延时

单元延时指逻辑单元自身逻辑求值的时间。不同的逻辑门单元具有不同的逻辑门延时。

(2)信号线延时

信号线延时指逻辑信号从上一级门单元输出端口,传播到下一级门单元输入端口所经过的延时。

2 组合逻辑单元相关概念

(1)上升时间

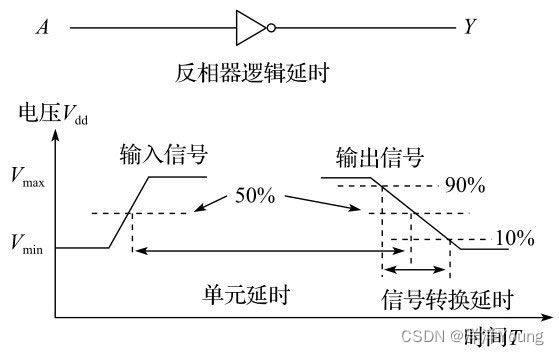

输入或输出信号从低电平转换成高电平所经过的时间,称为上升时间(rising time)。上升时间通常定义为信号电平从 10% Vdd 增加到 90% Vdd 经过的时间。

(2)下降时间

输入或输出信号从高电平转换成低电平所经过的时间,称为下降时间(falling time)。下降时间通常定义为信号电平从 90% Vdd 减小到 10% Vdd 经过的时间。

(3)信号转换延时

信号转换延时(transition delay)指同个端口的信号从低电平转换成高电平,或者从高电平转换成低电平所需要的时间。信号转换延时可以用上述上升时间和下降时间中的最大值或者平均值计算。

(4)逻辑门延时

逻辑门延时(logic gate delay)定义为组合逻辑输入信号改变到输出信号相应改变所经过的时间。通常定义为输入信号变为 50% Vdd 到输出信号变为 50% Vdd 经过的时间。

3 时序逻辑单元相关概念

(1)建立时间

对于时序逻辑单元,为了保证时序单元能正常工作,输入数据应该在时钟有效边沿到来前准备好并保持一段时间,这段时间的最小值称为建立时间(setup time)。

(2)保持时间

对于时序逻辑单元,为了保证时序单元能正常工作,时序单元的输入数据应该在时钟有效边沿到来之后继续维持一段时间,这段时间的最小值称为保持时间(hold time)。

(3)恢复时间

对于时序逻辑单元,为了保证逻辑功能的正确,要求复位或置位信号在时钟有效边沿到来前生效并保持一段时间,这段时间的最小值称为恢复时间(recovery time)。

(4)移除时间

对于时序逻辑单元,为了保证逻辑功能的正确,要求复位或置位信号在时钟有效边沿到来之后继续维持一段时间,这段时间的最小值称为移除时间(removal time)。

2952

2952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?