🔈声明:

🔑未经作者允许,禁止转载

🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈

接下去要做一款芯片的数字部分的功耗分析,方便模拟部分设计ldo的驱动能力。所以先基本了解功耗分析的基础知识。

为什么要降低芯片功耗

- 芯片封装都较小,如果功耗过大,则能量密度太大

- 功耗影响到芯片内部甚至外部的电源网络架构设计

- 高功率带来温度提升,会使性能受影响,时序跑不高

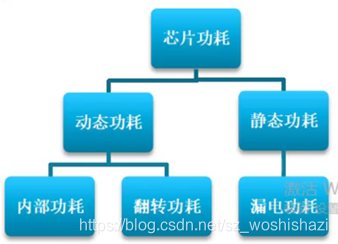

功耗产生原理

漏电功耗:非理想漏电流产生的功耗(例如MOS管关断时,仍然有微小电流存在)

内部功耗:寄生参数充放电产生的功耗

翻转功耗:晶体管负载充放电带来的功耗

其中漏电功耗是静态功耗,内部功耗和翻转功耗是动态功耗。

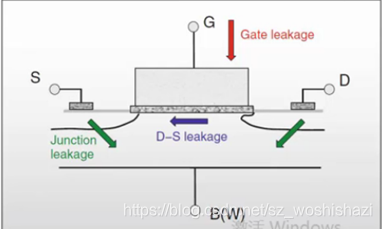

漏电功耗组成

漏电功耗主要包括三个部分:

- 亚阈值电流:CMOS的G级为0时,管子处于截至状态,S和D之间存在微量漏电流。

- 栅极隧穿电流:CMOS的工艺越来越小后,G极的SIO2越来越薄,当薄至和电子,空穴的德布罗意波的波长近似时,电子会击穿栅极,产生栅漏电流。

- 反偏PN节电流:扩散层与衬底之间的漏电电流(非目前主流因素)

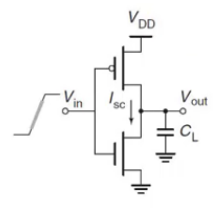

内部功耗组成

内部功耗主要由两个部分组成:

- 短路电流:CMOS管翻转过程中,pMOS和nMOS同时导通产生的电流,大小与输入信号slew和晶体管负载有关。

- 输入端口电流:晶体管输入发生翻转,但是输出来改变,但此时输入信号翻转仍会导致内部产生功耗。

翻转功耗

最常见的功耗,信号翻转产生的功耗。 主要和互联寄生参数和晶体管输入寄生参数有关。

电路功耗计算模型

漏电功耗计算

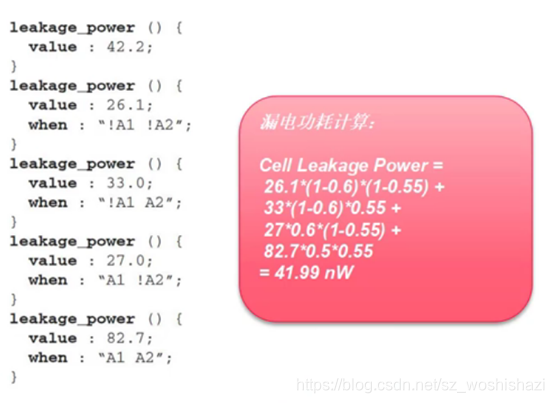

标准单元、宏单元的漏电功耗根据时序库(Timing library)文件中的“leakage power“查表与duty计算得出。

查找表内容包括: average leakage power 、 state dependent table

漏电功耗与input的duty有关,和output的toggle rate无关

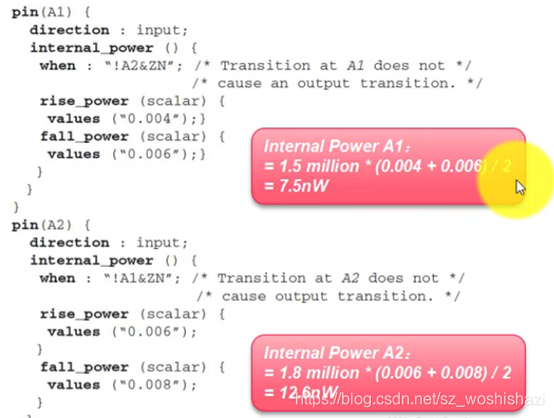

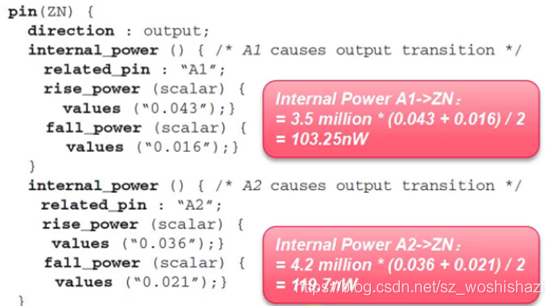

内部功耗计算

根据timing library中cell的internal_power查表与duty和toggle rate计算

查找表内容包括:

Input和output的internal_power

内部功耗与input信号slew和output的load强相关,与toggle rate有关

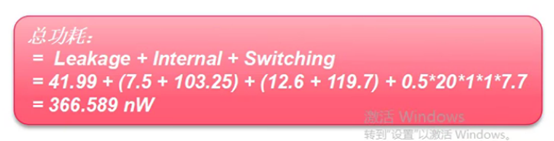

翻转功耗计算

P=0.5 * C *VDD^2 * f

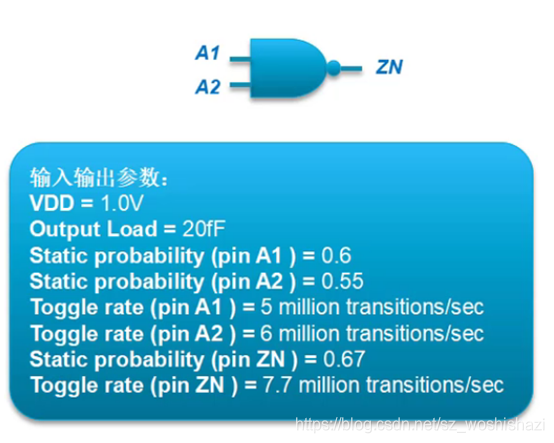

具体分析

下面拿二输入与非门举例如何计算总功耗

- 可以根据input的duty和查表得到的不同状态下的leakage_power来计算总漏电功耗,如下图。

- 根据查表得到的rise_power和fall_power可以和toggle rate计算得到input和output的internal_power,如下图

- 最后翻转功耗根据公式计算可得,最后的总功耗如下:

6116

6116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?