一、问题

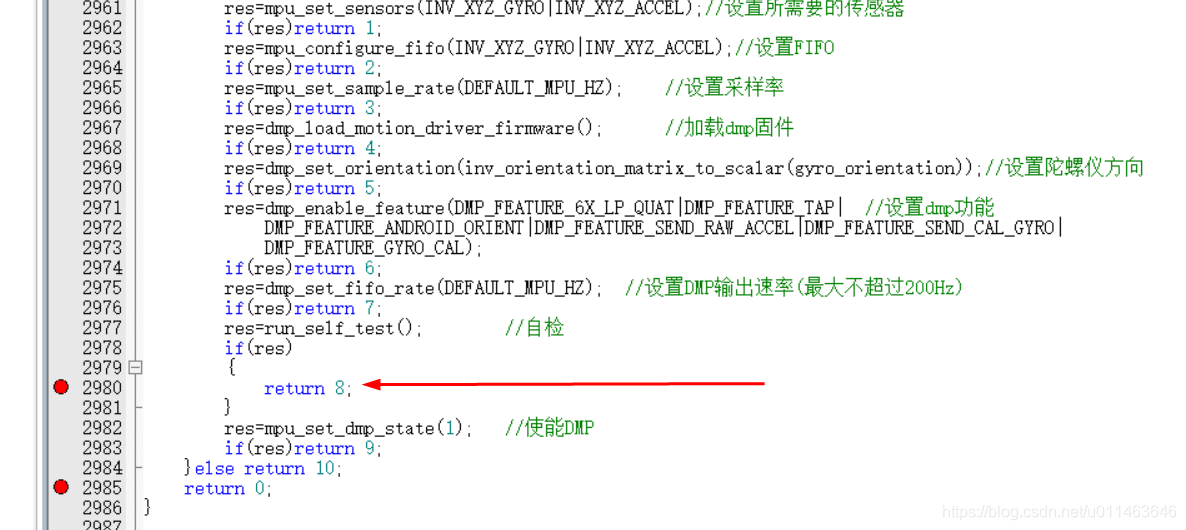

stm32c8t6移植MPU6050总是初始化失败,在自检测试通不过,返回8,网上的解决方法是将MPU6050放置水平,或者握紧杜邦线,但是怎么都不好使。

二、解决方法

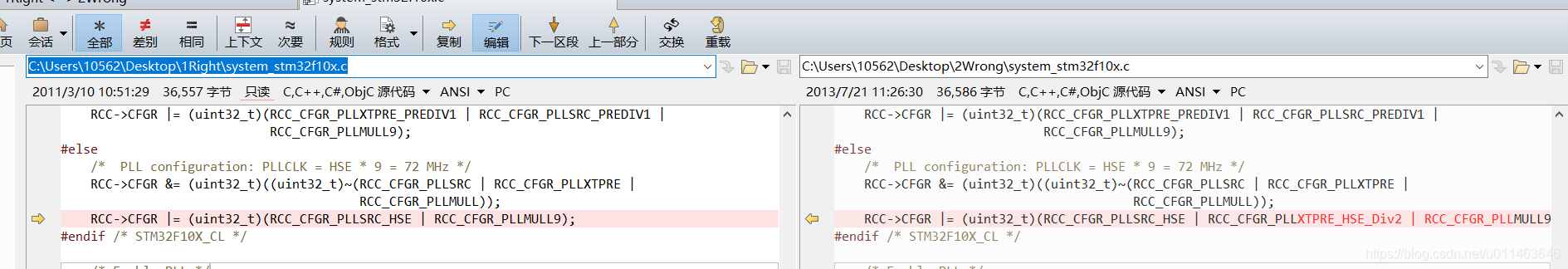

查找到一篇文章说是晶振时序的影响,后来下载一个工程对比分析发现system_stm32f10x.c在RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9)配置不一样,错误的工程中是 RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL9);

修改为RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9),自检通过。多了RCC_CFGR_PLLXTPRE_HSE_Div2 果然影响时钟。

这部分代码为外部晶振为8M时的情况:

/*PLL configuration:PLLCLK = HSE * 9 = 72MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

/*

修改后的代码对应的外部晶振为8/2=4M:

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_Div2 | RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

通过对比发现,修改后的代码多了一句话RCC_CFGR_PLLXTPRE_Div2。

RCC_CFGR:时钟配置寄存器,偏移地址为:0x04,复位值为:0x0000 0000。

PLLXTPRE:PREDIV1分频因子的低位。

Div2:二分频

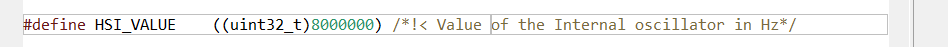

而stm32f10x.h中写的外部晶振HSE的值为8M,所以得到8/2=4M的时钟频率,明显导致IIC通讯异常。

工程下载STM32F103C8T6-MPU6050

https://download.csdn.net/download/u011463646/19421862

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?