Xilinx 公司提供了千兆以太网MAC控制器的可参数化LogiCORET™IP解决方案,通过这个IPCore可以实现FPGA与外部网络物理层芯片的互连。基于Xilinx FPGA 的以太网设计,大大降低了工程的设计复杂度,缩短了开发周期,加快了产品的面市速度。

Xilinx公司的千兆以太网解决方案按IP类型可以分为三态以太网软核、嵌入式三态以太网硬核、以太网AVB和Ethernet 1000BASE-X PCS/PMA等。基于40nm工艺技术制造而成的Vitex-6 FPGA,内部集成了4个三态以太网MAC硬核,采用三态以太网MAC硬核可以减少工程设计和验证工作量,并节省以太网接口控制的逻辑单元。与三态以太网软核相比,以太网MAC硬核特有的功能包括:集成的1000BASE-XPCS/PMA和SGMI物理接口:最高的接口速率可达2.5Gbps(16位1000BASE-X模式);提供的配置接口可以灵活地对RGMII/SGMII状态寄存器进行配置。

1 千兆以太网IP核简介

Xilinx公司在2001年推出了用于Virtex-1FPGA平台的干兆以太网媒体访问控制器(Gigabit Ethernet Media Access Controller,GEMAC)的IPCore,这也是业界针对FPGA开发并优化的第一个完整的千兆以太网解决方案,Virtex-1后续平台都支持GEMAC核。从Xilinx Virtex-5平台开始,FPGA内部集成了以太网MAC的硬核,可以轻松实现以太网MAC功能,不需要消耗FPGA内部的可编程资源。出于兼容性的考虑,支持10/100/1000Mbos的三态以太网MAC核逐断取代了GEMAC,现在的Xilinx设计环境中,以太网MAC(EMAC)作为一个库原语,特指三态以太网MAC(Tri-mode Ethernet MAC. TEMAC)

Xilinx公司的TEMAC核是可参数化内核,特别适用于交换机和路由器等网络设备使设计者能够实现大量集成式以太网设计,从低成本的10/100Mbps以太网顺利过渡到高性能的千兆以太网。TEMAC的设计符合IEEE802.3规范要求,具备3种工作模式:10Mbps、100Mbps和1000Mbps。此外,TEMAC还支持半/全观工操作。在10/100Mbps模式下,TEMAC采用MII接口:在1000Mbos模式下,TEMAC通过GMII/RGMII接口连接器件;TEMAC同时还支持SGMII/1000BASE-XPCS/PMA接口,综上所述,TEMAC能够提供全面、高度灵活,用于实现以太网链路层和物理层的解决方案。

Xilinx公司的Virtex-6系列FPGA对以太网MAC有着更好的支持,其内部整合了4个TEMAC模块(即硬核),其主要特性有:

■ 符合IEEE 802.3规范的要求:

■ 可配置的全双工模式(10/100/1000Mbps)和可配置的半双工模式(10/100 Mbps);

■ 支持MII、GMII、RGMII、SGMI和1000BASE-XPCS/PMA:

■ 通过管理数据的输入/输出接口(MDIO)管理对象的物理层;

■ 通过AX14-Lite接口进行核配置和状态监测:

■ 支持 VLAN帧:

■ 全双工操作模式下实现可配置的帧间间隔调整(IFG);

■ 通过MAC控制暂停帧实现可配置的对称或非对称的流量控制:

■ 支持任意长度的Jumbo帧。

2 TEMAC核的典型应用

TEMAC核的典型应用是实现以太网交换机、路由器或嵌入式处理器的以太网通信接口。如图1所示为基于TEMAC的以太网交换机或路由器的典型设计,TEMAC核的 PHY侧接口可以连接到外部集成的以太网PHY设备,支持10BASE-T、100BASE-T和1000BASE- T标准,也可以连接符合GMIIMII、RGMII或SGMII接口的PHY设备;TEMAC核的用户侧通过FIFO与用户进行互连,实现一个连接多接口的交换机或路由器。

图1 基于TEMAC核的以太网交换机/路由器设计

如图2所示为基于TEMAC核的嵌入式处理器以太网通信端口设计。MAC核的 PHY侧接口支持10BASE-T、100BASE-T和1000BASE-T标准和GMII/MII、RGMII或 SGMII接口设备。TEMAC核的用户侧接口可以通过DMA(Direct MemoryAccess)引擎连接到嵌入式处理器,处理器运行TCP/IP等协议实现以太网功能。

图2 基于TEMAC核的嵌入式处理器以太网通信端口设计

3 TEMAC核开发优势

基于Xilinx FPGA的TEMAC核为板卡级和芯片级互连提供了兼容千兆以太网技术的全套解决方案,TEMAC核的应用优势包括:

■ TEMAC核是可参数化内核,其物理接口速率可配置,用户可根据外围器件需求

灵活选择 10/100/1000Mbps自适应或特定的通信速率,特别适用于高密度千兆以太网通信和存储设备的开发;

■ TEMAC核与外围物理层器件无关,支持铜缆或光纤介质网络,可以灵活地实现以太网链路层和物理层功能;

■ 基于TEMAC的以太网解决方案充分利用IP核的“黑盒”优势,能够快捷高效地实现协议,从而降低了设计风险,缩短了开发周期;

■ Xilinx的可定制 TEMAC内核使得系统设计者能够实现大量集成化的以太网设计,从低成本的10/100Mbps以太网顺利升级为高性能的千兆以太网,从而降低设计成本;

■ 采用XilinxFPGA内嵌的TEMAC硬核可以有效地减少设计和验证工作,并节省逻辑资源。

4 TEMAC整体结构

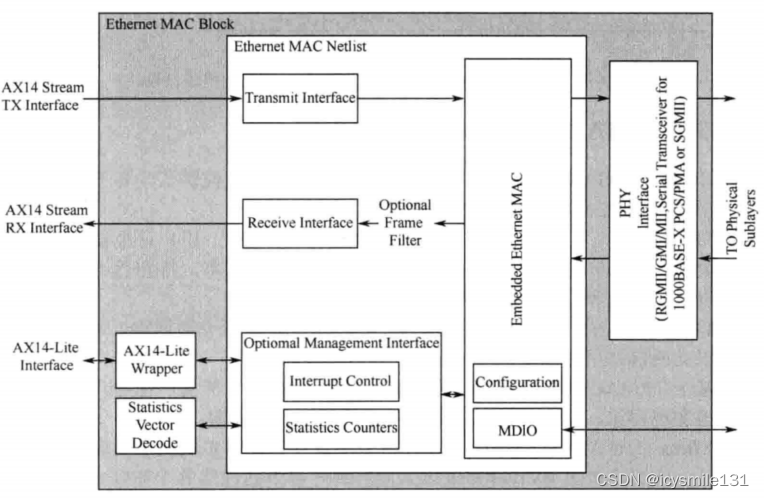

TEMAC硬核是一个支持多数据端口、多参数配置的复杂组件,其封装文件使用户只需要对特定应用所需端口的参数和接口进行定义便可完成TEMAC的设置,大大简化了时钟和物理I/O资源的使用。如图3所示为三态以太网 TEMAC核结构图,它包括嵌入式以太网MAC、AXI4-Lite封装接口模块、统计矢量译码模块(Statistics Vector Decode)和PHY物理接口模块4个部分。根据TEMAC接口方向和类型,可以将其接口信号分为3个部分,即用户接口信号(AXI4-Stream)、管理接口信号(AX14-Lite)和物理接口信号。

图3 三态以太网TEMAC核结构图

(1)嵌入式以太网MAC核

嵌入式以太网MAC核通过HDL示例设计形式提供,包括了使用MAC硬核时需要的基本模块。

(2)AXI4-Stream 接口

AX14-Stream接口使用户数据可以连接到MAC核内部的发送引擎和接收引擎。基于标准的AX14-Stream 协议,用户可以向MAC核发送数据或接收MAC核的数据。

(3)AXI4-Lite 封装

AXI4-Lite封装使用户可以通过AXI4-Lite接口连接到MAC核。用户通过AXI4-Lite接口对MAC核内部的寄存器进行配置,可以实现对MAC核控制/状态寄存器的访问及控制 MDIO主模式等功能。

(4)统计矢量译码

统计矢量译码模块用于解析MAC硬核在通信过程中产生的发送统计矢量和接收绩计矢量,并生成统计计数器的控制信号。

(5)PHY物理接口

PHY物理接口提供连接到RGMII.GMII.MII.SGMII找口或1000BASE-X PCS/PMA接口所需要的控制逻辑。当接入外部PHY设备时,使用由XilinxCORE Generator1™提供的并行接口标准(GMII/MII或RGMII)或串行标准(SGMII/或1000BASE-X PCS/PMA)。

5 嵌入式以太网MAC功能简介

如图4所示为嵌入式以太网MAC内部功能模块,主要包括发送引擎、接收引擎、流量控制,16或8位宽的用户接口,MII/GMI/RGMI接口、PCS/PMA子层、管理接口和MDIO裁决等。

图4 嵌入式以太网 MAC内部功能模块

(1)发送引擎

发送引擎从发送接口(TXInterface)接收数据并转化为所需要的格式(如GMII),对于待发送的数据,由发送引擎添加前导码(Preamble)和帧校验序列(FCS)。根据数据帧长度,在需要时也可以添加一定长度的填充字段(Pad)来满足以太网帧长度的传输要求。发送引擎为每一个数据包提供发送统计矢量(Transmit Statistics Vector),该引擎同时也支持发送流量控制模块产生的暂停控制帧。

(1)接收引擎

接收引擎从MII/GMII/RGMI接口接收数据,检查数据帧是否符合IEEE802.3协议标准,负责去除数据帧的填充区域,并对接收到的数据帧提供正确/错误指示信号。该引擎同时也为接收到的数据帧提供接收统计矢量(Receive Statistics Vector)。

(3)流量控制

流量控制根据IEEE802.3标准设计,通过暂停控制帧的收发实现:在以太网MAC全双工模式下配置流量控制功能,通过发送引擎发送的暂停控制帧附带可变的暂停值,接收引擎在接收后按照设定值进行处理。

(4)16或8位宽的用户接口

以太网 MAC的1000BASE-X物理接口具有超频特性,允许用户数据总线增加到16位。这种 16位模式只适用于物理接口为1000BASE-XPCS/PMA的情况,支持2Gbps(125MHz)或2.5Gbps(156.25MHz)。

(5)MII/GMII/RGMII接口

发送引擎和接收引擎将数据转换为GMII格式,而MII/GMI/RGMII接口模块实现了简化转换所需外部接口的必要的逻辑。

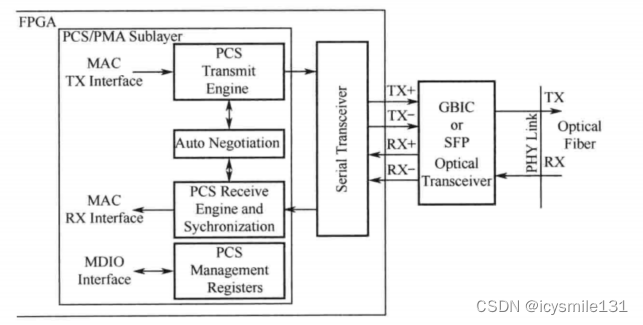

(6)PCS/PMA子层

当以太网MAC的物理接口配置为MI/GMII/RGMII时,相关信号将通过标准输入/输出接口连接到外部的物理接口上。当以太网MAC的物理接口配置为1000BASE-XPCS/ PMA或SGMII时,PCS/PMA子层模块的接口直接连接到串行收发器上。PCS/PMA子层模块将内部并行接口(MI/GMI/RGMI)转换为串行接口(1000BASE-X或SGMID),申行接口通过市行收发器(Serial Transceiver)与外部的光收发器进行通信,如图5所示。

图5 以太网的PCS/PMA子层

(7)管理接口

嵌入式以大网MAC管理楼口采用AXI4-Lite总线,主要配置MAC内部寄存器

(MACConfiguration)和MDIO接口(MDIO Interface),提供的功能包括对MAC控制/状态寄存器的访问和对MDIO主模式(MDIOMaster)的控制。

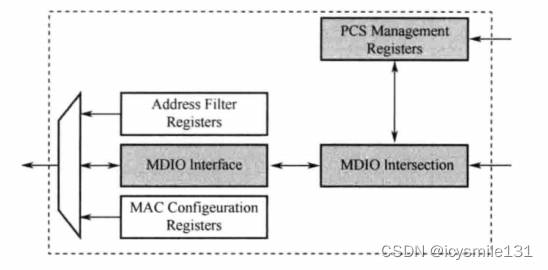

(8)MDIO裁决

MDIO接口根据MAC的配置可以工作在主模式或从模式下,如图6所示,当用户侧通过MDIO接口对PCS管理寄存器进行访问时,MDIO裁决模块裁定TEMAC核的 MDIO接口工作在主模式,PCS管理寄存器为从模式,从而实现MDIO接口和PCS管理寄存器的通信。

图6 MIDO楼口的主模式

当外部PHY访问PCS管理寄存器时,MDIO裁决模块裁定外部PHY工作在主模式, PCS管理寄存器为从模式,如图7所示,MDIO裁决模块确保了PCS管理寄存器在这两种模式下都可用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?