1 数模混仿的目的及思考框架

在数模芯片的研发过程中,作为研发项目中的数字部分设计,数模混仿是加大设计可靠性的重要过程,用于确保模拟到数字的信号的时序能正确的被采样,确保数字部分的输入正确,为芯片的功能正确保驾护航。

这里的数模混仿是指将数字的设计文件和模拟的设计文件进行联合仿真,仿真的顶层是整个芯片的顶层。(当然模拟工程师在设计时也会带着数字的设计文件进行仿真,但模拟工程师和数字工程师进行混仿是有区别的。)这里从数字工程师的角度出发,记录一下部分数模混仿的基础部分。

下面从纯数字设计仿真出发过渡到数模混仿上,这样理解框架就清晰明了了。

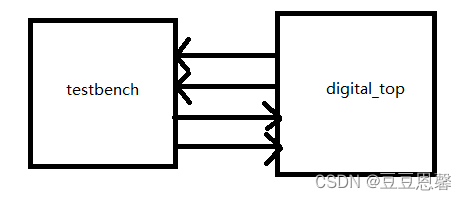

纯数字设计仿真:我们会建一个testbench的仿真文件和我们设计的数字部分digital_top进行仿真,digital_top中包含的全部是数字设计的.v文件,testbench是用于给设计文件灌激励的文件,如下图所示。

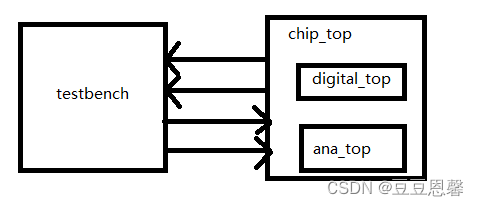

数模混仿:也是需要激励文件,即上图所说的testbench文件。相对于纯数字的仿真,混仿中的测试文件是建立在整个芯片顶层的,即它链接的引脚即为芯片pad。数模混仿中chip_top中的的设计文件就不再是只有数字设计文件,而是包括了数字设计文件和模拟设计文件,如下图所示。

chip_top还是一个.v文件。digital_top也全部是.v文件,testbench也是.v文件,而ana_top则换成了模拟spice网表(这个由模拟抽出的模拟网表,网表文件的内容见后面章节),但在chip_top中例化还是按照.v的方式例化的,chip_top这个整个芯片顶层文件的格式如下:

module chip_top (

//芯片端口的例化,和数字设计的输入输出端口一样的设置

);

digital_top digital_top_u (

.a(a),

.b(b),

.c(c),

……

);

ana_top ana_top_u(

.A(A),

.B(B),

.C(C),

……

);

endmodule

2 数模混仿工具

进行仿真肯定需要工具,工具可能还不止一种组合,这里给出一种组合:VCS+XA+VERDI(如下面的链接),其它的工具的使用可以在网上找找。

【验证基础】基于spice网表和xa工具的数模混仿_xa和costomsim-CSDN博客

有人做过数模混仿吗? - IC验证讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

对于数字设计人员来说,可能需要寻找XA的使用手册和混合信号设置的使用手册,后面找到后可以把链接贴上。

3 数模混仿的输入文件

(1)数字设计.v文件,对应上图中digital_top。

(2)模拟网表即spice网表,对应上图中的ana_top。

网表文件主要包含的就是以.subckt 开头,.ends结束的结构块描述,一个结构块描述的是一个器件或者一个功能模块,就像数字电路中的module和endmodule的功能一样。在这个网表文件中有很多这样的结构块,一个结构块可以出现在另一个结构块中,犹如数字电路中例化功能模块。在这个网表文件中直接找到模拟的顶层,了解模拟顶层中例化的各个模块的主要功能,这样方便后面加速仿真。要确保模拟顶层中每个例化模块能在这个网表文件中找到,不然仿真会提示某个文件、器件之类的找不到。

.subckt ……

xi7 …… INV2_V25

xi9 …… POR

……

Vavdd avdd 0 DC=2.5v

Vavss avss 0 DC=0

Vdvdd dvdd 0 DC=2.5v

Vdvss dvss 0 DC=0

.ends

注1:“xi7 ……INV2_V25”这里是spice网表中例化了一个INV2_V25的模块,INV2_V25这个module的定义可以在模拟spice网表中找到。中间“……”这部分是例化时的端口例化,这个是按位置映射的。

注2:“Vavdd avdd 0 DC=2.5v”这部分是直接在网表中给芯片设置电压,可以自己设置,这里设置了在testbench中顶层电源接口可以不用接。关于不同电压的设置要求有不同的设置方法,以后再补充。

(3)芯片顶层.v文件,对应上面讲到的chip_top

(4)仿真文件对应上面的testbench

(5)mix_control.int,这个文件用于将ana_top替换成(2)中说的模拟网表,也会在这里定义模拟到数字的接口电平定义(即a2d),还会定义数字到模拟的接口对应的电压(即d2a)。

mix_control.int

use_spice -cell ANALOG_TOP

choose xa -n ../../analog_netlist/spice.ckt ../mix_signal.cfg -o -xa/xa123;

port_dir -cell ANALOG_TOP(inout a,b,c,d,e,f);

a2d loth=0.8 hith=2 cell=ANALOG_TOP port=a;

a2d loth=3.3 hith=6 cell=ANALOG_TOP port=b;

d2a hiv=3.3 lov=0 cell=ANALOGT_TOP port=c;

bus_format <%d>

可以参考如下网址第2章:混仿基本特征_数模混仿 d2a a2d 配置-CSDN博客

在使用脚本文件进行仿真时,需要把这个文件读入,否则在这个文件中设置的无效。

(6)mix_signal.cfg ,这个文件里会定义需要观察的模拟信号,以及有的仿真设置mix_signal.cfg

set_waveform_option -format fsdb -flush 100ns -size 2000

probe_waveform_voltage -v testbench_top.dut_u.I1.*

set_logic_threshold -loth 0.8 -hith 2 -node *

set_sim_level 5

set_multi_core -cpu 4

可以参考下面的网址【验证基础】基于spice网表和xa工具的数模混仿_xa和costomsim-CSDN博客

4 相关链接

数模混合仿真实例(数字verilog作为顶层)VCS+Xa; 跑XA自带的demo存在的问题_vcs xa 波形实时更新-CSDN博客

XA VCS混仿编译问题 - IC验证讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

xa混合信号仿真guide - 第5页 - Analog/RF IC 资料共享 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

自己手动整理了一份在Cadence图形界面下进行Xa+VCS混合仿真的文档 - Analog/RF IC 资料共享 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

Finesim 2014.09 Mixed-Signal Simulation User Guide - Analog/RF IC 资料共享 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

笔记先记到这里,后续会继续更新,如有错误欢迎指出,如有补充欢迎添加。

本文详细介绍了数模混仿在芯片开发中的作用,涉及数字设计文件与模拟设计文件的联合仿真,使用的工具组合(如VCS+XA+VERDI),以及仿真所需的输入文件,如数字V文件、模拟SPICE网表和配置文件。

本文详细介绍了数模混仿在芯片开发中的作用,涉及数字设计文件与模拟设计文件的联合仿真,使用的工具组合(如VCS+XA+VERDI),以及仿真所需的输入文件,如数字V文件、模拟SPICE网表和配置文件。

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?