一.关于SDRAM

1.SDRAM Synchronous Dynamic Random Access Memory,同步动态随机存储器。同步是指它的工作(包括指令或数据的传输)需要同步时钟。动态指要保持数据的稳定,需要不断的刷新操作。随机是指数据的存取不是线性存取,而是按照地址进行读写。

2.SDRAM包括 SDR SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM四代。SDR SDRAM是单沿采样,第二、三、四代是双沿采样,工作频率更快,所以使用可以降低干扰的差分信号作为时钟信号。

SDR 不等于 SDRAM

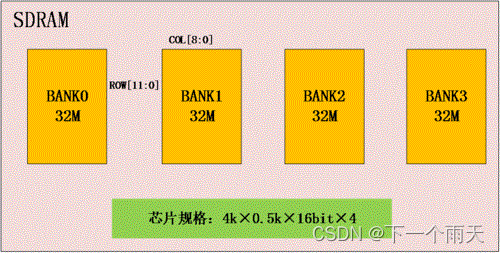

3.SDRAM芯片规格,拿笔者使用的SDRAM举例,笔者使用的是HY57V281620A 4Banks×2M×16bits Synchronous DRAM。

① SDRAM容量

SDRAM芯片内部包含4个BANK,每个BANK的大小为32M,所以SDRAM的容量32×4=128M

② 32M含义

每一个BANK实际上是由ROW×COL个16bit的数据格(比喻)组成,根据手册,ROW的位宽分别为12位,即4k;COL的位宽为9位,即0.5k。所以格子数=4k×0.5K。每个BANK容量:4k×0.5k×16bit=32M。

③ ROW的含义

这里面的ROW对应手册里面的A[11:0],MRS(模式寄存器配置时),A代表模式寄存器指令;在读写模式时,A代表地址(A[11:0]:行地址;A[8:0]:列地址)。

4.突发长度 SDRAM在进行读写时的一种模式叫做突发模式。在这种模式下,以写操作为例,突发长度为3,给出写命令和写地址后,连续写入3个数据,不必再给出后两个数据的地址,它会连续的写入。突发长度包括1、2、4、8。

5.潜伏期 在读取数据时,数据的读出时间会比读命令的时间晚相应的潜伏期的长度。潜伏期越长,时序就越得到提升。

举例:以Latency Mode=3 Burst Length=4 Burst Type=Sequential的模式下取读数据

在给出读指令跟地址时,如果Latency=3,数据以上面的形式延后三拍给出,Latency=2,数据则延后两拍给出。

6.刷新

为什么要刷新

SDRAM的基本结构是电容,单位是F(法拉),C=Q/U。Q-电荷量;U-平行板电势差。容量C跟Q有关。电容容易漏电,所以为保证数据的稳定,要定期对其充电,即SDRAM的刷新。

刷新频率的计算

对手册描述4096 refresh cycles / 64ms的解读:即每64ms对一个bank刷新一次。一个bank有2^12=4096 row。每一个刷新操作的对象是一个row,1 refresh cycles=15.625us。值得一提的是计算出的15.625us是平均刷新时间,而这4096次刷新只要在64ms内完成,刷新间隔可以不必是均匀的。这里我们取1 refresh cycles = 12us。

对SDRAM的介绍就到这里,下面我们来看看SDRAM是如何与其他模块对接的。

二.SDRAM模块描述

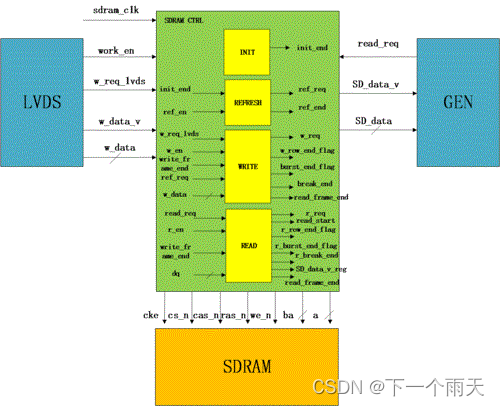

由于篇幅有限,只给出SDRAM的整体框图,与各个子模块的状态机。整体框图–表示SDRAM控制模块与外部模块与芯片(SDRAM)的关系;子模块状态机–表示各个操作的过程与跳转条件。

(一)整体框图

FPGA通过SDRAM控制器来控制SDRAM芯片,SDRAM_CTRL对SDRAM芯片的操作包括INIT(初始化)、WRITE(写操作)、READ(读操作)。对SDRAM_CTRL的整体模块描述如下:

1.LVDS模块通过信号work_en、w_req_lvds,在数据有效(w_data_v==1)时,将数据w_data缓存入sdram中。

2.SDRAM_CTRL的内部变量

3.SDRAM_CTRL通过cke、cs_n、cas_n、ras_n、we_n、ba、a信号跟SDRAM芯片绑定,完成INIT、REFRESH、WRITE、READ等操作。

4.GEN模块来取数据是会发送read_req信号给SDRAM_CTRL模块,SDRAM_CTRL模块将读出的数据SD_data,在SD_data_v(数据有效)有效时写入GEN FIFO中。

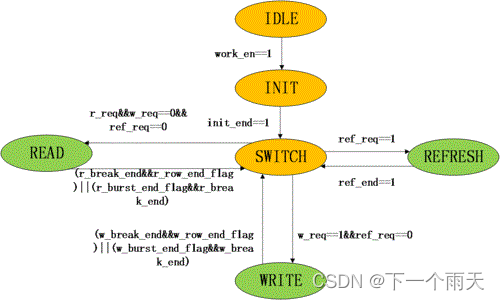

(二)主状态机

- 在IDLE状态下

检测到work_en==1,进入INIT状态。

2.在INIT状态下

检测到init_end==1,进入SWITCH状态。

3.在SWITCH状态下

? 检测到ref_req==1,进入REFRESH状态。

? 检测到ref_req0,w_req1,进入WRITE状态。

? 检测到ref_req0,w_req0,r_req==1,进入WRITE状态。

4.在REFRESH状态下

刷新结束后,发送ref_end信号,返回switch。

5.在WRITE状态下

写一行结束或者写突发被刷新打断,返回SWITCH状态。

? 写一行结束:发送w_row_end_flag和w_break_end

? 突发写被打断:发送w_burst_end_flag和w_break_end

6.在READ状态下

读一行结束或者读突发被刷新打断,返回SWITCH状态。

? 读一行结束:发送r_row_end_flag和r_break_end

? 突发读被打断:发送r_burst_end_flag和r_break_end

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?