原标题:超大规模集成电路中的非理想性

本文将讨论VLSI(超大规模集成电路)电路以及影响 MOS晶体管的非理想因素的来源。

自20世纪40年代末至50年代初发明晶体管以来,它一直是电子器件中最主要的元件,它使现代技术得到了极大的提高。摩尔定律和Dennard缩放已经描述了改进现代IC设计中的晶体管的功能尺寸和性能的需要;也就是说,每24个月就需要将某个芯片中的晶体管数量增加一倍。

由于这种改进,早期的晶体管电路(几毫米)与现代的晶体管电路(跨度只有几纳米)相比,在性能、工作点和内在特性上都有明显的差异。

在这篇文章中,我们将讨论理想的MOS晶体管分析模型和由于MOS晶体管的功能尺寸和设计的不断改进而产生的非理想性。另外,我们将讨论在实际实现之前,介绍了在MOS晶体管中引入非理想(SNI)的设计方法,以正确模拟仿真中的VLSI电路。

背景资料:源极和漏极

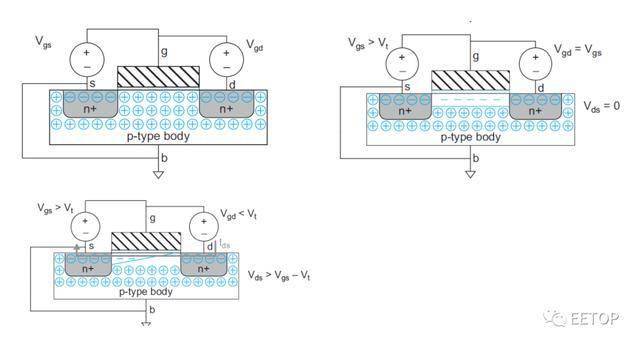

考虑图1中的基本晶体管图。当没有电压施加到栅极(g)上时,称该晶体管处于OFF状态。

图1.基本晶体管工作模式

如果施加较小的栅极电压(Vgs Vt),则会在漏极(d)和源极(s)之间创建一个通道,从而使漏极-源极电流(Ids)流动。

在导通状态下,漏极电流(Ids)与漏极电压(Vds)线性增加,直到(Vds = Vgs = Vdsat),之后漏极电流保持恒定。如果漏极电压进一步增加到该值(Vds > Vdsa

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2817

2817

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?