模拟CMOS

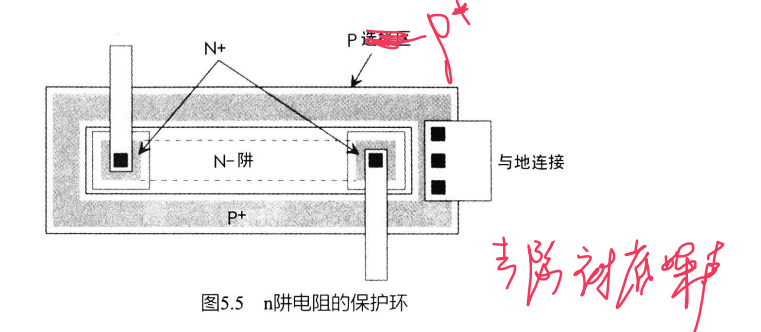

- 衬底噪声:由于相邻的电阻互相注入电流而产生的衬底噪声。解决方法:在两个电阻之间加入一个P+注入区(作为P衬底晶圆的衬底接触)。P+注入区保护电路免受载流子的影响,由于注入区是一个环形,所以成为保护环。

-

共质心版图

共质心(共同的中心)版图有助于改善两电阻之间的匹配性能(代价是两元件之间具有不均匀的寄生特性),另外,共质心也能改善MOS和电容的匹配性能。

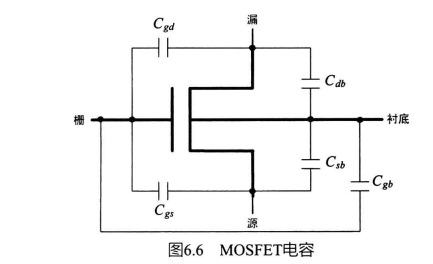

3.MOS电容

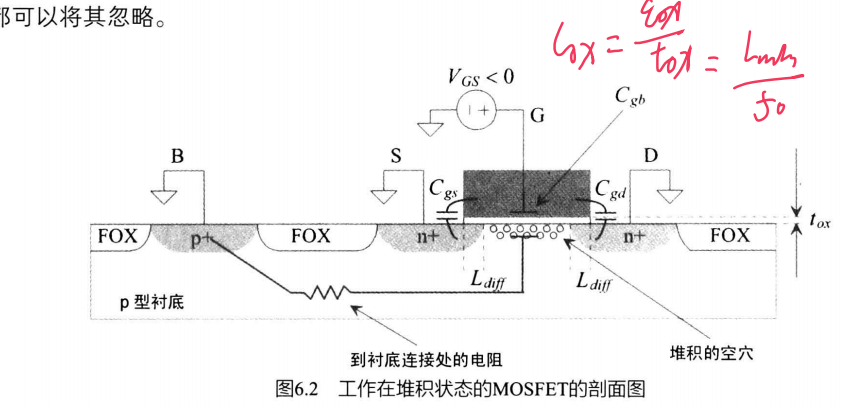

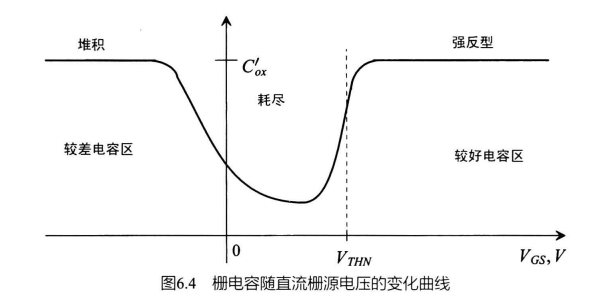

- 堆积 (VGS<<Vth)

当VGS<0,来自衬底移动的空穴被吸引(堆积)到栅氧层的下方。当MOS管处于堆积区时,栅极到地的电容Cgb的主体部分经过了衬底的大寄生电阻。为了让MOS工作在吃工作区,需要在栅氧化层周围有足够的衬底连接(以减少寄生衬底电阻)。从栅极到gnd之间的电容之和为:

C G S + C G B + C G D = C o x C_{GS}+C_{GB}+C_{GD}=C_{ox} CGS+CGB+CGD=Cox

-

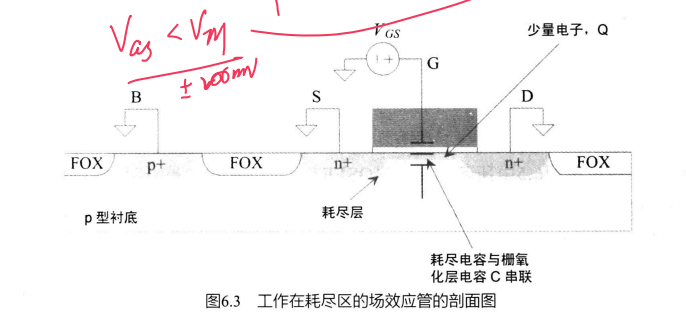

耗尽 (VGS<VTH)

当VGS<Vth(大约小于100mV),此时VGS不够负,不能吸引大量的空穴到栅氧层的下方,同时也不能足够正,无法吸引大量的电子。此时的栅极下方的硅表面被称作近耗尽(自由电子和空穴被耗尽),观察下图,当

VGS从某个负电压开始上升,栅极下方的空穴将会被替代,只留下不能移动的受主离子提供一个负电荷。随着VGS的增加,栅氧层下方感应的n沟道和三级之间将存在一个电容。同时在耗尽沟道和衬底之间还会存在一个耗尽电容。栅极和源极/漏极的电容只是覆盖电容,而栅极和衬底之间的电容是由氧化层电容和耗尽层电容串联而成的。下图中的耗尽电容式由n沟道和衬底之间形成的。由于氧化层下方的表面不是重n+区,所以工作在这个区的MOS被称为弱反型区或者亚阈值区

-

强反型区 (VGS>>vth)

当VGS>>Vthn时,大量的电子被吸引到栅极下方,此时栅氧化层表面称为反型,即不再是P型了。当需要一个电容时,可以最好时MOS工作在强反型区,被吸引之栅氧化层下方的电子将漏极和源极短接在一起形成电容的低电阻底板(常将源漏相连来讲MOS做电容)。

耗尽型器件(负的阈值电压,阈值电压等于0时,器件导通)

增强型器件(正的阈值电压,VGS=0时,器件截止)

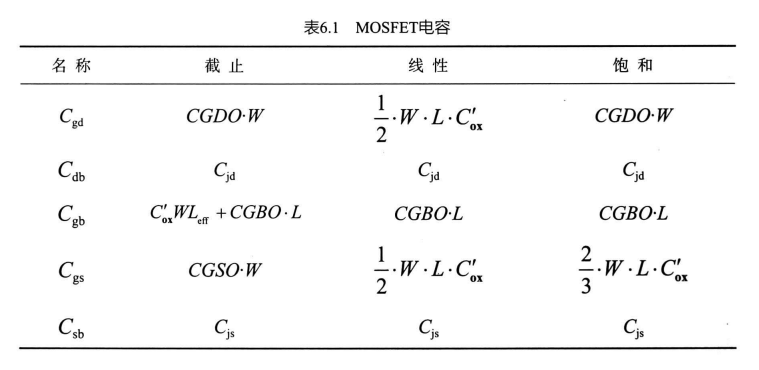

4.MOSFET的I/V特性

-

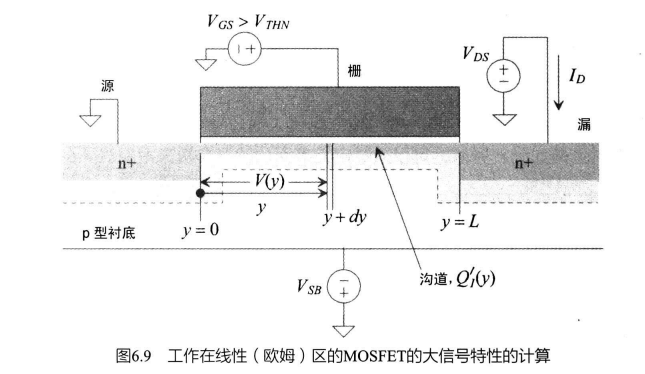

线性区(Vgs>Vth,Vds<Vgs-Vth)

由于Vgs>Vth,所以在栅氧化层下的表面会反型,因为Vds>0,所以有漂流电流从漏端流向源端。

I D = β × [ ( V G S − V T H ) 2 V D S − V D S 2 2 ] , β = k μ C o x W / L I_D=β \times [(V_{GS}-V_{TH})^2V_{DS}-\frac{V_{DS}^2}{2}] , β=kμC_{ox}W/L ID=β×[(VGS−VTH)2VDS−2VDS2],β=kμCoxW/L

-

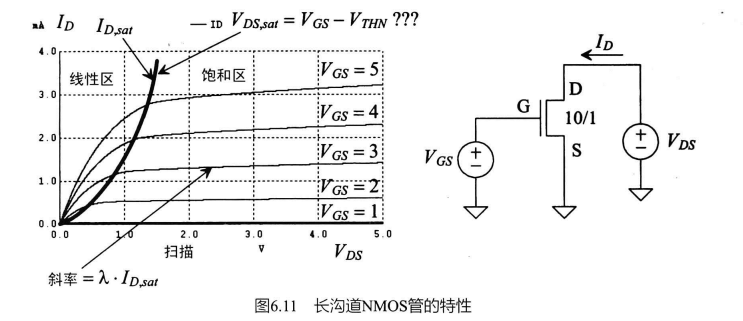

饱和区(Vgs>Vth,Vds>Vgs-Vth)

当Vds=Vgs-Vth时,栅电极下方(漏极与沟道的汇合处)沟道中的反型电荷为零,这个漏端和源端之间的电压被称为Vds,sat=(Vgs-Vth),它表明沟道在漏端和沟道交界处被夹断。增加Vds并超过Vds,sat,会将固定电荷吸引至漏端,从而使得沟道中紧临漏端的电荷被耗尽。继续增加并不会使漏端电流继续增加(由于沟道长度调制效应会使漏端电流随着漏端电压增加而增加)

I D = 1 2 β ( V G S − V T H ) 2 ( 1 + λ V D S ) , λ = 1 L d X d V D S I_D=\frac {1}{2} β(V_{GS}-V_{TH})^2(1+λV_{DS}) ,λ=\frac {1}{L}\frac {dX}{dV_{DS}} ID=21β(VGS−VTH)2(1+λVDS),λ=L1dVDSdX

迁移率会随着Vds变化而变化,

- 饱和区中的Cgs计算:

C g s = 2 W L C o x 3 , C o x = E o x t o x C_{gs}=\frac {2WLC_{ox}}{3} ,C_{ox}=\frac {E_{ox}}{t_{ox}} Cgs

- 饱和区中的Cgs计算:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?