数字IC后端实现专家都具备哪些技能?(附后端面试宝典)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

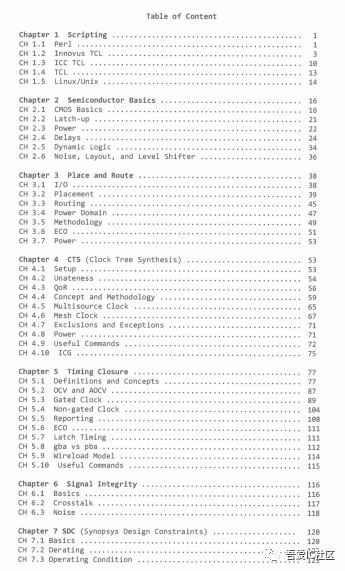

又到周末了,下午上海开始下起了毛毛细雨,这样的天气小编都有点惰性了。但是自己定的周更目标仍然还是要坚持下去的,所以下午又来到星巴克码字来了。码字之前想起分享一份数字 IC 后端面试宝典给大家,这份宝典是一本书,约 230 页,亚马逊上好像是卖三百多人民币吧,特此分享给需要的朋友。有需要的朋友可以前往小编知识星球查看下载。

另外 Synopsys 的各大 workshop 还在扫描中,预计五一过后可以不断分享出来。为了扫描这些书籍,小编都瘦了几斤了,没有功劳也一定有苦劳。

懂设计本身

对于数字后端工程师来说,一般是不会去写代码,但必须要懂设计。比如你作为一个 chip 的 top owner,做后端实现时你必须根据设计的 data flow,各个模块之间如何交互,各个时钟之间的关系等信息来规划 floorplan,做好标准单元的摆放,时钟树综合等工作。

如果你对设计本身不清楚,那么你就是硬着头皮做后端,你一定会做得很累,很痛苦。经常碰到很多工程师抱怨 timing 太难收敛了,绕线总是绕不开等现象。主要原因还是不懂设计,比如前端设计的时钟结构不合理,你仍然硬着头皮做,最后发现 hold violation 就是不好修,插入太多的 holdbuffer,绕线又绕不通,陷入死循环。又比如 placement 后各个逻辑模块位置分布跟 data flow 不 match,导致 timing 怎么都做不上去或者出现**setup 和 hold 打架(互卡)**的情况。

数字 IC 设计实现之 hold violation 修复大全

懂逻辑综合

熟悉逻辑综合各个阶段(逻辑优化,DFT 等)工具都做了哪些工作,每个工作对数字后端实现可能造成的影响。

需要与前端工程师沟通,了解设计架构,时钟电路结构,各个时钟间的同步异步关系,芯片的应用场景等方面。

根据设计需求编写设计约束文件 SDC 并请前端设计工程师 review(这个过程需要不断与前端设计工程师不断沟通,特别是第一次做某个新的 design)。

制定扫描链插入方法,分配 scan chain 条数,确保测试覆盖率,产生 scan test pattern。

根据数字后端实现情况决定是否需要做 scan chain reordering。熟悉 scan chain reordering 的工作机理,对 hold 的影响。

Scan chain reordering 怎么用你知道吗?

熟练掌握 DCT/DCG 的逻辑综合 flow,以及哪些设计需要做 DCT/DCG。甚至如果你对设计和工具的行为有足够的熟悉,完全可以用 DC+DCT 的混合模式来实现设计需求。

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

理解综合工具的行为,高效率 fine tune 综合阶段和布局布线阶段之间的 timing 一致性。掌握一系列可以改善 timingcorrelation 的方法,比如 set_max_cell_density 等变量的设置,以及如何反馈 PR 阶段的 clock latency 给综合工具等等。

精通布局布线(Place&Route)

- 工艺选择

对于一个新工艺可以快速评估当前项目需要选用某个工艺节点的哪个 metal stack,是 1P7M 还是 1P8M? 是用 9Track 还是 12Track? 这个选择涉及到数字后端 powerplan 规划,IR drop,布线阶段可用的绕线资源,封装形式,乃至整个芯片的成本。

教你彻底搞懂 ARM Cortex-A75 CPU 的数字后端实现报告

- IP 相关

需要根据设计需求和后端 floorplan,与 IP vendor 沟通定制 IP 的形状和 orientation。这里简单提一下,很多工程师经常犯一个错误就是 IP 的 poly orientation 问题。比如 vendor 提供给你的是 EW 方向,而你做 floorplan 时确把它当做 FN 来使用(这点是致命的)。

能够从 IP Vendor 提供的文件中快速提取 check list。比如 IP 和 core logic 之间应该预留多少 spacing,IP 中某些关键信号对电阻的特殊要求等等。

能够给 IP 规划一个 robust 的 powerplan。很多工程师还只是停留在将 IP 的 power ground pin 连起来,而忽视供电 robust 特性。小编反正每次都是将 power net 能画粗点就尽量画粗点,能形成 power mesh 的就尽量画一个电阻最小的 power 网络。总之 powerplan 一定要经得起 review。

数字 IC 后端设计实现 floorplan 及 powerplan 规划

- 模块 partition

chip 或者 block 形状选取(矩形或者方形抑或多边形,与 design 相关,关乎 routing 资源)。深知各个 block 的难易程度,各个模块适合用什么类型的形状等。

能够根据后端实现情况,向前端提出那部分逻辑可能需要单独做 hardening。因为前端对于模块的切分可能仅仅考虑逻辑功能方面,而后端则可以根据实现的复杂程度和难易程度,反馈可能需要单独做 PD 的模块。

根据 design 的 data flow,合理摆放各个 partition 模块的位置以及出 pin 位置。为了节省面积,经常还需要做信号的 feedthrough,实现模块之间无缝对接(channeless)。对于低功耗设计,可能还需要提前规划若干个孤岛,用来走某些特殊的 signal 或者 clock。

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

数字 IC 后端设计实现 floorplan 及 powerplan 规划

- chip area 估算

为 IO 添加 core vdd &core vss 以及 IO vdd& IO vss。前者涉及芯片功耗的估算,后者设计 SSO 的计算。同时还需要考虑 ESD 和 EM。

IO 添加完成后,根据各个模块的面积,IP 的面积,IO 的面积就可以大致估算是 chip 的面积。这里需要指出的是,如果 chip 是 IO limited,则可以反馈信息给 PM,询问是否可以通过 IO mux 来实现 IO 的复用,从而减少 IO 的数量。如果 chip 是 core limited,则需要重点将各个子模块的面积最到最小。

- Timing 和 congestion 优化

Timing 优化贯穿着整个数字 IC 设计全过程。一个对设计比较了解的工程师,一定可以做好 timing 优化,它可以站在设计的角度来规划模块的分布。PR 阶段用于优化 timing 的一些方法如下:

使用 SPG flow

使用 Multi-Vt 作为 target_library 优化

CCD flow

create_voltage_domain, create_bounds,keepout setting,group_path 等

对于设计实现中碰到的 congestion 问题都能快速找到 root cause,从根源上解决。

- Power 优化

低功耗设计 flow 和方法论

掌握优化 leakage 和动态功耗的方法

- 时钟树优化

这个阶段需要后端工程师能够自己来分析时钟树结构,并根据 design 的 spec 来编写一个约束文件,引导工具 如何长时钟树。很多 SOC 中,时钟都有几百个。由于 PLL 的个数有限,因此很多设计都有时钟选择和切换电路。因此,针对复杂的时钟结构,工具可能很难做到符合我们预期的时钟树(clock skew 和 clock latency)。

很多数字后端工程师经常担心自己的工作会被工具所替代,其实大可不必。有这方面担忧的朋友可能做的是假后端,可能仅仅停留在 run flow 这个层次。小编从来没碰到过工具能把复杂模块的 cts 自动做好的,人为干预的东西真的是不要太多了。难道你们不觉得工具真的很笨吗?

这步非常关键且非常重要,也是衡量一个数字后端工程师能力的重要指标。主要工作如下:

clock tree building constraint 的编写

长时钟树需要设置的 timing drc 等

时钟树用于长 tree 的 buffer 或者 inverter 种类选择

时钟树的 ECO

设定 clock net 的 non-default rule

如何做 shielding,对哪些 net 可以做 shielding,影响是什么

- 绕线和串扰

熟练掌握 fix short 的方法

理解 SI 产生的原理和避免 SI 的方法

理解 SI 和 noise 的区别(见知识星球上解析)

- 精通 Function ECO

不论是 pre-mask 或者是 post-mask,都可以高效完成设计所需的 FunctionECO。这里涉及 ECO 所能动用的 layer,是通过用ECO cell 还是 spare cell来实现,ECO 后的 timing fixing,LVL 比较,利用 ECO CELL 和 Space CELL 做 function eco 各自的优缺点等。

- IR Drop 分析和优化

精通 IR Drop 分析和优化包括静态和动态 IR Drop 分析。对一个 chip 分析 IR drop 后还需要对其进行优化。对于基于 Redhawk 的 IR Drop 分析 flow 之前已经在知识星球上分享过。IR drop 优化的方法也分享过无数次了。

数字 IC 设计后端实现前期预防 IR Drop 的方法汇总

- 理解工具

工具一定不是万能的,bug 也是无处不在,但是如果你能将工具的长处用的淋漓尽致,那么你一定会喜欢上它的。一方面资深的后端工程师懂得工具的局限性,工作时尽量避免工具进入此工作模式,不掉入 “陷阱” 中。另外一方面对工具的行为有比较透彻的理解,可以利用工具为我们所用,可以利用它的特性来 guide 工具实现我们的需求。

精通时序分析和 timing signoff

时序分析和 timing sigoff 这步,很多数字后端工程师也都做了。但是你是否是拿着现有的 flow 跑下 primetime,然后就开始你的 leakage optimization,hold violation fixing 和 timing drc 的 fixing? 这个能力是每个数字后端工程师都必须具备的,但是仍然远远不够。你需要搞清楚以下几点:

signoff 的标准,如何定?(特别是一个新的工艺)

如何优化 leakage 优化的 flow,使得 leakage 最小化?

如何少插 hold buffer?

遇到 hold buffer 修不进去,如何解决?

精通物理验证

这步属于 physical signoff 阶段。主要为 DRC,LVS,ERC,ESD,Latch up 等方面的检查和修正。在先进工艺节点中,physical vertification 显得更为重要。

精通脚本语言

脚本能力强,至少掌握一种及以上脚本语言(TCL,perl,python 等)。至于哪种语言不重要,关键是要学会一门语言并且能够熟练运用。

涉面广且有专长

面广就比如本篇所列到甚至更多方面你都比较熟练。专长是指你至少要在某个领域有深入的研究而且做的要比别人好,比如擅长做高频率的模块实现,或者擅长 physical 方面(powerplan,DRC ,LVS 等),抑或擅长写脚本,能够写一个 timing engine 出来。

流程自动化

将整个实现 flow(从综合到物理验证)调好后,一旦 rtl ready 后可以自动一键实现从 RTL 到物理验证(较少的 DRC)。

好了,今天关于数字 IC 后端专家基本技能的分享就到这里。今天小编罗列的数字 IC 后端专家具备的这些技能,大概有 90% 的内容都是之前分享过的(公众号和知识星球上)。因此,如果小编公众号上和知识星球上的分享你都认真看过,搞懂了,那么你离数字 IC 后端专家还远吗?

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

定期将项目中碰到的问题以案例的形式做技术分享

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有176位星球成员,感谢这 176 位童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。(星友人数超过200 人后星球的门票即将调整到228 元 / 年,有需求的朋友趁早上车,**目前价格是 208 元 / 年,折算每天需要六毛钱 **)

很久没放出公众号链接了,很多芯朋友表示找不到关注入口。赶紧扫码或者长按图片关注起来吧!(小编微信:ic-backend2018)如果需要进数字 IC 后端技术交流群,可以添加小编微信,邀请入群。

1356

1356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?