数字后端面试问答No.22-24(每日三问)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

最近正是各大公司校园招聘抢人的关键时期,提取祝各位同学找到一份好工作。听说今年应届生最高依然可以开到月薪超 2 万,你是否拖后腿了?另外,吾爱 IC 社区小编建议大家把本公众号中所有文章都认真看一遍,对你肯定有所帮助,说不定还能碰到原题哦。

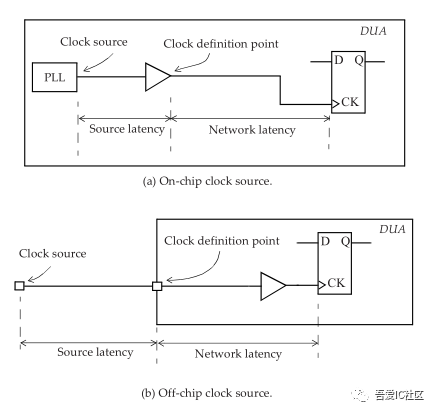

1.What is a clock latency? What components are there in it ?

A clock latency is the time for a clock to be propagated from a clock source to its sinks. A latency consists of source latency and network latency,and the source latency may or may not on chip depends on design requirements as shown in the following figure:

2.If a buffer insertion is needed to fix a setup violation,and the distance between launch FF and capture FF is about 200um,where is the best location to put buffers?

秒杀数字后端实现中 clock gating 使能端 setup violation 问题

Tips: It depends on setup and hold time slack!

-

Buffers are inserted for fixing fanout voilations and hence they reduce setup voilation; otherwise we try to fix setup voilation with the sizing of cells; now just assume that you must insert buffer !

-

Near to capture path.

Because there may be other paths passing through or originating from the flop nearer to lauch flop. Hence buffer insertion may affect other paths also. It may improve all those paths or degarde.

If all those paths have voilation then you may insert buffer nearer to launch flop provided it improves slack.

- Others

3.What is the most challenging task you handled? What is the most challenging job in P&R flow?

-

It may be power planning because you found more IR drop

-

It may be low power target because you had more dynamic and leakage power

-

It may be macro placement because it had more connection with standard cells or macros

-

It may be CTS because you needed to handle multiple clocks and clock domain crossings

-

It may be timing because sizing cells in ECO flow is not meeting timing

-

It may be library preparation because you found some inconsistancy in libraries.

-

It may be DRC because you faced thousands of voilations

**** 小编知识星球简介:****

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程(已经发布)

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现(已经发布)

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程(准备中)

-

时钟树结构分析(规划中)

-

低功耗设计实现(规划中)

-

定期在星球布置作业题(星球已经支持布置作业功能)

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有五十四星球成员,感谢这五十四位童鞋的支持!欢迎各位铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。 (星球的门槛将会越来越高,有需求的朋友趁早上车)****

相关文章推荐

低功耗设计实现中 secondary power pin 的连接方法汇总

项目后期踩到这些坑,原来可以这么简单处理!(数字后端实现救火篇)

想要彻底掌握 placement 各种技巧,这个一定可以如你所愿!

教你轻松玩转天线效应 (Process Antenna Effect)

深度解析 Create_clock 与 Create_generated_clock 的区别

clock jitter 是否对 hold time 有影响?(文末有福利)

为什么时钟树上要用 clock inverter(min pulse width check)

PBA(Path Base Analysis)想说爱你不容易(静态时序分析基础篇)

【惊呆了!】你居然还在用 flatten 方式进行 timing signoff

合理的时钟结构能够加速 Timing 收敛(时钟树综合中级篇)

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

秒杀数字后端实现中 clock gating 使能端 setup violation 问题

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

Scan chain reordering 怎么用你知道吗?

数字后端实现时 congestion 比较严重,你 hold 得住吗?

Final netlist release 前,你应该做好哪些工作?

深入浅出讲透 set_multicycle_path,从此彻底掌握它

数字后端实现时 congestion 比较严重,你 hold 得住吗?

时钟树综合(clock tree synthesis)基础篇

好了,今天的码字就到这里了,原创不容易,喜欢的可以帮忙转发和赞赏,你的转发和赞赏是我不断更新文章的动力。小编在此先谢过!与此同时,吾爱 IC 社区(52-ic.com)也正式上线了。吾爱 IC 社区(52-ic.com)是一个专业交流和分享数字 IC 设计与实现技术与经验的 IC 社区。如果大家在学习和工作中有碰到技术问题,欢迎在微信公众号给小编留言或者添加以下几种联系方式进行提问交流。

2308

2308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?